Преобразователь код-фаза

Иллюстрации

Показать всеРеферат

Союз Советски к

Социалистическик

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 7449?3 (6! ) Дополнительное к авт. свид-ву— (22) Заявлено 20.03.78 (21) 2592812/18-21 (ь) )м. Кл .

Н 03 К 13/20 с присоединением заявки №вЂ”

Гасударственный камнтет (23) Приоритет—

Опубликовано 30 06.80. Бюллетень № 24

Дата опубликования описания 03.07.80 ла делам нзобретеннй н откоытнй (53) УДК-681.325 (088.8) (72) Авторы изобретения

А, М. Столяров и В. И. Лобанов (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ КОД-ФАЗА

Предлагаемое изобретение относится к ,области импульсной техники и может быть использовано в автоматике, измерительных и вычиспительных системах.

Известно устройство формирования сигнала с дискретно измеряемой фазой, cogep- жащее генератор, К -разрядный. общий geamens, пешифраторы с подключенным к ним блоком управления, узлы уточнения, формирователи и преобразователи сигнала, 1О и ячеек, кажпая из которых содержит поспедовательно включенные узлы уточнения, формирователь и преобразователь фо мируемого сигнала, причем между входом узла уточнения каждой из ячеек и обшим

15 делителем включен свой отдельный дешифратор, ко всем преобразователям ячеек подключен выхоп формирователя= гетеродинного напряжения, входы которого подключены к запакхпему генератору и выходу обшего делителя (1)

Схема данного устройства реализуется с использованием большого количества цифровых комбинационных, и анапоговых блоков, требует высокой частоты генератора и имеет сложную настройку, что приводит к увеличению габаритов и снижению падеж ности выполняемых на ее основе приборов.

Известно также цифровое устройство для воспроизведения фазовых сдвигов, содержашее запаюший генератор, связанный с делителем частоты, выходы которого соединены с одними входами блока сравнения, другие входы которого подключены к выходам блока установки кода фазового сдвига, счетный триггер, фильтры, схемы совпадения, схемы однозначности и неоднозначнооти и триггер с раздельным управлением, причем выход счетного триггера соединен с первыми входаьти схем однозначности и неоднозначности, вторые входы которых подключены к выходу старшего разряда блока установки кода фазового;сдвига, а выходы схем однозначности и неоднозначности соединены с одними вхопами схем совпадений, другие входы которых подключены к вьпсоду блока сравнения, а выходы схем совпа.— цения соединены с соответствующими входами триггера с раздельным управлением 2

К недостаткам текат о преобразователя код-фаза следует отнести высокую тактоВую частоту задающего генераторе, опрецепяемую соотношением 5г = т ьье >

К гце 9 - частота выходных сигнедов устройства.

Требование высокой тактовой частоты

10 заставляет применять умножение при ограничении, утки тактовых частот, затрудняетт йрименение доступной ацементной базы, усложняет устройство.

Целью предпагеемогО изОбретения явля15 ется уменьшение частоты зацающего генератора без изменения дискретности преобрезов ения.

Поставпеннея цепь достигается за счет того, что в преобразователь код-фаза, сс 20 держащий задающий ге нератор, связанный с делителем частоты, апемент И, выход которого соединен с одним входом тактируемого триггера введены К -разрядный и (К -1)-Разрядный сУмматоРы, при oM 25 делитель частоты выпопнен (К -1)-разрядным, а его выходы соединены с первой группой входов старших разрядов К-разрядного сумматора, вторая группа входов которого и младший разряд первой группы подкпючены к K-разрядному входному коду, и с первой группой входов (К -1)-разрядного сумматора, вторая группа входов которого соединена со старшими разрядами

K -разрядного входного кода, а выходы старших разряцов сумматоров подключены к входом алемента И, выход которото соединен с управляющим входом тактируе- мого триггера.

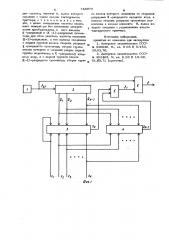

На фиг. 1; структурная алектриче40 скея схема у> гройства; на фиг. 2 приведены временные диаграммы, поясняющие работу устройства дпя случая разряднооФи K-4 и входного коцо Х-6.

Преобразов атель содержит задающий генератор 1, (К -1)-разрядный делитель частоты 2,К -разряцный сумматор 3, (К-1)-разряЪный сумматор 4, алемент

И 5 и.тектируемый триггер 6.

Сигнал, с задающего генератора по

50 ступает на тектовый вход тригтера 6 и на (К -1)-разрядный депитепь час;готы 2, Все Выходы Qg> Qg > ° ° Я1(,1 которого соединены с первой группой входов старших разрядов К»разрядного сумматора 3.

Вторая группа входов сумматора 3 и младший разряд первой группы соединены с К -разрядным двоичным входным кодом

Х =(X X< ...Х ). Кроме того, выходы

73

4 делителя частоты соединены с первой группой входов (т, -1 )-разрядного сумматора 4, вторея группа входов которого соединена со старшими разрядами >,-разрядного входного кода )(. Сигналы У>к с выхода старшего разряда сумматора 3 и с выхоца старшего разряда сумматора 4 пацаны на входы алемента И 5, Выход которого Ф соединен с управляющим входом тактируемого триггера.

Вых дные сигналы (и Zg MM а торов 3и4 и сигнал 1<, с выхода схемы

И 5 появляются с некоторым присущим цифровым блоком нестабильным запаздыванием по отношению к тактам >ч задающего генератора, что могло бы внести фаэовую ошибку и преобразование код-фаза при ис подьзовении сигнала >>„в качестве выходного, Привязка сигнала к тактом осуществляется но выходе токтируемого триггера 6. Именно сигнал > (>, без учета нестабильности ) и сигнвч 9 но выходе старшего (К -1)-го разряда делителя частоты и являются выхолными сигналамипреобразоватепя частотой 4>,, . Очек-

P>by, Из фиг. 2 видно, как образуются сдвиги переднего П> и заднего п2 фронтов относительно Q3 при К =4 и Х =6. Здесь

5 величины ц=2.y g,.g y=g т 2

2 з

z,=2 Y.z; 2 i,g-. i )(. z

>-1 3> где 9;, Y;,еф;еЬI3, явля>отся десятичным аквивачентным препставлением двоичных кодов соответственно на одном иэ входов четырехроэрядного сумматора, на выходе 4-разрядного сумматора, на выходе трехрозрядного сумматора и на входе преобразователя.

Приращение входного кола р, на единицу вызывает изменение лишь одного иэ. фронтов сигнала т или fq на величину

360 /2 пля К 4 или 360 /2" в общем случае. Поскольку сдвиг по фазе между первыми гармониками меондро (3т> и сигнала или -т определится полусуммой сдвигов переднего и зочнего фронтов, цена мпацшего разряда составит 360 /2, что о к позвопяет при достижении прежней пены младшего разряда 360 /2 вдвое снизить тактовую частоту задающего генератора без изменения дискретности преобразования.

Формупаиэоб рете ния

Преобразов атель код-фаза, содержащий зецакютий генератор, связанный с депяте744 лед частоты, элемент И, выход которого соединен с одним входом тактируемого триггера, о т л и ч а ю ш и и с я тем, что, с целью уменьшения частоты задающего генерат,>ра без изменения дискретности преобразования, в него введены

К -разрядный и (K -1)-разрядный сумматоры при этом делитель частоты выполнен (g-1 -разрядным, а его выходы соединены с первой группой входов старших разрядов

g -разрядного сумматора, вторая группа входов которого и младший разряд первой группы подключены к K -разрядному входному коду, и с первой группой входов ф-1)-разрядного сумматора, вторая групе73

6 па входов которого соединена со старшими разрядами и -pmpagnovo входного кода, а выходы старших разрядов сумматора подключены к входам элемента И, выход которого соединен с управляющим входом тактируемого триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

hh 320036, М., кл. Н 03 К 5/153, 30.03. 70.

2. Авторское свидетельство СССР

М 362465, М, кл. Н 03 К 13/20, 01.03,71 (прототип).

Составитель Б. Войтов

Редактор Е. Караулова Техреду М, Петко Корректор С. Шекмар

Заказ 3682/15 Тираж 995 Подписное

БНИИПИ Государственного комитета СССР по делим изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4