Преобразователь частоты в код

Иллюстрации

Показать всеРеферат

Союз Советскин

Сощивлистическин

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

744977 (6! ) Дополнительное к авт. свил-ву (22) Заявлено 04 05.78 (21) 2613234/17-21 (5> 3> К>.

Н 03 К 13/20 с присоединением заявки,%

Гасударственный комитет (23) Приоритет (533 УДК 621.317. .76 (088.8) ао денни нэобретений и атнрытий

Опубликовано 30.06.80. Бюллетень №24

Дата опубликования описания 02 07.80 (72) Авторы изобретения

В. В. Клименко и В. А. Гаманко

Таганрогский радиотехнический институт им. В. Д, Калмыкова (7I ) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД

Изобретение относится к вычислительной технике и может быть использовано для связи вычислительной машины с внешними устройствами и объектами.

Известны преобразователи двоичного ко да в частоту, содержащие информационный 5 регистр, комбинационный сумматор и регистр суммы (1) .

Недостатком известного устройства является то, что он не производит обратного преобразования.

Известен также многоканальный очи чик импульсов, содержащий N информационных регистров, регистр суммы с комбинационным сумматором на входе 121.

t5

Недостатком этого преобразователя является то, что он не учитывает знак преобразуемой величины и не позволяет производить обратное преобразование, что приводит к тому, что вычислительные машины

Ы комплектуются большим количеством раЭнс> тинных преобразователей.

Целью изобретения является расширение функциональных воэможностей.

Поставленная цель достигается тем, что в преобразователь содержащий распределитель импульсов, первый и второй выходы которого соединены с первыми входами первого и второго коммутаторов соответственно, ко вторым входам которых подключен выход регистра суммы, выход первого коммутатора через последовательно соединенные первый информационный регистр и третий коммутатор подключены к первому входу комбинационного сумматора, выход второго коммутатора через последовательно соединенные второй информационный регистр и четвертый коммутатор п отключены ко второму входу комбинационного сумматора, выход которого соединен со входам регистра суммы, третий и чу вертый выходы распределителя импульсов подключены к управляющим входам третьего и четвертого коммутаторов введены триггеры режима и знака, четыре синхронизатора, коммутатор записи, два ключа, два элемента ИЛИ и инвертор, причем управляк щие входы первого и второго синхронизаторов соединены с пятым Выходом распределителя импульсов, шестой выход которого подк}почен к. управ!?(по}цим Входам третье=-го и четвертого синхронизаторов, выходы псрвого и третьего с?п?хро(??(заторов через пе1звый элемент ИЛИ подключены к третье=му ВхОду кОм бинационцОГО суммQYopQ! K четвертому входу которого чеоез второй элемент ИЛИ подключены выходы второго и четвертого синхронизаторов, Выход ком= мутатора записи соединен с управляющим . Входом информа?(??0?п?ого регистра и входом тр?(г(гepQ знака, Выходы KOTopo? o ?IОП3 Ho!??(« цы к первым входам клю ?ей, вторые }зходы

?»ОТОРЫХ СОЕ}ЗЗ}ЛРПЫ С СЕДЬМЬП;! ВЫХОДО;.; 0 }С .,1:, пределите}?я импульсов, к ??ервому входу

КОТОРОГО ПОДК?ПОЧЕ?} ПРЯМОЙ ВЫХОД ТРИГ?«Е»

pQ pe MHMA, БылО д 13азря ? в не?зеп Олнец ия реГист13а c) ммы подкл?Оче?(чсрсз HHI3epтор и третьему входу первого ключа и цепо- 3(j средственно = к третьему входу Вторсго

Eл?0 ? а.

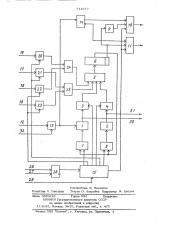

Ца ц?ертежe приве«дена блок ch(ема цреоб?зазователя -?астоты в код, Осу(цест?зля?ошеГО двух?(а}?а(?ье(Ое ?(?зеобрэзова(?}}е 3= частоты B КОд и Одцокае?альнО(. Ifpe06?}азО-Вац цe КО ?е-«ча cтота, 1 ре бразова (е(??. co(topi!(I(T;III(!tjop;;}Qitпоц цые рег??стры 1, 2 B(jxo(!J)j которых соедз«вЂ” н(Н!» Черсз е Омму(гат01зы 3 -г со BI(одам?? „o

?(Омб?}е?ац??оце?ого сумматора 5. Вь?хо(гя ком:6?(ц 31}е(0????ОГО с»ч.ллQTopQ соед?(це(?ы с pe«:

ГистВОм (3 с Уммы. Выходы 1зэгц стра суе! м},! через ?(Ое}м утаторы 7. 8 Jjo(t((JII0!1(!I?LJ к е}хода?и информационных регистров, Q раз- -,-, ряд пе13еполцения реГистра суммы пс д((л(с=чеп через цнвертор 9 к кл?очу 10 и к клю= чу 1 1 непосредственно. Преобразуемый дополцительпь?й код по ши?е 12 через ком-мутатор записи 13 поступает в информа-= ционный Регистр 1 а знаковый разряд Б триггер 14 знака. Прямой и инверсный и(= ходи? триггера знака соединень! со Входами

?(л?очей, третьи входы которых соедчнець? с с первыми входами кшочей, Вторые }=.3(од}:? d5 которых соедпнены с распределителем импульсов 15. С выходов ключей снимается сигнал, частота которого пропорциона ьца входному коду. Преобразуемая частота по шипам 16 — 18 поступает на cHKrpoK!Heà-;(? тсры 20 - 23 Bxo(IIION ?QOYGTI!1, BRD(opbj. которых через элементы ИЛИ 24, 25 под-кзпочецы ко входам комбинационного суммато1за. По шинам 26 и 27 поступают c?i?= наль?, устанавл??Ба(О?цие режим работь(г(рс- 5 образователя. Выход триггера режима 28 соединен с распределителем импульсов, который управляет работой схемь! от с??ил=

)77 ф роцизнрующкк импульсов. носTy ?QIO!HHJ(по

}ц}п?е 29. Выходы расп130}ю(}цте}ц(tfh}пу?(е

СОВ сое?л(?(ен!»! со Входами сццхро(???заторов

В?(ОДЕ?О}1 i) ас ТО ты С КОММ TQTopQh! H и С Вьt-. Оццымц клю fohf!t. Ко}? ч}}сел соответс«В«:

-3;J0UIHx f!3(0BIjt,jI»(часто.-ам, снимается с: и???(30 и 31 „Импульс записи (?(3 nj!!Ile 31

"}л?равляе г занесением !ю?}о(шите(?нного кс :.« да В ??(?форыа1(?(оццый 130Гистр 1 .

Усту.о}10 гво рабо}ает следу?0(пим обраЗОМ.

П1зеобразователь Ос„ц?естВляет дВухка= (=QJ}I»IH:jc пре061за зова(?ПЯ с}асто (?ь! в код ц одноканальное преобразо}за(?е(е кода в (ас

° (0«г, (1ля,стацовкц пзeo6ðoço QToля в pe:= . (} } h 0» «1(Ос(()(а !?Q B(Ц(Е?)! ?ЦЬ!И ВХОД ТРЕП

Гера резким-.} 28 подается упра?иь?юший цм/

j (! JJj B 2 0 . .r вых«ода трцГ? BpQ режима i?Q

Вхо}-. pQcr!pеделителя ??мг(у((ьсов 15 подае ся еды?ичный по.геещцал, которь(й обеспеч?(хазе т Вь} дачу сООТ}зете тв ЛОщих ущза вля?0 щцх им??ульсОВ, которы(з пОст" пьцот в этом рззкцме ца (}уоду ?(Ом„»(утатОРОВ 3, 4 и EGM« (:}ута «OpQ ы: 1(реобразуе. .(ы}} дс??О litl(TBJ(I— етый кa;. Но шине 12 г(р??ход?(т Hа вход ком;.»! i TQTopQ Записи 1 ПО импульсу 3,, pQB —,;;t!QI0jJtB.;»(у запцсь кода B преобразоьатель„

Ос у; де ствгя ется запись информ }щиОцць?х раз?зядсв кода B jtíôîðMQöl}oíít jj1 регистр 1, а з?(ак (Од з;}г цсывается в тр?(ггер знака

I :1. И;.(??ульсы с распредегп(теля имцуле гlo 1 5 )tO!t!?ПОТСИ IQ Входы КОМ; у тато} ° ОВ .3, 1 ц Осуц}ествлиется с л;(м?(ро}за ?ие КОДОВ

}(з ?ц?ц)0,зма}(}»О(и(? (х 1}БГистрОВ 1, 2 В кОмбццацпоццо(,; сумматоре 5, Q результат Но"ступает B регистр су (мы 6. Затем подаютсН Äp

ax0Jlj.j к?по jet 10 11. В результате В информационный регпсто 1 перезаписывается сумма, а зца !e!lite разряда переполце(п?я

pe? Itc. тра суммы 6 выдается ца клкзчи 10, 1 1 и В заВцсцмости 0Т состОяния т13игг ра знака 14 ф01змируется выходной импульс

Такое циклическое суммирование осущестВляется ца всем интервале преобразования,,}13?я уста??овкц преобразователя В режим (астота-код па нулевой вход триггера режима 28 подается управляющий импульс

27. С .выхода триггера режима 28 на Вход распределителя импульсов 15 подается ?? = левой поте«ещца«л, при этом управля."ошие им==

fi ульсы с распределителя импульсов пс

Ст„ë.òQ!ÎT IIQ Входы KOMM;y(QTOpOB 7, 8 и

3, 4, Импульсы пОложи ГельцОГО IlpllpQI(te ! IfiH l!? ПЕРВ(}? 0 Ка?(ала ПОСТУПа?ОТ Па СИЦХ

p0HHBQT0p ?}ХО}з??ОЙ часT(JTI j 20 H Ito равля?ощему импульсу с распределителя ю(??у?(ьсов 15 через элемент ИЛИ 24 ??О=

S 7 4- 1 ступают на вход младшего разряда комбинационного сумматора 5. Импульсы отрицательного приращения поступают на синхронизатор входной частоты 21 и по управляющему импульсу с распределителя

5 импульсов 15 через элемент ИЛИ 25 поступают на все разряды комбинационного сумматора 5, т.е, осуществляется прибавление дополнительного кода отрицатечьной единицы. Одновременно с импульсом приращения (положительным или . отрицательным) по управляющему сигналу с распределителя импульсов 15 из регистра 1 через коммутатор 3 на комбинационный сумматор 5 поступаеч предыдущее значение кода и результат записывается в регистр суммы 6. Из регистра суммы по приходу импульса из распределителя импульсов 15 на коммутатор 3 результат переписываеч ся в левый информационный регистр 1. За- 20 тем импульс с распределителя импульсов

15 поступает на синхронизаторы входной частоты 22 и 23. Импульсы положительного приращения для второго канала поступают на синхронизатор входной частоты 22 через элемент ИЛИ 24 на вход младшего разряда комбинационного сумматора 5. Импульсы отрицательного приращения второго канала поступают на вход синхронизатора входной частоты 23 и по 30 управляющему импульсу с распределителя импульсов 15 через элемент ИЛИ 26 поступают на все разряды кол бинационного сумматора, т.е. осуществляется прибавление дополнительного кода отрицатель- 5 ной единьщы. Одновременно с импульсом приращения через коммутатор 4 из информационного регистра 2 на комбинационный сумматор 5 поступает предыдущее значение кода и результат попадает в регистр уО суммы 6. Из регистра суммы 6 при приходе импульса из распределителя импульсов 15 на вход коммутатора 8 результат переписывается в информационный регистр 2.

Опрос обоих каналов циклически повторяется. Информационные регистры 1 и 2 обнуляются при считывании из ННх двоичного кода по шинам 30 и 31.

Реализация функций двухканального so счетчика импульсов и преобразователя кода в частоту, работающего по принципу циклического суммирования преобразуемого кода, на одном и том же оборудовании позволяет уменьшить аппаратурные за- Ы траты. Использование в преобразователе дополнительного двоичного кода исключает необходимость машинного преобразовация прямого кода в дополнительный и nñ полпптельного еодя р- прямой.

Формула изобр етония

Преобразователь частоты в код, содержатций распределитель импульсов, первый и второй выходы которого соединень с первыми входами первого и второго коммутаторов соответственно, ко вторым входам которых подключен выход регистра суммы, выход пер ваго коммутатора через последовательно соединенные первый информационный регистр и третий коммутатор подключены к первому входу колтбинацпо плго сумматора, выход второго коммутатора через последовательно соединенные второй информационный регистр и четвертый коммутатор подключены ко второму входу комбинационного сумматора, выход которого соединен со входом регистра суммы, третий и четвертый выходом распределителя импульсов nonzInoчены к управляв> шим входам третьего и четвертого коммутаторов, о т л и ч а ю ш и и с я тем, что, с целью расширения функциональ.ных возможностей в него введены триггеры режима и знака, четыре синхронизатсьра, коммутатор записи, два ключа, два элемента ИЛИ и цпвертор, причем управляющие входы первого и второго синхронизаторов соединены с пятым выходом ðañпределителя импульсов, шестой выход которого подключен к управляющим входам третьего и четвертого синхронизаторов, выходы первого и третьего синхронизаторов через пергый элемент ИЛИ подключены к третьему входу комбинационного сумматсра, к четвертому I oäó которого через второй элемент ИЛИ подкгцочены выходы второго и четвертого синхронизаторов, выход комл утатсга записи соединен с vnL равляюшим входол1 информационного регистра и входом триггера знака, выходы которого подключены к первым входам ключей, вторые входы которых соединены с седьмым выходом распределителя импульсов, к первому входу которого подключен прямой выход три гера режима, выход разряда пер полнения регистра суммы поп ключен через инвертор к третьему входу первого кхпоча и непосредственно к третьему входу второго, ключа.

Источники информации, принятые во внимание при экспертизе.

1. Данчеев Б. П. Е!ифро-частотные вычислительньге ус тройства. М., Энергия

1976.

2. Лвторское свидетельство СССР

N . 422105, кл. Н 03 Е 23/00, 1972.

744977

Составитель Е. Мосолков

Редактор JI. Гольдина Техред О. Андрейко Корректор М. нигула

Закж 3683/16 Тираж 995 По шисное

ПНИИЛИ Государственного комитета СССР по делам изобретений и отжрытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4