Устройство для деления частоты импульсов с дробным коэффициентом деления

Иллюстрации

Показать всеРеферат

Соизз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii) jggQQ() (6! ) Дополнительное к авт. свил-ву № 621 101 (22) Заявлено 11.01.78 (2I ) 2568878/18-21 (51)М. т(Л.

Н 03 К 23/ОО с присоединением заявки.%

Государственный комитет

СССР (23) Приоритет до делам изобретений и открытий (53) УДК 621. . 37 4.4 (088. 8) Опубликовано 30.06.80. Бюллетень №24

Дата опубликования описания 03.07.80 (72) Автор изобретения.В. И. Иванов (7I) Заявитель (54) УСТРСЙСТВО ДЛЯ ДЕЛЕНИЯ ЧАСТОТЫ ИМПУЛЬСОВ

С ДРОБНЫМ КОЭффИБИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к импульсной технике и может использоваться в частотноперобразующих узлах аппаратуры времени и эталонных частот, электронных часов, измерительных прибо5 ров, в устройствах синхронизации систем передачи данных, преимущественно при наиболее высоких требованиях к стабильности фазы выходных импульсов.

По осноитому авт. св. № 621101 известно устройство для деления частотыимпульсов с дробным коэффициентом деления, содержащее делитель частоты с переменным коэффициентом деления, установочные входы которого подключены к шине ввода кода целой части коэффициента деления, а выход — к входу считывания элемента сравнения кодов, первый выход которого подключен к входу считывания первого сумматора и ко входу установки нуля второго сумматора, второй выход- ко входу установки нуля первого сумматора, ко входу считывания сумматора и ко входу делителя делителя частоты,с переменным коэффициентом деления, счетный вход которого соединен с входной шиной, выход первого сумматора подключен к первому входу элемента сравнения кодов и к первому информационному входу второго сумматора, а вторые информационные входы первого и второго сумматоров подключены к шинам ввода соответственно кода числителя дробного коэффициента деления и кода разности знаменателя и числителя дробного коэффициента деления (1).

Недостатком описанного устройства является вызываемая дискретностью

:шкалы текущего времени модуляции фазы выходных импульсов.

Целью дополнительного изобретения является повышение стабильности фазы выходных импульсов при одновременном снижении требований к быстродействию устройства.

С этой целью в устройство для деления частоты импульсов с дробным коэффициентом деления, содержащее делитель частоты с переменным коэффициентом деления, установочные входы которого подключены к шине ввода кода целой части коэффициента деления, а выход ко входу считывания элемента сравнения кодов, первый выход которого подключен ко входу считывания первого сумматора и ко входу установки нуля }зторого сумма= тора, второй выход - ко входу установки нуля первого сумматора, ко входу считывания второго сумматора и ко входу делителя частоты с переменным коэффициентом деления, счетный вход которого соединен с входной шиной, выход первого сумматора подключен к первому входу элемента сравнения кодов и к первому информационному входу второго сумматора, а вторые информационные входы первого и второго сумматоров подключены к ц111пам ввода соответственно кода числителя дробного коэффициента деления и кода разности знаменателя и числителя дробного коэффициента деления, ввс.ден блок квантованцой задержки, подкпк}= че}псый к выходу делителя частоты с переменным коэффициентом депс.ния, причем Bxog BIUIIo÷eIIII}I блока к1«антовац110й за-держки соединен с его выходом, В пь»рвый

И ВтОРС}й УСтВЦОВОЧНЫЕ ВХОДЫ СОЕД1111ВНЬ1 соот}3етственпо с выходами первого и втсрого сумматоров.

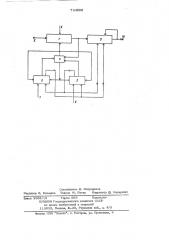

На чертеже изображена структурная электр}}ческая схема устро}ссства.

Оно содержит делитель 1 частоты с переменным коэффициентом деления,, сумматоры 2 и З, элемент 4 сравнения кодов, входную шину 5, IIIIIIly 6 ввода кода целой части коэффициента деле}п111, шину 7 ввода кода числителя дробнсго коэффипиента деления, шину 8 13вода кода разности знаменателя и числителя дробного коэффициента деления, блок квантованной задержки 9, выходную тт}И11у 1с-т.

Делитель 1 частоты имеет вход переключателя коэффициента деления на единицу, соединен}сый с входом установки нуля сумматора 2, входом считывания сумматора.З н первь}м выходом элемента

4 сравнения, вход подачи импульсов, -:oåдииенный с входной 1циной,3 Il Bxog ввода целой части дробного коэЦ}1циента деления, соединенный с шиной 6.

1-}ТОрой ВЫХОД ЭЛЕМЕНТС1 Сра}ЗНЕцря,ф соединен с вхОдом считывания сумматора

2 и входом установки нуля суммВторВ 3»

ЩЩЦД 7 И 8 ОЛу3КВТ Лпя ПСтдачи СОСу1»ВЕ1т -;T-"

BeImo кода Ч11слнтеля дробного 1соэс}}фн»» циента деления и кода разнос;.ти зпаменатеЛЯ И Чпт ЛИТЕЛ}т H8 OgIII|I От»тНОИМЕЦПЬ1Е BXO ды сумматоров 2 и, З.,Другие одно= именные входы этих сумматоров объединены каждый с Одним установочным входом блока 9 квантован}1ой задержки и подключены к стробируемому выходу другого сумматора. Потенциальные выходы сумматоро}з 2 и 3 соединены с соответствуюцпсми информационными входами элемента сравнения 4.

Информационный вход блока 9 квантованной задер}кки соединен с выходом делителя 1 и входом считыватяия элемента 4 сравнения, а выход — с выходом вкл10чения з 1 ОГО блока H «ыходной шиной 1 О. В сумм Втор 2 с }Н1т}}.ы 7 заносятся со зна}сом + В в суммаТОР 3 C I*,IImi »-I С3 - 1СОДЬт СО Зтт1ЭтСОМ

Из сумматорс;в 2И3 в элементе сравнения

4 КОДЫ Пртцп1Маптоя бЕЗ ЗНВКВ. СумматОрами. 2 3 из д}}тт.гогт3 су}иматорат а также

Опо}сом 9 кваптованной задержки из сумматоров 2, .3 копь} принимаются са знаком. Ьпоком 9 квацтованной задержки реализуется задержка, раиная алг браи«1 С КО}} т ч«111Е }СОт»т-т-l.,Ь1 II тСт3, НВ

-«ЭСТВПОВО«1НЬ}Х Кетсак ВЗ.I>O O С ПРОт1

:«Стттот1С««гтСЬ1«,С ЗнатСО«1 j QIIC.— j3 3В }т:». бт— котс}ттд> Д}1«1 рэа}1 тЗВц}т1т З:тдэ}3 1СЕ}Р—.О ЗтСтт

» -В«я» "+ « тт " - Длс«} leттт"- }»ра1-.,1тэттнч г1

ГДЕ,,; — тИСПВ„}1С?П}ЧBННЫЕ СООГФ

ВЕТ .г}3т ННО В СУММВТт3т3тах,".. И .3.

}-}а пэрвом B! !xoge: 3}э ..энта С}3ВВНЕ

НИЯ )- ЩЩ Стснт1-.1ВВ}тн11 ти»т НВП Ile ПОЯВЛЯЕТс.я, если. у1сазЭВ}псое vcповие выпсспняе3у я, и пОянпяется B Остал1 ных спучая3 1}В втсром выходе элемента сравнения 4 при

Ссянт ЫВВН11П -ИГттал НМЕЕГ И1}ВЕpC}loe Зна

ЧЕНЯЕ ПО С}}ВВ11ОП1.1КЭ С )}ЕРВт.тМ В1,1«СОДО1«Ь

Гст»B j g I Q j 7, (т- т Эт « „тс*}т:ГВ С РЭВ» понт}я 1}В де«} .}1тс}пь .1 oil l цщ1 1}е поступает. В результате делитель 1 срабаты1 ВОI С кт e!I«ô}1ц1 ен1 Ом ge}1еп}итт А в про lÒ}ß1IOМ Cl1УЧВе К(ЪЭффПЦИЕН1 Дэi Ie}IЧЯ «тста нс1в}1}1вается p}B»HI«IM (Л + 1 ) т Где А — цеПС}Я ЧВСТЬ ДРООНО1 О Кт3Э }тф}}«птйэт}тт3т ДЮ1

Щ}Я, т т313ТВЕ"т С1 ВЕП}то OiIOP»Е/3ЦОЙ ВЫХ(:тдЦОй

11мпульс сдвиГается пс} ьре};1етш в сторону

СтТСТВВВ1}ШЯ Нпн ОПЕ}3Ежа}Ш}1!, ТВК 1СВК

1 Д К Л + Ъ ДС}ОС311Ы}1 1СОЭтт«т}}1} тсиг-Цт т3,. }3 дт,-п ттня"

СС }3 ЧИСЧИТЕЛЬ 11 ЗНВМЕКВ—

" ет ° <-ГО дробной части;

;Вт ТтОС}»а С3}1ГПВЛ т1а В „O

lie 3 Уст}ЗОЙства. получим т- (.-р(+) а

Бслп первое срабатывание произошло с коэффициентом деления (А+1), товыходной импульс сдвигается в сторону опережения на величину:

ЬТ(+) = — = (2)

k А Я

Если первОе cpa6GTI,IBGKEe произошло с коэффициентОм деления (А+1 ) р ГО выхОд ной импульс сдвигается в сторону отставания HG величину(а а -) =(А .М Е „- — = — <д) (у -а.)

Ь

5T(=((ь-d) =(; (5>

Величину ГО, имеющую размерность времени, назовем квантом временной задержки. Если делитель 1 сработал с коэффициентом деления А, -то на его выходе имцульс имеет опережение на с(, квантов, в противном случае наблюдается OTCTGBBHHe HG (p3 — (К ) Квантов

Злемент сравнения 4 выбирает .Наименьшее из чисел 7.. -+c(.;, =-(р-ф

o6pGG/0ìûõ В сумматорах соответственно

2 и 3, и jjГстанаВливает требуемый кОэффициент дсления делителя 1 при поступ-. лении на его вход считывания очередного импульса с выхода делителя 1.

Одновременно по сигналу с первого или 35 второго выходов элемента сравнения 4 происходит перепись числа 2. из сумматора 3 в сумматор 2 и в блок задержки 9,. если условие ЦЯ Е ) выпохшяется

Ф или из сумматора 2 в сумматор 3 и в @ блок задержки 9, если это условие не выполняется Для компенсации Времен ных сдвигов в блок задержки 9 из сумматоров 2 и 3 числа передаются с обратным знаком.

Требуемая задержка в блоке задержки

9 включается каждый раз цри поступлении на выход 10 очередного импульса. С установленной задержкой будет вьщан на выход 10 очередной импульс. Для реализации опережения и Отставания (двусторонней задержки ) блок задержки

9 имеет исходную задержку, от которой вОзможно наиООльшее Отклонение на

Д

Е ;д» = + квантОВ B процессе работы устройства, где P — знаменатель

Я дрОбнОй ч Ястн еоэ ффиццента деления устройства.

Требуемое значение кванта задержки блока квантовой задержки 9 зависит

or параметров устройства и вычисляеъся по формуле (4). Например, для типичного случая, когда требуется реализовать коэффьщиент деления, задаваемый в виде десятичной дроби прп его перестройке с. шагом ЬK = 0,01 (т.е. f5 = 100) и

Ev„y, = 5 МГц., нз (4) подучим значение кванта задержки: ГО = 2 нс. В этом случае блок квантованнои задержки Ф должен иметь задерживающие секции с задержками 2, 4, 8, 16; 32 и 64 нс, которые можно реализовать, например, на цепочках микросхем. В результате применения блока 9 квантованной задержки методическая погрешность устройства деления оказывается полностью компенсированной, а результирующая стабиль ность фазы выходных импульсов зависит только От стабильности задержки этого блока.

Фор мула изобретения

Устройство для деления частоты импульсов с дробным коэффициентом деления поавт. Св. ¹621101, Отлич Qю щ е е - я тем, что, с целью повышения стабильности фазы выходных импульсов при одновременном сниженхш требований к быстродействию устройства, в него введен блок квантованной задержки, подключенный к выходу делителя частоты с переменным коэффициентом деления, при ем вход включения блока квантованной задержки соединен с его выходом, а первый и второй установочные входы соединены соответственно с выходами. первого и второго сумматоров.

Ксточшп:и информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 621101, кл. Н 05 К 23/00, 2 1.02.77.

Составитель О. Митрофанов

Редактор П. Галанина Texpell М. Петко Корректор Ю. Макаренко

Заказ 3653116 . Тиран 995 Поднионое

Ш-1ИИПИ Государственного комитета СССР по делам иеобретеппй п открытий

113035, Москва, Ж-З5, Раушская наб., д. 4/5

Филиал ППП Патент, г. У>игорек, ул. Проектная. 4