Селекторный канал

Иллюстрации

Показать всеРеферат

Дата опубликования описания Q7 Q 7 8Q

681 ° 14 (088 ° 8) (71) Заявитель (54) СЕЛЕКТОРНЫИ KAHAJI которая содержит блок связи с центральным процессором, блок состояния канала, блок связи с внешними устройствами, блок прерывания.

Недостатком ее является наличие буферной памяти и значительного канального оборудования для выборки и хранения команд ввода-вывода, ког-. да управляющая программа обращается к занятому блок-мультиплексному каналу, так как программе не сообщается о состоянии канала, Цель изобретения - повышение производительности канала при работе в блок-мультиплексном режиме, Предлагаемое изобретение относится к вычислительной технике, может быть использовано в электронно-вычислительных машинах для обмена информацией между быстродействующими внешними устройствами и оперативной памятью. Оно также находит применение в системах вычислительных машин, состоящих из нескольких ЭВМ и множества быстродействующих внешних устройств.

Известен селекторный канал (1), содержащий блок сопряжения канала с вычислительным устройством, блок сопряжения канала с памятью, блок сопряжения канала с внешними устройствами, служащими для обмена данными между быстродействующими внешними устройствами и оперативной памятью, 20

Этот канал не обеспечивает воэможности прекращения многократных обращений управляющей программ к занятому каналу, вследствие чего значительное время центрального процессора теряется для продуктивной рабоTbT

Наиболее близкой к данному изобретению по технической сущности яв— ляется система обработки данных 2), 30

Поставленная цель достигается тем, что устройство содержит первый, второй, третий, четвертый элементы И, первый, второй элементы ИЛИ, первый, второй элементы НЕ, схему сравнения, триггер, обращения, память для хранения подканалов, первый, второй входы и выход которой соединены соответственно с первым выходом блока хранения состояния канала, выходом первого элемента ИЛИ и входом первого элемента НЕ, выход которого соединен со входом триггера обращения, выход которого соединен с первым входом пер(72) Авторы изобретения В. M. Пронин, JI. H. Иэвозчикова, В. A. Воронцов и M.П, Орлова

746486 элемент а И, второй вход и выход которого соединены соответственна со вторым выходам блока хранения состояния канала, со вторым входом блока прерыв ани я и первым в ходом в т apo r o элемента И, второй, третий вход и выход которого соединены сооТаеТсТвенка с третьим и четвертым выходами и с первым входом блока хранения состояния канала, первый, пятый, шесТОЙ, седьмОЙ, ВОсьмОЙ ВыхОды КОТОРОго соединен соответственно с первым и вторым входами схемы сравнения,первым и вторым Входами третьего элемента И, первым входом четвертого элемента И, второй вход и выход которого соединены соответственно с Выходом схемы сравнения и со вторым входом второго элемента ИЛИ, выход которого соединен со вторым входом блока хранения состояния канала; при этом первый и второй входы первого элемента

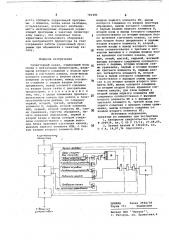

ИЛИ соединены сооветствекно с выхо- дом второго элемента НЕ и с выходом третьего элемента И, третий вход котого соединен с выходам схемы сравнения, выход которой соединен со входом второго элемента НЕ, Схема селекторного канала изображена на чертеже, Селекторный канал содержит блок связи с центральным процессором 1, блок хранения состояния канала 2, блок связи с внешними QGTpoAOTBBMH

3;блок прерывания 4,элементы H 5-8, схему сравнения 9, элементы НЕ

10, 11, элементы ИЛЙ 12, 13, память для хранения падканалов 14, триггер обращения 15.

Селекторный канал обеспечивает.. возможность запуска быстродействующих внешних устройств для работы в блок-мультиплексном режиме, когда в канале могут одновременно работать несколько быстродействующих внешних ! устройств, причем лишь с одним из этих устройств происходит обмен данными, а все другие одновременно работающие устройства действуют автономно, т,е. они работают без необходимости передачи данных.

Через блок связи с центральным процессором происходит передача команд ввода-вывода, данных и управля-, ющей информации, необходимой для работы с внешними устройствами, При получении из центральиoro процессора стартовой команды для запуска внешних устройств блок хранения состояния канала определяет, может ли канал выполнить команду, Если канал свободен, управляющей программе сооб-щается," что команда будет выполнена; стартовая команда через блок связи с внешними устройсвами передается ка внешнее устройство, которое начинает ее выполнять, По окончании передачи данных блок связи с внешними устройствайи через блок прерывания сообщает центральному процессору, что р бота с заданным внешним устройством ,закончена, При обращении управляющей программы к занятому каналу адрес стартовой.

5 команды и адрес работающего в данный момент в канал@ устройства сравниваются иа схеме сравнения 9, чтобы определить, принадлежат ли эти адреса одному падканалу. Если адреса не принадлежат одному падканалу, сигнал со схемы сравнения 9 через элемент

НЕ ll и элемент ИЛИ 12 совместно с pl 00M Стартовой КОМаНДЫ ПОСГУПааЕт в паамЯть Длл ХРакениЯ поДкакалав 14 5 для определения, занят ли зтст падканал в данный момент. Таким же образом, если при сравнении на схеме а сравнения 9 оказалась, что падканал сраькился, ка устройство неразделек2О кое и адреса не равны, та сигнал с элемента И 7 и элемента ИЛИ 12 совместно с адресом стартовой команды поступает ка дешифратор адреса для тения падкакала в память для хранения подкакалов 14, Если падканал свободен, сигнал из памяти для хранения подкакалав 14 через элемент НЕ

IO запоминает обращение на триггере

15, и„как только канал становится

Щ свободным, через элемент И 5 и блок прерывания 4 управляющей программе сообщается (через прерывание, в результате которого записывается слоВа состояния канала, Все поля кото35 рого равны нулю), что возможен запуск стартовой команды, Таким образом, отпадает необходимость в зацикливании обращений управляющей программы к занятому каналу. Если подканал занят или подканал один, а устройства разделенные, сигнал с элемен та ИЛИ 13 поступает в блок хранения состояния какала Z и через блок связи с центральным процессором 1 указывает управляющей программе, что стартовая команда не может быть выполнена, управляющая программа ке обращается к каналу да тех пор, пока через прерывание не будет указано, что обращение в.озможно; тем самым освобождается произв одителькае время процессора для выполнения других работ. Кроме того, при наличии сигнала Обращение возможно с элемента

И 5 при запрещенных прерываниях системы управляющая программа с помощью команды Пров ери ть к акал, поступающей на элемент И 6, может определить момент для нового запуска стартовой команды„

Селектарный канал,. работающий в блок-мультиплексном режиме, обеспечивает эффективную работу управляющей программы при обращениях к за65 нятаму каналу, так как имеет Возмож746486

Формула изобретения

Кценпъральноиу

npogeccopy

/(Etreuc un

ycmpoucmfa.

HccTü сообщить управляющей программе, о моменте, когда канал свободен, следовательно, исключает необходимое-ь многократных обращений управляющей программы к занятому селекторному канах,у, что позволяет более 5 эффективно использовать оборудование центрального процессора за счет сокращения работы управляющей программы прн обращениях к занятому каналу. !О

Селекторный канал, содержащий блок 1 связи с центальным процессором, входвыход которого соединен с блоком хранения и состояния канала, вход-выход которого соединен с блоком связи с внешними устройствами, выход которого с оедин ен с первым входом блока прерывания, выход которогЬ соединен со входом блока связи с центральным процессором, о т л н ч а ю шийся тем, что, с целью повышения производительности канала при работе в блокмультиплексном режиме, он содержит первый, в торой, третий, четв ертый элементы И, первый, второй элементы

ИЛИ, первый, второй элементы НЕ„ схему сравнения, триггер обращения, память хранения подканалов, первый и второй входы и выход которой соединены соответственно с первым выходом блока хранения состояния канала, выходом первого элемента ИЛИ, с первым входом второго элемента ИЛИ и входом первого элемента НЕ, выход которого соединен со входом триггера обращения, выход которого соединен с первым входом первого элемента И, второй вход и выход которого соединен соответственно со вторым выходом блока хранения состояния канала, со вторым входом блока прерывания и первьм входом второго элемента И, второй, третий входы и выход которого соединены соответственно с третьим и четвертым выходом и с первым входом блока хранения состояния канала, первый, пятый, щестой, седьмой, восьмой выходы которого соединены соответственно с первым, вторым входами схемы сравнения, первым и вторым входами третьего элемента К, первым входо ; четвертого элемента И, второй вход и выход которого соединены состветственно с выходом схемы сравне- ния и,со вторым входом второго элемента ИЛИ, выход которого соединен со вторым входом блока хранения состояния канала, при этом первый и второй входы первого элемента ИЛИ соединены соответственно с выходом второго элемента НЕ и с выходом третьего элемента И, третий вход которого соединен с выходом схемы сравнения, выход которого соединен со входом второго элемента НЕ, Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

Р 298934, кл, r. 06 F 15/16, 27 08,69, 2, Патент Англии Р 1442214, кл.

G 4 А, 14 ° 07 ° 76 (прототип), Филиал ППП Патент, r. Ужгород, ул. Проектная,4