Устройство для сопряжения

Иллюстрации

Показать всеРеферат

Ёмн

41у1 те. . .ь

Союэ Советских

Социалистических

Республик

О П ои746488

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б1) Дополнительное к авт. свид-ву— (22) Заявлено 271277 (21) 2561920/18-24 с присоединением заявки HP— (51}М. Kil 2

G 06 F 3/04

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет— !

Опубликовано 070780. Бюллетень Hо 25

Дата опубликования описания 07. 07,80 (53} УДК 681,327 °

gll (088,8) (72) Авторы изобретения

Д. И, Вигдоров и И„ П. Сколецкий (71) Заявитель Азербайджанский институт нефти и химии имени М. Азизбекова (54) УСТРОЯСТВО ДЛЯ СОПРЯЖЕНИЯ

Изобретение относится к области . вычислительной техники и может быть использовано для согласования скоростей обмена данными, Известны устройства для сопряже- 5 ния (lj содержащие память на сдвиговых регистрах, коммутаторы, распределители, регйстры, сумматор, с херы сравнения и узел управления и выполняющие функции согласования ско- 10 ростей передачи данных, Однако такие устройства сложны, кроме того, невозможно использовать в качестве запоминающих элементов стандартные интегральные модули па- )5 мяти, Наиболее близким к изобретению по технической сущности является .устройство для сопряжения $2j, содержащее память, кольцевой маркерный 29 регистр, соединенный выходами с соответствующими входами дешифратора, первая и вторая группа выходов которого подключены соответственно к первой и второй группам управляющих входов памяти, информационные входы и выходы которой являются соответствующими информационными входами и выходами устройства,и элемент И, соединенный входами с соответствующими 30

2 выходами первой группы дешифратора, а выходом — с первым управляющим выходом устройства, Недостаток этого устройства состоит в низком быстродействии из-эа того, что считывание очередного слова из памяти не может производится сразу по синхроимпульсу вывода, а только через некоторое время после поступления очередного импульса синхронизации, который тактирует запись, При этом скорость чтения информации не может быть выше частоты записи.

Кроме того, ограничение на тип запоминающих элементов, на которых может строится память, выражающееся в невозможности использовать стандартные дешевые интегральные элементы памяти с произвольной выборкой, сужает область применения устройства.

Целью изобретения является повышение быстродействия устройства, Поставленная цель достигается тем, что в предложенное устройство введены два счетчика, коммутаторы по числу адресных входов памяти и элемент ИЛИ, Выход каждого коммутатора подключен к соответствующему адресному входу памяти, первые и вторые входы комму-, 146488 . выхо таторов соединены соответственно с ющий вход сое не ый соединенный с выходом 17 выхо и дами первого и второго счетчиков переполнени 6

Р, ия счетчика 6, - для занеоды переполнения которых подключе- сения нул ны соответственно к первому и второ- 011 41f в нуля справа от границы в регистре 3, му управляющим входам кольцевого мар- Устройст о б ке н рного регистра, а входы — соответ- разом, ро ство работает следующим обственно.к первому и второму уп авляющим входам Уст ойства Вых ы

Р му у равляю- В исходном состоянии все разряды р . ыходы второй регистра 3 устанавливают в 0 за группы выходов дешиф ато а и д фратора подключе- исключением какого-либо одного. П и

Ф ны к соответств ю м у щи входам элемента этом комбинация подряд расположенод ого. Ри

ИЛИ, выход которого является вторым ных a регистре одной единицы и управляющим выходом устройства, Кроме двух нулей дешифрируется соответого, память содержит и элемеНтов HJIH тствующим трехвходовым элементом И поминаю и матрицу из и строк и К столбцов зя,— дешифратора 2 как сигнал подг готов ки õ М-разрядных элементов,:гф%- записи (например, на выходе 10, ) чем инфо формационные выход и вход запо в ячейки запоминающих модул и 1 оде З

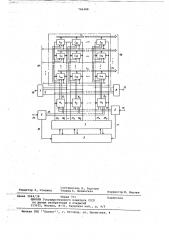

15 . з минающего элемента i-той строки (j,=I, ) 1 „ третьего столбца памяти 1. Этот подключены соответственно через 1-,й же сигнал подключает к адресным вхоэлемент ИЛИ к 1-му выходу и 1-мд- вхо« дам этих модулей выход счетчика 5, ду памяти, адресные, первый и второй Первое слово, поступающее по инвходы запоминающего элемента f-го формационному входу 19 и стробируестолбца (=1,К) подключены соответ- 20 мое синхроимпульсом записи по управственно к j-ым адресному и управляю- ляюшему входу 14, заносится в первую щим входам из первой и второй группы ячейку выбранных модулей, Переключаеуправляющих входов памяти, мый этим же синхроноимпульсом в сле На чертеже представлена структур- дующее состояние счетчик 5 подготавная схема устройства, 25 ливает занесени а есение второго входного

2 к л

Оно содержит память l,дешифРатоР слова во вторую и а во вторую ячейку и т,д, до за,кольцевой маркерный регистР 3iкомму- полнения всех М яче е ячеек з апоминающих таторы 4, первый счетчик 5, втоРой модулей третьего б третьего столбца. счетчик 6, элемент И 7, и эле- В момент когда момент, когда модули окажутся менты ИЛИ 8, группу 9 адрус- g() заполненными сче 5 ми, счетчик переполнится ных шин паМяти 1, первую груп- и окажется в пу 10 выходов дешифратора (подготовв нулевом состоянии, зипнси), вторую РуппУ 11 выхоДов 16 поступит в а сигнал его переполнения с выхода дешифратора (подготовка чтения), группостУпит в регистр 3 вызовет за пу 12 адресных шин счетчика 5 групнесение еще одной единицы в слепу 1 адресных шин счетчика б, пер13 е вы 14 управляющий вход устройства- ким Образом р находившейся там перв Оначально. Та(стробирование записи), второй 15

Управляющий вход УстРойства (стробиходиться дв е подряд расположенные

Комбинация вновь эапирование чтения), выход 16 переполне- санной един ния счетчика 5 (сдвиг по записи), 40 за ней дулей| ф . единицы и двух следующих выход 1 переполнения счетчика б х 17 за не нулей дешифрируется другим трехвходовым элементом И дешиф (сдвиг по чтению), первый управляю- ратора как сигнал подготовки защий выхбд 18 устройства (блокирование источника), информационные входы 19 писи по выходу 10 в модули четвертого столбца памяти 1. и выходы 20 устройства и второй управ- 45 ляющий вход 21 устройства, Так как сигнал, подготавливающий

Память 1 содержит матрицу однотип- запись, перешел с выхода 10 на вына выных запоминающих модулей с произволь- ход 10 дешифратора 2, выход счетчиной выборкой (например Мх1 бит со . ка 5 подключается к адресным входам встроенными дешифраторами) 1м, 5О м дулей четвертой строки через ком1ы . ., 1.кн и и элементов ИЛИ) обоз- мутатор 4 и вновь поступающ наченные I.g - I„ информационный вход 19 слова будут поДешиФратор 2 содержит две групйы следовательно записывать логич исываться в ячейки еских трехвходовых элементов И этих модулей до очередного переполи предназначен для дешифрации поло- нения счетчика 5 и переключения сигжения двух границ между группой ну- нала на выходах первой группы 10 делей и группой единиц, находящих- шифратора 2 ° ся в регистре 3, а также для переклю- Запись информации в другие соседчения коммутаторов и запоминающих ние модули происходит аналогично. модулей с режима запись на режим Сразу после заполнения моду и

1Ю

60 третьего столбца подряд расположен-управляющий вход кольцевого мар- ные в регистре 3 один нуль и две керного регистра 3 соединен с выхо- единйцы дешифрируются соответстдом 16 переполнения счетчика 5< c S вующим трехвходовым эпемен roM H дежит для занесения единицы . справа шифратора 2 на третьем выходе второй от границы 1™-1 0, а управля- 65 группы выходов ll> как сигнал подго6

746488

Формула изобретения тонки чтения из этих модулей. Так как счетчик б адресов чтения находится в нулевом состоянии, первое слово будет считынаться в приемник информации по первсму адресу модулей третьего столбца, а каждый синхроимпульс чтения, поступающий из приемника по второму управляющему входу

15, подготавливает адрес очередной ячейки этих модулей до момента считывания всех слов переполнения счетчика б.

Импульс переполнения счетчика б с выхода 17 поступает на вход регистра 3 и записывает нуль справа от группы нулей на место первоначально находившейся там единицы, Расположенные в этом регистре подряд нуль и дне единицы дишифрируются-дешифратором 2 как сигнал подготовки чтения из ранее заполненных модулей четвертой строки 20 аналогично описанному выше.

Для более надежной работы устройства при полном заполнении памяти элемент И 7 вырабатывает сигнал, ныданаемый на первый управляющий выход 25

15. и служащий для блокировки ввода информации со стороны источника, для исключения потерь информаций чтение памяти 1 осуществляется только при наличии на втором управляющем 3() выходе 21 сигнала, который вырабатывается элементом ИЛИ 8, Таким образом, устройство позволяет осуществить независимые запись и чтение информации из памяти, что 35 повышает его быстродействие, Кроме того, объем памяти устройства может быть достаточно просто изменяться без изменения его структуры путем исключения или добавления запо- 40 минающих модулей вместе с соответствующим коммутатором, частью дешифратора и частью кольцевого маркерного регистра, 1, Устройство для сопряжения, содержащее память, к ольцев ой маркерный регистр, соединенный выходами c соответствующими входами дешифратора, первая и вторая группа выходов которого подключены соответственно к первой и второй группе управляющих входов памяти, информационные входы и выходы которой являются соответствующими информационными входами и выходами устройства, и элемент И, соединенный входами с соответствующими ныходами первой группы дешифратора, а выходом — с первым управляющим выходом устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия устройстна, в него введены два счетчика, коммутаторы по числу адресных входов памяти и элемент ИЛИ, причем ныход каждого коммутатора подключен к соответствующему адресному входу памяти,. первые и вторые входы коммутаторов соединены соответственно с выходамй первого и второго счетчиков, выходы переполнения которых подключены соответственно к первому и. второму управляющим входам кольцевого маркерного регистра, а входы — соответственно к первому и второму управляющим входам устройства, выходы второй группы выходов дешифратора подключены к соответствующим входам элемента ИЛИ, выход которого является вторым управляющим выходом устройстна, 2, Устройство по и, 1, о т л и ч а ю щ е е с я тем, что память содержит и элементов ИЛИ и матрицу из и строк и К столбцов запоминающих

М-разрядных элементов, причем информационные выход и вход запоминающего элемента i-й строки (i 1,n) подключены соответственно через i-й элемент

ИЛИ к i-му выходу и i-му входу памяти, адресные, первый и второй входы запоминающего элемента j-ro столбца (j= 1,К) подключены соответстненно к

j-HM адресному и управляющим входам из первой и второй групп управляющих входов памяти, Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР по заявке Р 2166167/18-24, кл, G 06 F

3/04, 1975, 2. Авторское свидетельство СССР

9 488202, кл, G 06 F 3/04, 1973 (прототип) .

746488

Составитель В. Вертлиб

Техред А. Щепанская

Редактор Л, Утехина

Корректор M. Шарсти

Заказ 3944/38 Тираж 751

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4