Арифметическое устройство

Иллюстрации

Показать всеРеферат

l4@ (",)цчя

Д Ъ 4,„-, у

О П - "-А И- И- Е

ИЗОБРЕТЕНИЯ

Союз Сов,етских

Социалистических

Республик 7465О8

К АВТОРСКОМУ СВИ ВТЕЛЬСТВУ! (61) Дополнительное к ввт, свид-ву (51)М, Ид, С 06 F 7/38 (22) Заявлено 250478 (21) 2607470/18-34 с присоединением заявки Йо (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий (53) УД (681. 325 (088.8) Опубликовано 070780. Бюллетень Но 25

Дата опубликования описания 070780 — C (72) Авторы изобретения

Н. H. Иванова и A. И. Васильев (71) 3а яв ит ел ь (54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

25 (3)

Изобретение относится к цифровой вычислительной технике и может применяться в составе ариФметических устройств цифровых вычислительных машин.

Известны арифметические устройст- ва, предназначенные для решения, задач с большим числом тригонометрических функций, содержащие сдвиговые регистры, сумматоры-вычитатели и ком- 1 мутирующие блоки (1).

Недостатком устройств является отсутствие в их наборе операции вычисления произведения двух двоичных чисел за одну .операцию.:

Наиболее близким по технической сущности к предлагаемому является арифметическое устройство, реализующее алгоритм Волдера

X =Х g У..g- 2).

e+i ,) и позволяющее вычислять .

Y- K(Y .с06Л+ Хб(п Я)

1 (2)

Х = К (Х(COS A- Ye Ю a), или Я-К A +т,;в=а с P — х, где X;,У,, 8 - значения координат и угла на 1-й ..итеоапии t функция, показывающая направление вращения и равная для соотношений (2) °

Г, -5ig<8.

t для соотношений (3) .5 -ВiДП (-Y;) сс1 - угловая постоянная, равная :.arcing t - >.

У

К вЂ” коэффициент общего удлинения вектора, равный произведению коэффициентов удлинения на каждой 1итерации .

II II к-и к -и ф,z -"

< 2 <=2

Л1, У1, Л - начальные данные номер итерации i 2, 3 / ° ° °, °

При решении соотношений (2) и (3) устройство работает по алгоритму(1), 4 а при вычислении значения Д вЂ „ в устройстве организуется итерацйонный

746508 где Xo = Х (05 -4 1/Х/< 1); — номер итерации, i = 1, 2 3, е ° ° у пк оператор, придающии такое изменение Х; чтобы прн 1 п значение Х - 1,2„-,Х и равный i,/x;/ i

-,/х;/

Е; — значение. обратной величины на 1-й итерации (7о = 1 при

Х>0 и7О=-1 при Х(О).

Арифметическое устройство содержит три сдвиговых регистра, два коммутирующих блока, три сумматора-вычитателя и элемент И, причем разрядные выходы,.;, первого и второго сдвиговых регистров соединены с соответствующими вхо-. дами соответственно первого и второ+о коммутирующих блоков, управляющие входы которых подключенй к первому уп-20 равляющему входу устройства, выходы младших разрядов каждого из сдвиговых регистров подключены к первым входам соответствующих сумматоров-вычитателей,"вЫходы которых являются" выхода- .25 ми устройства, и подключены к входам старших разрядов соответствующих сдви" говых регистров и ко второму, третьему и четвертому управляющим входам устройства, второй вход первого "сумматора-вычитателя соединен с выходом элемента И, первый вход которого подключен к,выходу второго коммутирующе го блока, а второй вход — к запрещающему входу устройства, управляющие входы первого и третьего сумматороввычитателей соединены с пятым управляющим входом устройства, второй вход третьего сумматора-вычитателя подключен к первому разрешающему входу устройства f2). ., 4О

Однако структура такого устройства не приспособлена для вычисления произведения двух двоичных чисел за одну операцию.

ЦЕлью изобретения является расши- 4 рение Функциональных возможностей " ариФметйческого устройства за счет вычйслейия произведения двух двоич;ных чисел за одну операцию. .Поставленная цель достигается тем, щ что в арифметическое устройство, со держащее три сдвйговых регистра:, два коммутирующих блока, три сумматоравычитателя и элемент И причем разрядййе выходы первого и второго сдвиговых регистров соединены с соответствующими входами соответственно первого и второго коммутируЕмых блоков, управляющие входы которых подключены к первому управляющему"вхбду устройства, выходы младших разрядов каждого 60 из сдвиговых регистров подключены к первым входам соответствующих сумматоров-вычислителей, выходы которых являются выходами устройства и подключены к входам старших разрядов со 65

1 ответствующих сдвиговых регистров и .ко второму, третьему и четвертому управляющим входам устройства, второй вход первого сумматора-вычитателя соединен с выходом элемента И, первый вход которого подключен к выходу второго коммутирующего блока, а второй вход - к запрещающему входу устройства, управляющие входы первого и третьего сумматоров-вычитателей соединены с пятыми управляющим входом устройства, второй вход третьего оумматора-вычитателя подключен к первому Разрешающему входу устройства, дополнительно введены второй и третий элементы И, выходы которых соединены соответственно со вторым и управляющим Мходом второго сумматора-вычитателя, а вторые входы со вторым и йервйм разрешающими входами устройства, первый вход второго элемента И соединен с выходом первого коммутирующего блока, первый вход третьего"элемента И - с шестым управляющим входом устройства.

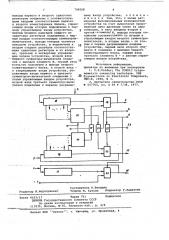

На чертеже показана структурная схема арифметического устройства.

Устройство содержит входы 1, 2, 3, 4, 5„ 8, выходы устройства 9, 10 и 11, первый коммутирующий блок

12, второй сумматор-вычитатель 13, второй коммутирующий блок 14, первый сдвиговый регистр 15, второй сдвиговый регистр 16, третий сдвиговый регйстр 17, первый сумматор-вычитатель

18, первый элемент 19 И, третий сумматор-вычитатель 20, второй элемент

21 И, третий элемент 22 И, зайрещающий вход 23 устройства.

ПредлагаЕмое устройство работает следующим образом.

При выполнении преобразования координат, построения вектора и вычисления обратного значения на входы

8 и 7 из блока управления поступают сигналы разрешения, которые постоянно присутствуют при выполнении укаэанных операций. Этими сигналами разрешения обеспечивается связь выхода йоммутатора l2 со вторым входом сум.матора-вычитателя 13 и связь управляющего входа сумматора-вычитателя 13 со входом устройства 6.

При вычислении произведения на вход 1 поступают управляющие сигналы, по которым в коммутаторах 12 и 14 осуществляются сдвигы вправо чисел, содержащихся в сдвиговых регистрах 15 и 16, а на вход 5 подается сигнал запрета. В блоке управлейия вход 6 устройства соединяется с входом устройства 8 и на оба эти входа подается управляющйй оператор, получаемый на выходе устройства 11 и анализируемый в блоке управления. На вход 7 устройства подается иэ устройства управления сигнал запрета только на втором mare вычисления.

746508

В исходном состоянии множимое А содержится в сдвиговом регистре 15, множитель В . — в сдвиговом регистре 17, а сдвиговый регистр 16 находится В нулевом состоянии. В процессе вычисления в сдвиговом регистре 16 происходит накопление сдвинутых множимых и в конце вычисления: содержится окончательный результат.

При пбдаче на вход 5 сигнала Запрет, на второй вход сумматора-(вычи- тателя 18 с выхода элемента И 19 поступает сигнал, равный нулю. Благодаря этому множимое А, поданное на вход

2, в процессе вычисления сохраняется в сдвиговом регистре 15 неизменным при установках сумматора-вычитателя

18 как на сложение, так и на вычитание. Управляющий оператор устанавлиг вает сумматор-вычитатель 13 на противоположное действие по сравнению с сумматорами-вычитателями 18 и 20. 20

Вычисление произведения Е = A ° В выполняется за (п + 1) шагов, где и - число разрядов в сдвиговых регистрах арифметического устройства.

На первом шаге проверяется знак 2$ умножителя В. Из устройства управления на управляющие входы б и 8 поступает сигнал запрета. Этот сигнал закрывает элемент,21 И и 22 И и устанавливает сумматор-вычитатель 20 на сло- щ жение. На второй вход сумматора-вычитателя 13 поступает 0, сдвиговый регистр 16 при выполнении первого шага продолжает сохранять нулевое состояние, значение сигнала на входе 7 устройства при выполнении первого шага безразлично.

На вход 7 устройства из блока памяти иоступает константа 2, которая суммируется сумматором- вычитателем: .20 с множителем В, находящимся в сдвировом регистре 17. На выходе 11 сумматора-вычитателя 20 образуется сумма

В 1 = В + 2, которая вновь засылаето ся в сдвиговый регистр. 17. В Завйсимости от В1 ) О или В1 с О в устройст-45 ве управления определяется значение управляющего оператора F для второго шага.

1 0, Е, ,=,0 5О

На втором шаге выполняется коррекция множителя А в зависимости от значения Е,1 (0,1)., Из блока управления на вход 7 поступает сигнал запрета, устанавливающий сумматор-вычитатель

13 на вычитание;- а на входы 6 и 8 поступает управляющий оператор 1.

При F 0 (В с О), элемент 21 И закрыт, множимое A на второй вход

:умматора-вычитателя 13 не поступает и сдвиговый регистр 16 продолжает сохранять нулевое состояние. При

1 (В > О), элемент 21 И открыт, множимое без сдвига поступает на вто- 65 рой вход сумматора-вычитателя 13 и вычитается из нуля, содержащегося до этого в сдвиговом регистре-16 °

Полученный дополнительный код мно жимого А< > вновь поступает в сдвиго вый регистр 16, определяя содержимое

Ьдвигового регистра 16 после выполнеНия 2-го шага как О - Ю,< A = Г, ° Адо„ °

Управляющее воздействие р подан.ное йа вход 6, выполняет соответствующую установку сумматора-вычитателя

20 О сложение .Г 1 вычитание на вход 7 из блока памяти поcтyпaет число 2 и на выходе 11 суммато- ра-вычитателя 20 образуется число

В2 = В1 -э в 81 2, которое вновь поступает в сднйговый регистр 17. Знак этого числа при появлении его на выходе 11 анализируется в блоке управления и определяет управляющий оператор для третьего шага.

Начиная с третьего шага в коммутирующем блоке 12 происходят сдвиги мно-. жимого A вправо на каждом шаге на один разряд, в сдвиговом регистре 16 накапливается произведение, а на вход из блока управления подается сигнал разрешения.

В результате выполнения 3-го шага в сдвиговом регистре 17 имеет место сумма "дол+ .

Для определения управляющего воэ" действия следующего (четвертого) шага из блока памяти на вход 7 поступа" ет число 2, на выходе сумматора-вычислителя 20 образуется число

— Вр — б п У В2 2 которое снова записывается в сдвиговый регистр 17.

После выполнения (n + l) шагов, где и равно числу разрядов в сдвиговых регистрах арифметического устройства, в сдвиговом регистре 16 содержится произведение Z = A В при изменении сомножителей и результата в пределах ! — 1 А 1, -1-"В < 1 и — 1 7, «1

В кОнЦе опеРаЦии РезУльтат Ь и может быть выведен по линии 11.

Эффективность изобретения заключа" ется в расширении Функциональных воэможностей арифметического устройства за счет вычисления произведения двух двоичных чисел за одну операцию, достигаемом за счет незначительного увеличения затрат оборудования.

Формула изобретения

Арифметическое устройство, содержащее три сдвиговых регистра, два коммутирующих блока, три сумматора-вычитателя и элемент И, причем разрядные

746508

Составитель В.Венцель

Техред N. Кузьма Корректор Г.Решетник

Редактор N.Íåäoëóæåíêî, Заказ 4103/17 Тираж 751

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д 4/5

Филиал ППП Патент, г. Уа орьд, ул. Проектная, 4

Подписное выходы первого и второго сдвиговых регистров соединены с соответствующими входами соответственно первого и второго коммутирующих блоков, управ- ляющие входы которых подключены к первому управляющему входу устройства, выходы младших раерядов каждого из сдвиговых регистров подключены к пер" вым входам соответствующих сумматороввычитателей, выходы которых являются выходами устройства, и подключены к. входам старших разрядов соответствующих сдвиговых регистров и ко второму, третьему и четвертому управляющим входам устройства, второй вход

-первого сумматора-вычитателя соединен с выходом элемента И, первый вход которого подключен к выходу второго коммутирующего блока, а второй вход— к запрещающему входу устройства, управляющие входы первого и третьего сумматоров-вычитателей соединены с 2О пятым управляющим входом устройства, второй вход третьего сумматора-вычитателя подключен к первому разрешающему входу устройства, о т л и ч а— ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет вычисления произведений двух двоичных чисел за одну операцию, в него введены второй и третий э- ементы!И, выходы которых со- . единены соответственно со вторым и управляющим входом второго сумматоравычитателя, а вторые входы - co вторым и первым разрешающими входами устройства, первый вход второго;элемента И соединен с выходом первого коммутирующего блока, первый вход третьего элемента И вЂ” с шестым управляющим входом устройства. б.

Источники информации, принятые во внимание при экспертизе

1. Y.E.Volderi The CORD1C trigonometric computing technigue. IRE

Transactions on Electronic Computers, VEC-8, 1959, Р 3.

2. Авторское свидетельство СССР

9 547765, кл. G 06 Г 7/38, 1977.