Двоично-десятичный сумматор

Иллюстрации

Показать всеРеферат

«»746509

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

r iver»

:-®::;, у

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

I (61) Дополнительное к авт. свид-ву (22) Заявлено 130977 (21) 2526167/18-24 (51)М. Кл.2

G 06 F 7/385 с присоединением заявки ¹

Госухврственный комитет

СССР оо делим и юбретеиии и открытий (23) Приоритет—

Опубликовано 0707.80 Бюллетень № 25 (53) УДК 681 ° 325 (088 ° 8) Дата опубликования описания 1007.80 (72) Авторы изобретения

И, В, Вайсер, Ю. С. Почтарь, Г. А, Пуэакова и Б. С. Шевченко (71) Заявитель

Ордена Ленина Институт проблем управления

1 (54) ДВОИЧНО-ДЕСЯТИЧНЫИ СУММАТОР

Целью изобретения является упроще,. ниее с уммат ора.

Для достижения поставленной цели в двоично-десятичном сумматоре, каждая декада которого содержит блок формирования суммы H блок формирования переноса, причем разрядные входы блока формирования суммы подключены ко входам первого слагаемого, а выходы — к выходам данной декады сумматора, вход переноса блока фсрмирования c+MMbl подключен ко входу переноса иэ предыдущей декады сумматора, выход блока формирования переноса подключен к выходу переноса в последую- щую декаду, блок формирования суммы в каждой декаде содержит узлы ввода второго слагаемого, ввода переноса и элементы НЕ. Входы узла ввода второго слагаемого непосредственно и через элементы НЕ подключены к разрядным входам блока формирования суммы, а выходы - к разрядным входам узла ввода переноса, выходы которого

Изобретение относится к области вычислительной техники и автоматического управления и может быть применено в системах числового управле5 ния.

Известны сумматоры, содержащие ячейки поразрядного суммирования, Каждая ячейка представляет собой сумматор с тремя входами и двумя выходами и содержит большое число логических элементов (1Ц2).

Наиболее близким по технической сущности к изобретению является двоично-десятичный сумматор, каждая декада которого содержит блоки формирования суммы и формирования перено са. Входы блока формирования суммы соединены со входами первого и второго слагаемых и со входом переноса иэ предыдущей декады, а выходы — с выходами данной декады, Выход блока формирования переноса подключен и выходу переноса в последующую декаду, а входы — к выходам некорректирован- 75 ной суммы блока формирования суммы (3).

В каждой декаде такого сумматора используются семь одноразрядных двоичных сумматоров и дополнительные ло-. 3Q гические элементы для связи между ними.

Недостатком сумматора является большое количество используемых элементов.

746509 подключены к выходам блока формирования судимы. Вход переноса узла ввода переноса подключен ко входу переноса блока формирования суммы. Первый, второй и третий входы блока формирования перноса соединены соответственно со входом старшего первого слагаемого, с управляющей шиной сумматора и с выходом старшего разряда данной декады.

Поставленная цель достигается 10 также тем, что блок формирования переноса содержит два элемента ИЛИ, эЛемент И и элемент запрета. Входы первого элемента ИЛИ и элемента И подключены к первому и второму входам блока формирования переноса, третий вход которого подключен к управляющему входу элемента запрета, вход .которого соединен с выходом первого элемента ИЛИ, Входы второго элемента 2О

ИЛИ соединены с выходами элемента И и элемента запрета, а выход - с выходом блока формирования переноса.

Поставленная цель достигается также тем, что узел ввода второго слагаемого содержит коммутационное поле, десять входных клемм которого подключены ко входам узла ввода второго слагаемого, а пять выходных клеммк выходам узла ввода второгО слагаемого. 30

Кроме того, узел ввода переноса содержит элементы И,ИЛИ и НЕ и- "ЗаПрета. Входы каждого элемента ИЛИ подключены к выходам соответствующих элемента И и элемента запрета, а вы- 35 ход - к соответствующему выходу узла ввода переноса, Первый вход каждого

i-ro (1=1, 2, 3,4) элемента И соединен со входом (i+1) -ro элемента запрета (i +l) му Разрядному 4О входу узла ввода переноса, первый вход которого подключен ко входу первого элемента запрета и через элемент НЕ к первому входу пятого элемента И. Вторые входы элементов И и управляющие входы элементов запрета подключены ко входу переноса данного узла.

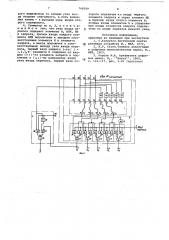

На фиг. 1 показана функциональная схема одной декады двоично-десятичного сумматора; на фиг, 2 - табличная запись десятичных чисел в коде

Либова-Крейга; на фиг, 3 — таблица ввода второго слагаемого.

Каждая декада сумматора содержит блок формирования суммы 1, входы 2 первого слагаемого, вход 3 переноса из предыдущей декады сумматора, выходы 4 данной декады сумматора, блок формирования перноса 5, выход б пе- 40 реноса в последующую декаду сумматора, Блок формирования суммы 1 содержит узел -ввода второго слагаемого 7, узел ввода переноса 8 и элементы НЕ 9, Узел ввода второго слагаемого 7 осуществляет сдвиг первого слагаемого на величину второго слагаемого представляет собой коммутационное поле с пятью выходными клеммами 10 и десятью входными клеммами 11, Узел ввода переноса 8 осуществляет сдвиг поступающей на его входы суммы двух слагаемых на величину единицы переноса из предыдущей декады и содержит элемент НЕ 12, пять элементов И 13, пять элементов запрета 14 и пять элементов ИЛИ 15, Блок формирования переноса 5 содержит элементы И 16, запрета 17, ИЛИ 18 и 19 °

Первый, второй и третий входы блока формирования переноса 5 подключЬны соответственно ко входу 2 старшего разряда первого слагаемого, к управляющей шине 20 сумматора и выходу 4 старшего разряда данной декады, Входы 2 подключены к разрядным входам блока формирования суммы 1, которые непосредственно соединены с первыми пятью входами 11 узла 7, а через элементы НЕ 9 с другими пятью входами 11 узла 7. Вход 3 подключен ко входу переноса блока формирования суммы 1, который соединен со входом переноса узла ввода переноса 8, разрядные входы которого подключены к выходам 10 узла 7, а выходы — к выходам блока формирования суммы, которые являются выходами 4 данной декады сумматора, Разрядные входы узла вводы переноса 8 подключены ко входам соответствующих элементов запрета 14, управляющие входы которых подключены ко входу переноса узла ввода переноса 8, Первые входы первого, второго, третьего и четвертого элементов И 13 подключены соответственно ко второму, третьему, четвертому и пятому разрядным входам узла ввода переноса 8, первый разрядный вход которого через элемент НЕ 12 соединен с первым входом пятого элемента И 13, вторые входы элементов И 13 подключены ко входу переноса узла ввода переноса 8, Входы элементов ИЛИ 15 подуключены к выходам соответствующих элементов

И 13 и элементов запрета 14, а выходы — к выходам узла ввода переноса 8, Входы элемента И 16 и элемента

ИЛИ 18 соединены с первым и вторым входами блока формирования переноса

5, третий вход которого подключен к управляющему входу элемента запрета

17, вход которого соединен с выходом элемента ИЛИ 18, Входы элемента ИЛИ

19 подключены к выходам элемента И 16 и элемента запрета 17, а выход - к выходу б блока 5, 74б509

1О

35

50

Первое слагаемое вводится в сумматор по входам 2 s коде Либова-Крейга.

Второе слагаемое вводится в сумматор в виде постоянной установки с помощью соединений в коммутационном поле между входными 11 и выходными

10 клеммами, Эти соединения устанавливаются в зависимости от значения в торого слагаемого в с оотв етс твни с таблицей, данной на фиг. 3. ЦиФры в таблице означают в еличину в торого слагаемого и расположены в пересечении вертикальных и горизонтальных столбцов, в которых указаны выходные клемкы 10 и 11 узла ввода второго слагаемого 7, которые должны быть при этом соединены между собой.

Например, для ввода второго слагаемого, равного 4, необходимо соеклеммы аз и „, а н, а и 3 а и 4 а и

Таким образом производится сложение произвольного первого слагаемого с постоянным вторым слагаемым, значение которого выбирается при настройке устройств а, Ввод переноса в. данную декаду осуществляется по входу 3, вывод переноса из данной декады - по выходу б °

Если значение второго сЛагаемого больше или равно пяти, на управляющий вход 10 подается сигнал коррекции.

Сумматор работает следующим образом.

Перед началом работы определяется значение второго слагаемого В, Если

В>5, подается сигнал на управляющий вход .20, В соответствии с таблицей, показанной на фиг. 3, производятся необходимые соединения в узле ввода второго слагаемого 7, При работе устройства каждому значению первого слагаемого А на входах 2 н значению переноса на входе 3 соответствует значение сумщ С = А+В на выходах 4.

Значение переноса в последующую декаду Формируется на выходе б, Например, пусть В выбрано равным

2. В соответствии с таблицей фиг. 3 производятся соединения между клеммами 11 и 10 узла ввода второго слагаемого 7, как показано на фиг, 1.

Тогда, если первое слагаемое A = 7 (код на входах 2 - 11100), а перенос равен 0 (О на входе 3), то на выходах

4 образуется код 10000, что соответствует сумме С = 9, Сигнала на выходе б нет, что соответствует отсутствию переноса в последующую декаду устройс тва.

В данном двоично-десятичном сумматоре не используется операция Сложение по модулю два, и в его конструкции отсутствуют двоичные одноразрядные сумматоры. Замена опера20

65 ции поразрядного двоичного сложения операцией сдвига первого слагаемого яа величину второго слагаемого позваляет существенно упростить конструкцию сумматора, Сложение произвольного числа с постоянной установкой является актуальной задачей для систем числового позиционирования. Данное устройство по своей конструкции существенно проще известных арифметических устройств, используемых в системах позиционирования, Формула изобретения

1. Двоично-десятичный сумматор, каждая декада которого содержит блок формирования суммы и блок формирования переноса, причем разрядные входы блока формирования суммы подключены ко входам первого слагаемого, а выходы — к выходам данной декады сумматора, вход переноса блока формирования суммы подключен ко входу переноса из предыдущей декады сумматора, выход блока формирования переноса подключен к выходу переноса в последующую декаду сумматора, о т л и ч аю шийся тем, что, с целью упрощения сумматора, блок формирования суммы в каждой декаде содержит узлы ввода второго слагаемого, ввода переноса и элементы НЕ, причем входы узла ввода второго слагаемого непосредственно и через элементы HE подключены к разрядным входам блока формирования сумма, а выходы подключены к разрядным входам узла ввода переноса, выходы которого подключены к выходам блока формирования суммы, а вход пе-! реноса узла ввода переноса подключен ко входу переноса блока формирования суммы, первый, второй и третий входы блока формирования переноса соединены соответственно со входом старшего разряда первого слагаемого, с управляющей шиной сумматора и с выходом стауаего разряда данной декады, 2 ° Сумматор по и, 1, о т л и ч аю шийся тем, что блок формирования переноса содержит два элемента

ИЛИ, элемент И и элемент запрета, причем входы первого элемента ИЛИ и элемента И подключены к первому и второму входам блока формирования . переноса, третий вход которого подключен к управляющему входу элемента запрета, вход которого соединен с выходом первого элемента ИЛИ, входы второго элемента ИЛИ - с выходами элемента запрета, а выход « с выходом блока формирования переноса, 3, Сумматор по п. 1, о т л и ч аю шийся тем, что узел ввода вто го слагаемого содержит коммутационное поле, десять входных клемм кото146509 в

2 2 2 2 2

Nul

МРСНдга

eau t рого подключены ко входам узла ввода второго слагаемого, а пять выходных клеим - к выходам узла ввода второго слагаемого.

4 ° Сумматор по п. 2, о т л и ч аю ц и и с я тем, что узел ввода пе- 5 реноса содержит элементы И, ИЛИ, НЕ и запрета, причем входы калдого элемента ИЛИ подключены к выходам соответствующих элемента И и элемента запрета, а выход подключен к сост" ветствуюцему выходу узла ввода переноса, первый вход каждого Х-го (1 =:

1,2,3,4) элемента И соединен со входом ((+ )-го элемента запрета и подключен к (iw h ) -му разрядному входу узла ввода переноса, первый вход которого подключен-ко входу первого элемента запрета и через элемент НЕ к. первому входу пятого элемента И, вторые входы элементов И и управляюцие входы элементов запрета подключены ко входу переноса данного узла, Источники информации, принятые во внимание при экспертизе

1 . С .Колдуэлл, Логический синтез релейных устройств М,, ИИЛ, 1972, 2, Н,Р, Скотт, Техника аналоговых и цифровых вычислительных машин. М,, ИИЛ, 1963, 3, Карцев М,А, Арифметика цифровых машин. М., Наука, 1969, с, 194-197, рис, 2-26 (прототип) 746509

Фиг,2

Выко3 глюка bhaga 2-го слагаемого

Фиг.Х

Составитель В, Березкин

Техред Ж. Кастелевич

Редактор Л, Утехина

Корректор М. Вигула

Заказ 3944/38 Тираж 752

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д, 4/5

Подписное

Филиал ППП Патент, r, Ужгород, ул, Проектная, 4