Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ па 746518

Ф

i (61) Дополнительное к авт. свнд-ву (22) Заявлено 22.05.78 (2) )2619584/18-24 с присоединением заявки J%(23) ПриоритетОпубликовано 07.07.80. Бюллетень,% 25

Дата опубликования описания 08.07.80 (5l)М. Кл.

9 06 F 9/16

Государственный комитет

СССР ао делам изобретений к открмтнй (53) У,П,К 681.14 (088.8) 1

П. А. Грездова, В. A. Иванов, А. В. Палагин и В. В. Сыров (72) Авторы изобретения

Ордена Ленина институт кибернетики АН Украинской CCP (7!) Заявитель (54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

Изобретение относится к области вычислительной техники и предназначено для применения в устройствах управления цифровых вычислительных машин с микропрограммным управлением.

Известны устройства микропрограммнс- > го управления $1), содержащие запоминающий блок, регистры, дешифраторы, блок местного управления, отличающиеся построением блока формирования управляющих

1О сигналов.

Недостатком известного устройства яв ляется большой объем блока памяти.

Наиболее близким по технической cymности к изобретению является устройство

I 15 микропрограммного управления f2), содержащее запоминающий блок, регистры, дешифраторы, блок формирования управляющих сигналов, блок переключения и блок местного управления, включающий в себя генератор тактовых импульсов, элементы и задержки, причем выходы блока местного управления подключены соответственно к управляющим входам peraerpa, 2 адреса микрокоманд, а входы связаны с шиной признаков условий ветвления и нулевым и единичным выходами триггера управления, кокоторые также подключены к управляющим входам элементов И блока переключения.

Недостатком известного устройства является большая разрядность микрокоман . ды н, следовательно, большой объем блока памяти.

Бель изобретения - упрощение устройства за счет сокращения объема блока памяти.

Бель достигается: тем, что в устройство микропрограммного управления, содержащее генератор тактирующих импульсов, выход которого соединен с первым входом блока формирования адреса, второй и третий входы которого являются входами устройства, а четвертый вход соединен с вы ходом блока переключении, выход блока формирования адреса соединен со входам блока памяти, выход которого соединен co . входом регистра микрокоманд, первая, вто-.

3 7,,4 раяе третья и четвертая группы выходов которого соединены со входами соотвечст»

"" Ьующих дешифраторов, третья и четвер ая группы выходов регистра микрокоманд со единены также с первой группой входов блока переключения, первая группа выходов каждого дешифратора соединена с пер» вой группой входов элементов Д соответствующей группы, второй выход каждого дешифратора соединен со второй группой входов элементов И всех групп, кроме со ответствующей группы, второй выход первого дешйфратора соединен также со вторым входом блока переключения и со вхо» дами блокировки всех дешифраторов, кроме первого и второго.

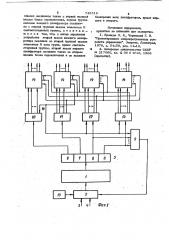

На фиг. 1 и 2 приведена блок-схема устройства.

Устройство содержит блок памяти 1, блок формирования адреса 2, имеющий вход 3 условий и вход,4 кода команды, регистр микрокоманд 5 содержащий несколько групп разрядов 6, 7 и 8 (поля микрокоманды), блок переключения 9, дешифраторы 10, 11, 12 и 13, группы элементов И 14 и генератор тактирующих импульсов .15. Количество .дешифраторов

10, 11, 12 и 13, а также групл элемен" тов И 14 равно количеству групп разрядов 6, 7 и 8 соответственно.

Выход генератора 15 подключен к управляющим azollaM блока формирования адреса 2, а также к синхронизирующим входам (на чертеже не показано) дешифра торов и элементов И, Устройство работает следующим обра» зом.

Под воздействием тактирующего сигнала от генератора 15 блок формирования адреса 2 выдает в блок памяти адрес микрокоманды. Через некоторое время, равное времени считывания блока памяти

1, на выходе последнего появляется микрокоманда, которая заносится в регистр 5.

Считанная микрокоманда состоит из нескольких полей, которые образуют группы разрядов 6, 7 и 8. Код каждого поля. подается на соответствующий дешифратор . 10,11,12 вти13, сигналынавыходах16 которых участвуют в формировании управляющих сигналов элементами И 17 групп 14 в соответствии с их описанной структурой.

При естественном следовании микрокоманд ядрес следующей микрокоманлы образуется блоков4 2 путем увеличения те кущего адреса, наиример, на единицу.

6518 4.

При необходимости изменения естественного порядка следования микрокоманл, в поле 6 микрокоманды указывается код, вызывающий появление сигнала на выхо» де 16 дешифратора 10. Этот сигнал бл кирует дешифраторы 12, 13 и открывает элементы И блока переключения 9, через который разряды полей 8, являющиеся адресом перехода, заносятся в блок 2.

10 При условных переходах соответствующие признаки ветвления заносятся через вход 3 блока 2, модифицируя адрес лю бым известным методом, например, диэьюнктивным вписыванием признаков ве ь-

15 вления в младшие разряды адреса.

Переход к первой микрокоманде микропрограмм осуществляется по адресу, который формирует я блоком 2 по коду команды, поступающей на вход 4.

Так же как ив поле 6, один иэ кодов, в котором вызывается переход по принудительному адресу, блокирует дешиф раторы 12. В каждом поле микрокоманды есть одйн 1в общем случае таких кодов

25 может быть несколько), который определяет тип всей микрокоманды и может изменять смысл других полей.

Сигналы, которые соответствуют колам, интерпретирующих смысл тугих полей, З0 появляются на выходах 16 дешифраторов

10, 11 и 12. Для их выработки весьма, . удобными являются нулевые коды (00...0), которые позволяют в ряде случаев уменьшить аппаратурные затраты.

55 Возможность интерпретации кодов одних палей микрокоманды в зависимости от кодов других полей позволяет эффективно испсаьэовать разрядную сетку регистра микрокоманд, уменьшить разрядность микроко40 манлы и блоха памяти в целом.

Формула изобретения

Устройство микропрограммного управления, содержащее генератор тактирующас импульсов, выход которого соединен с первым входом блока формирования адреса, второй и третий ar.оды которого являются

50 входами устройства, а четвертый azon соелинек с выходом блока переключения, выход блока формировании адреса соединен со входом блока памяти, выход которого соединен со входом регистра мипрокоманл, f5 первая, втораа, третья и четвертая группы выходов которого соединены со входами соответствующих дешифраторов, третья и четвертая группы жиодав регистра микро

5 746518 команд соединены также с первой группой блокировки всех дешифраторов, кроме первходов блока переключения, первая группа вого и второго. выходов каждого дешифратора соединена с первой группой входов элементов И Ис гочники информации, соответствующей группы, о т л и ч а ю - принятые во вниманЖ при экспертиэ .m е е с я тем, что, с целью упрощения 1. Кравцов Л. Я., Черницкий Г. И. устройства второй выход каждого дешиф- Проектирование микропрограммных усъратора соединен со второй группой входов ройств управления . Энергия, Ленинград, элементов И всех групп, кроме соотнес- 1976, с. 84-58, рис. 14-18. ствующей группы, второй выход первого 1Е 2. Авторское свидетельство СССР дешифратора соединен также со вторым . % 217066, кл. G 06 F 9/16, 1968 входом блока переключейия и со входами (прототип).

746518

Составитель Г. Пономарева

Редактор Н. Зйнзикова Техред Л. Теслюк Корректор М. Вигула

Заказ 4104/18 Тираж 751 Подписное

Ш ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раущскаи наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектнаи, 4