Многоканальное приоритетное устройство

Иллюстрации

Показать всеРеферат

» ФЪ

Ф„:, О Il И С А Й И" Е- —

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскии

Социалистических

Республик

46519 (6l ) Дополнительное к авт. свид-ву— (22) Заявлено 29.12.77(gi) 2578310/18-24 (51)М. Кл.

G 06 P 9/18 с присоединением заявки ¹â€”

Государстваинмй комитет

СССР (23) Приоритет— (53) УДК 681., 14(088.8) пв делам изобретений и открытий

Опубликовано 07.07.80. Бюллетень ¹25

Дата опубликования описания 10.07.80

Л. М. Петрова, Э. П. Овсянникова-Панченко, Б. В. Шевкопляс . и А. В. Сперанский (72) Авторы изобретения (7! ) Заявитель (54) МНОГОКАНАЛЬНОЕ ПРИОРИТЕТНОЕ

УСТРОЙСТВО

Изобретение относится к вычислительной технике, может быть использовано ! в вычислительных системах, содержащих ряд блоков, подключенных к устройству общего пользования, например, к общей информационно-адресной магистрали.

Известно многоканальное устройство для подключения источников информациИ к общей магистрали (1). В этом устройстве сигнал опроса вырабатывается в од10 ном из блоков и проходит последовательно по кольцу все блоки, участвующие в работе. Йостигнув блока, в котором он выработался, сигнал кольцевого опроса при наличии заявок на общей шине pere15 нерируется, а при отсутствии заявок исчезает. Недостатком устройства является его повышенная сложность, связанная с обеспечением высокого быстродействия и равноприоритетной дисциплины обслуживания.

Из известных устройств наиболее близким по технической сущности K пред. лагаемому является многоканальное при2 оритетное устройство g2). Оно содержит в каждом канале триггер запроса, выход которого соединен с первым входом элемента подтверждения запроса и, через элемент передачи разрешения, — с входом следующего канала. Триггер запроса выполнен на двух элементах И-НЕ, соединенных по схеме Вбгриггера, управляемого сигналами логических нулей, элемент передачи разрешения выполнен на инверторе, элемент подтверждения запроса - на двухвходовом логическом элементе И.

У этого устройства низкая помехозащищенность и ограниченные функциональные возможности.

Первый недостаток состоит в следующем. В исходное состояние, когда отсутствуют сигналы запросов и сигнал разрешения во всех последовательно соединенных блоках, в каждом из них

RS -ãðèrråð на элементах И-HE установ-! лен в запрещенное состояние», при котором на входы установки и сброса одно временно подаются сигналы логических нулей; и на обоих плечах триггера за счет этого поддерживаются логические единицы. При работе устройства в реальной системе не исключена возможность одновременного поступлейия на некоторый блок сигналов запроса и разрешения. В этом случае R5-триггер иэ "запрещенного" состояния переходит непосредственно к состоянию запоминания {входы установ- 10 ки и сброса одновременйо переходят из нулевого в единичное состояние), минуя стадию установки или сброса. Процесс перехода неуправляем и может протекать, в такой последовательностй: спуста вре- 15 мя задержки элементов И-HE на их выходах формируются логические нули, которые по цепям обратной связи передаются на входы элементов И-НЕ, й,"в"сл»учае, если из двух элементов И-HE элемент, 20 управляемый запросом, оказался более

"быстрым", триггер переходит в устой чивое состояние, при котором íà его плече, соединенном со входом инвертора, хранится единица, Ч аким образом, зап " рос,: поступивший одновременчо с разрешением, в конечном счете воспринимаетса и передается на выход подтверждениа запроса s виде положительного потенциа-,. .ла. Однако одновременно с этим отрица- ЗО тельный импульс, формируемый на триггере, цроходит через инвертор и в виде сиг- нала разрешении поступает в следующие блоки, что может привести к одновремен- ному выходу на магистралЫ двух активных 35 устройств и, следовательно, к сбою.системы.

Отмеченный выше недостаток„связаннйй с ограниченными функциональными

40 возможностями известного устройства, обусловлен двумя факторами. Во-первых, при отсутствии сигнала разрешения триггер запроса "теряет" запрос, если он имеет импульсный характер. Во- вторых, 45

;за счет одновременного стробирования последовательно соединенных элементов

И-HE и И сигналом разрешения при отсутствии запроса на выходе элемента И формируются ложные кратковременные

\ 50 импульсы, которые необходимо компенсиI ровать введением дополнительных злемен тов, например, интегрирующих R5 звеньев, подключаемых" к выходам« элементов И.

° - 1

Цель изобретения - повышение помехо55 устойчивости и расширение функциональ». ных воэможностей устройства.

Поставленная цель достигается тем, что в устройство введены элемент И-HE„

4 первый и второй элементы НЕ, триггер компенсации, причем первый вход элемента И-НЕ является четвертым входом каждого канала устройства, второй вход элемента И-НЕ, вход первого элемента HE. и первый вход триггера компенсации соединены со вторым входом элемента И, выход элемента И-HE соединен со вторым входом триггера запроса, выход первого элемента НЕ подключен ко входу второго элемента НЕ, выход которого соединен со вторым входом триггера компенсации, выход которого подключен к третьему входу элемента И и третьему входу триггера подтверждения запроса.

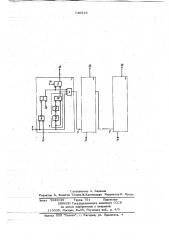

На чертеже показана логическая схема предлагаемого многоканального приоритетного устройства.

Устройство содержит ряд последовательно включенных каналов 1, каждый из которых включает в себя триггер запроса 2, выход которого соединен с первым входом триггера подтверждения запроса 3 и через элемент И 4 — с третьим входом 5 следующего канала, эле- . мент И-Ht 6 и линия задержки 7, выполненнук> в виде последовательно соединенных первого элемента HE 8, второ о эле- . мента HE 9 и триггера компенсации 10, выход которого соединен с третьим входом триггера подтверждения запроса 3 и с третьим входом элемента И 4. Второй вход элемента И 4 соединен со входом первого элемента НЕ 8, со входом элемента И HE 6, с установочным входом триггера 10 и со входом 5 соответствующего канала, выход элемента 6 соединен со входом триггера 2. Вход 11 каждого канала является входом прйема запроса, выход 1 2 каждого канала является выходом подтверждения запроса„ входы

13 и 14 каждого канала служат для ус"тановки в исходное состояние соответственно триггера 2 и триггера 3.

Устройство может быть выполнено на различных типах логических элементов, Юля определенности в дальнейшем предполагаетса, что элемент 6 представляет собой двухвходовый логический элемент типа ИЛИ-НЕ, элемент 4 — элемент типа И, элементы 2, 3 и 10 — D- триг-. геры. Кроме того, предполагается, что пары элементов: 2 и 10, а также 6 и 8 выполнены на одних и тех ке кристаллах интегральных схем. Это угловие не обязательно, однако оно "автоматически" обеспечивает га рантированные временные

74651

5 соотношения между информационными и ,управляющими сигналами, а именно, превышение времени задержки распространения входного сигнала разрешения по цепи

8- 9" 10 над временем задержки по цепи 62.

Ниже рассмотрен принцип действия многоканального приоритетного устройшения между этими сигналами определяются принятым для данной системы интерфейсомм.

Использование предлагаемого много- канального приоритетного устройства в вычислительных системах позволяет повысить их помехоустойчивость и расширить функциональные возможности.

Источники информации, принятые во внимание пря экспертизе

1. Авторское свидетельство СССР

М 394789, кл. G 06 F 8/04, 1970.

2. Авторское свидетельство (. ССР

N 544967, кл (я 06 Р 9/18, 1972 (прототип) . ства.

Устройство приводится в исходное сос- 16 ,тояние воздействием импульсных сигна.лов на входы установки 13 и l4„после чего на выходах триггеров 2 и 3 устанавнавливаются логические единицы. Сигналы разрешения в исходном состоянии отсутствуют„т. е, на входы 5 каждого блока поданы логические нули. Триггер

10 под действием нулевого сигнала на установочном входе, связанном со вхо. Дом 5, переведен в нулевое состояние. 2О

Сигнал запроса, поступа|ощий на вход

1 l в виде логического нуля, при отсутствии сигнала разрешения проходит через элемент 6 и подается на синхронизирующий вход D триггера 2, переводя его в нулевое состояние, так как "D — вход этого триггера подключен к шине логичесКОГО нуля {например, при полОжителье ной логике - к шине "земля", Сигнал разрешения, поступающий на вход 5 в ЗО виде логической единицы, через элементы HF. 8 и 9 поступает на синхронизирующий вход Т3 триггера 10, переводя его и единичное состояние, так как

13 -вход этого триггера подключен к 3S шине логической единицы. Далее, в зависимости от состояния триггера запросов 2, или срабатывает элемент И 4, передавая сигнал разрешения на вход 5 следующего блока, или под Воздействием 4О фронта сигнала с выхода триггера 10

HB синхронизирующий ВхОд ) триггера

l 4 ПОследний формирует HB выходе 12 сигнал подтверждения запроса в виде логического нуля, так как на 9 -вход это-- 45 го триггера подан логический нуль с, триггера 2. Запрос, поступающий на вход

1 1 при наличии сигнала разрешения на входе 5, блокируется элементом 6 на время трансляции сигнала разрешения через

50 данный блок; по окончании трансляции запрос запоминается на триггере 2. Ус тановка триггеров 2 и 3 в исходное сос тояние производится сигналами от устройства, получившего сигнал подтверждения М запроса; конкретные временные соотноФормула изобретения

Многоканальное приоритетное устройство, содержащее в каждом канале триг.г.ep запроса, триггер подтверждения зап:роса, элемент И, причем первый вход ,триггера запроса является первым входом каждого канала устройства, а выход триггера запроса соединен с первым входом триггера подтверждения запроса и первым входом элемента И, второй вход триггера подтверждения запроса являетса вторым входом каждого канала устройства, а выход триггера подтверждения запроса является выходом каждого канала устройства, второй вход элемента

И является третьим входом каждого канала устройства, а выход эпемента И соединен с третьим входом следующего канала устройства, о т л и ч а ю щ е

B c я тем, что, с целью ttGshltHBHHH ПО» мехоустойчивости, в каждом канале введены элемент И-НЕ, первый и второй элементы НЕ, триггер компенсации, причем первйй вход элемента И-HE является четвертым входом каждого канала уст- ройства, второй вход элемента И-НЕ, вход первого элемента НЕ и первый вход .триггера компенсации соединены со вхорым входом элемента И, выход элемента И-НЕ соединен со вторым входом триггера запроса, выход первого эле,мента НЕ подключен ко входу второго элемента НЕ, выход которого соединен со вторым входом триггера компенсации, выход которого подключен к третьему входу элемента И и третьему входу триггера подтверждения запроса.

746519

° ° °

Составитель A. Баранов

Редактор Б. Федотов ТехредЖ.Кастелевич Корректор И. Муска

Заказ 3949/39 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4