Устройство для исправления ошибок при итеративном кодировании

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()746528

Союз Советскни

Социалнстнческни

Республик (6! ) Дополнительное к авт. свнд-ву(22) Заявлено 14.04,78 (2l ) 2611913/18-24

{5I)M. Кл.

G 06 F 11/00 с присоединением заявки М (23 ) П р нори тетГасударственный комитет

СССР йа делам изобретений и аткрытий

Опубликовано 07.07.80. Бюллетень М 25

Дата опубликования описания 1 0.07.80 (53) УДК 681.326.,7 (088.8) (72) А вторы изобретения

В. А. Брик и Е. А. Брик (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

ПРИ ИТЕРАТИВНОМ КОДИРОВАНИИ

Изобретение относится к дискретной технике и может быть использовано в цифровых вычислительных машинах, устройствах передачи дискретной информации и т.п.

Известны устройства контроли правильности работы аппаратуры дискретного

S действия, проверяющие правильность хранящейся, передаваемой или обрабатываемой информации, содержащие свертки (схемы определения четности или нечетности информации (1j, P2) и (3)

Недостатком известных устройств является невозможность исправления многократных ошибок в контролируемом коде.

Наиболее близким техническим решением к предлагаемому является устройство для исправления ошибок при итеративном кодировании, содержащее блок хране ния информации с дешифратором адреса, сумматор по модулю два, регистры, элементы И и блок сравнения (4) .

Недостатком устройства является невозможность исправления любых четных многократных (т.е. двойных, четверных и

2 т д.) ошибок в любом из контролируемых информационных регистров.

Белью изобретения является повышение надежности работы контролируемой аппаратуры дискретного действия.

Поставленная цель достигается тем, что в устройство для исправления ошибок при итеративном кодировании, содержащее

A,m - разрядных информационных реги- сттзов, первый rn — разрядный контрольный регистр и второй n - разрядный контрольный регистр, первую группу из rn ..сумматоров по модулю два, вторую группу из и сумматоров по модулю два и блок сравнения, причем информационные выходы каждого > -го разряда всех информационных регистров соединены с соответствующими входами 1 -ro сумматора по моду лю два первой группы, выход j -го разряда первого контрольного регистра соединен с (o +1)-м входом 1 -го сумматора по модулю два первой группы, выходы сумматоров по модулю два первой и вто .рой групп соединены соответственно с пер

74652 вой и второй группой входов блока сравнения, в устройство введено о сумматоров по модулю два, во второй контрольный регистрдополнительно п разрядов, причем выходы вновь введенных сумматоров по модулю

5 два второй группы соединены. с дополнительной группой входов блока сравнения, -ый разряд j -ro информационного регистра соединен с -м входом (i + 1- 1)-го сумматора по модулю два. 10 второй группы, i -ый разряд второго контрольного регистра при a n соединен с (i+1)-м входом \ -го сумматора по модулю два второй группы, а при <> n соединен с (i+2)-м входом i «го.сумматора 15 по модулю два второй группы > -ый разряд первого контрольного регистра соединен с

{т +1)-ым входом (1 + )-го сумматора по модулю два второй группы.

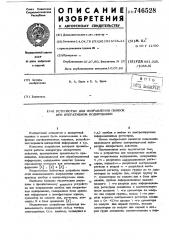

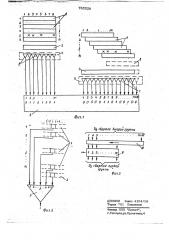

На фиг. 1 изобра>кено устройство для исправления ошибок при итеративном кодировании при n = 6 и m=8;на фиг.2-схема подключения одного сумматора по модулю два первой группы; на фиг. 3 — схема реализации одного из вариантов блока сран 25 ненни, входящего в состав устройства.

B состав устройства входит и, чразрядных информационных регистров 1, 1"р1 -разрядный первый контрольный регистр 2, второй контрольный. регистр 3, Зо имеющий разрядность (n + 1 }, первую группу 4 (n + 1)-входных сумматоров 5 по модулю два и вторую группу 6 сумматоров 7 по модулю два, блок 8 сравнения, (+ )-разрядный регистр 9 совпадения 35 и (и +т)-разрядный регистр 10 сдвига (влево) .

Двукратное изображение информационных регистров 1 и первого контрольного регистра 2 (в левой и в правой частях фиг. 1 ) является условностью.

Первый контрольный регистр 2 и сумматоры 5 по модулю два первой группы 4 и все их соединения между собой и с ин« формационными регистрами 1 выполнены, 45 как на фиг. 2. Соединения же информациI онных регистров 1, первого контрольного регистра 2 и второго контрольного регистра 3, разрядность которого увеличена с и до n + рч, с сумматорами 7 по модулю два второй группы 6 (число которых также увеличено с и до и + & ) выполнены путем последовательных сш3игов регистров 1 и 2 таким образом, что -й разряд (i 1,2, ...,m ) j. -го информаци55 онного регистра () 1,2, ...р) соединен -м входом (1 +) -1)-го сумматора 7 по модулю два второй группы 6, p -й раз8

*ряд (p = 1 2 ...„ ) первого контрольного регистра 2 соединен с (n +1)-ым входом (p + Tl)-го сумматора 7 по модулю два второй группы 6, а к-й разряд второго контрольного регистра 3 (K =1,2, ..., n+m), при ка и, соединен с (К+1)-ым входом К-ого сумматора 7 по модулю два второй группы 6, а при К> >соединен с (n+2)-м входом К-ого сумматора 7 по модулю два второй группы 6.

Выходы сумматоров по модулю два обеих групп 4 и 6 соединены с блоком сравнения 8.

Устройство работает следующим образом.

Предположим, что в одном из информационных регистров 1, например в пятом, возникает ошибка любой кратности, напри мер одновременно в четырех разрядах,втором, третьем„пятом и восьмом (на фиг, 1 эти разряды отмечены знаком х).

Тогда на выходах сумматоров 5 по моду ну два первой группы 4 вместо кода

00000000 (при исправной контролируемой аппаратуре) образуется код 01 1 01 001, на выходах сумматоров 7 по модулю два второй группы 6 вместо кода

00000000000000 образуется код

00000110100100. Оба кода с выходов сумматоров 5 по модулю два первой группы 4 и с выходов сумматоров 7 второй группы 6 поступают на блок 8 сравнения, который производит сравнение этих двух кодов. Это сравнение производят последовательно, сдвигая вправо на один разряд е выходной код первой группы 4 относительно выходного кода второй группы 6 или (что то же самое) сдвигая влево выходной . код второй группы 6 относительно выкопкого кока первой группы 4

000001 1 01 001 00

01 1 01 001

Эти два кода совпадают тогда и только тогда, когда число сдвигов равно (i1) где } - номер неисправного регистра (в данном случае р =5). Знал число сдвигов (т.е„ зная номер неисправного регистра) и зная номера всех неисп» равных разрядов этого регистра (по единицам в выходном коде первой группы 4), легко исправить (инвертированием) эти разряды, Таким образом устройство позволяет обнаруживать любые одиночные и групповые ошибки в 6оМ из информационных регистров 1, а также в первом контрольном регистре 2 (ошибки в котором нахо° дятся и исправляются точно так же, как и

7465 28

2. Самофалов К. Г. и др. Структурно-логические методы повышения надежности запоминающих устройств. М;, М ашиностроение, 1976, с. 40-47.

3. Селлерс. Ф. Методы обнаружении ошибок в работе ЭБВМ. М., Мир, 1972, с. 269-270.

4. Авторское свидетельство СССР

М> 364032 кл. Я 11 С 29/00, 25,01.71 (прототип) . ошибки в информационных регистрах 1) и во втором контрольном регистре 3 (при ошибках so втором контрольном регистре

3 выходной код первой группы 4 не содержит единиц, единицы в выходном коле второй группы 6 указывают неисправные разряды второго контрольного регистра 3).

Само сравнение кодов в блоке 8 сравнения можно производить при помощи са« мых различных схем, например при помо-10 щи (A+m)-разрядного сдвигающего (влево) регистра 10 и rn -разрядной схемы совпадения 9 (фиг. 3). Более быстро (без сдвигающих регистров, требующих до

h временных тактов) сравнение производят 15 при помощи (n+1)m -разрядных схем совпадения (подобньсх схеме 9), соответствующим образом соединенных с выходами сверток 5 и 7.

Обнаружение и исправлени е ошибок, в 20 первом контрольном регистре 2 не является обязательным условием работы устройства (связанное с этим обнаружением и исправлением - оборудование изображено пунктиром, фиг. 1 ) . 25

Следует отметить, что использование термина "регистр (применительно к информационным и контрольным регистрам 1,2 и 3) является в известной степени услов.ностью. В реальных объектах контролируе- ЗО мые (информационные) и контрольные коды вырабатываются не только регистрами, но и различными другими элементами и устройствами — микросхемами памяти, различными блоками цифровых вычислительных35 машин и других дискретных устройств (арифметическими и запоминающими уст ройствами, блоками ввода-вывода, каналами связи и т.д.) .Применение устройства для исправления4п ошибок при итеративном кодировании позволяет существенно повысить надежность работы различных видов аппаратуры дискретного действия, а также позволяет, строить такую аппаратуру из частично де-45 фектных комплектующих изделий, например позволяет применять микросхемы памяти,. в которых по отдельным адресам находятся неисправные запоминающие элементы, увеличивать периоды работы систем между 56

Ъ профилактическими ремонтами и т. д, Формула изобретения

Устройство для исправления ошибок при итеративном кодировании, содержащее

rl,rn -разрядных информационных регист- 55 ров, первый & разрядный контрольный регистр и второй и --разрядный контрольный регистр, первую группу из гт сумматоров по модулю два, вторую группу из сумматоров по модулю два и блок сравнения, причем информационные выходы каждого

1 -ro разряда всех информационных регистров соединены с соответствующими.входами 1 -го сумматора по модулю два первой группы, выход 1 -го разряда перво го контрольного регистра соединен с (+1)-м входом i -го сумматора по модулю два первой группы, выходы суммато»ров по модулю два первой и второй группы соединены соответственно с первой и второй группой входов блока сравнения, о т л и ч а ю щ е е с я тем, что, с целью повьппения надежности в устройство введено гъ сумматоров по модулю два, а во второй контрольный регистр - дополнительно м разрядов, причем выходы вновь введенных сумматоров по модулю два второй группы соединены с дополнительной группой входов блока сравнения, -ый разряд р -го информационного регистра соединен с -м входом (1 + j --1)-го сумматора цо модулю два второй группы, 1 -ый разряд второго контрольного регистра при I (p соединен c (i +1)-м входом -ro сумматора по модулю два второй группы, а при I > и соединен с (i +2)-м входом i -го сумматора по модулю два второй группы, i -й разряд первого контрольного регистра соединен с (%+1)»ым входом (I + 11)pp сумматора по модулю два второй группы.

Источники информации, принятые во внимание при экспертизе

1. Сидоров А. N. Методы контроля электронных цифровых машин. М., Советское радио", 1966, с. 97-98, 768828

Му сбирай Ьиорой грулпы. ni irl

Лд-Ag сбитой пербоо рдеем фУ2.Д Фиг.Л

Фидиал ППП "Патент", т .Ужгород, ул. Проектная,4

ЦНИИПИ Заказ 4104/18 3 ираж 751 Подписное