Устройство для цифровой обработки сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАН

ИЗОБРЕТЕНИЯ

--"- .юзиа1в ййтйк . «о та,, а въощ д о; бйя42тб,(я Д Q д (,1)746 37

Союз Советскни

Соцнапнстмческнк

Респубпнк

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (5l)М. Кл.

С, 06 t= 15/34 (22) Заявлено 20.12.77(21) 2558344/18-21 с присоединением заявки ¹

Государственный комитет

СССР (23) Приоритет

Опубликовано 07.07.80. Бюллетень ¹ 25

Дата опубликования описания 10.07.80 ио делам изобретений и открытий (53) УДК 621.375..8(088.8) (72) Авторы изобретения

В. B. Пискорж, С. E. Фалькович, С. Л. Голинец, и A. A. Чумаченко (7I) Заявитель

Харьковский авиационный институт

- . (54) УСТРОЙСТВО ДЛЯ БИФРОВОЙ ОБРАБОТКИ

СИГНАЛОВ

Изобретение относится к измерительной технике.

Известно устройство для цифровой обработки сигналов, содержашее систему генераторов, формируюших набор гетеродинных напряжений, используемых в сис5 теме фильтрации 1 .

Для данного устройства характерно недостаточное быстродействие, определяемое последовательным поиском производ1О ной сигнала.

Наиболее близким к изобретению по технической сушности является устройство для цифровой обработки сигналов, cogepжашее блок цтврровой обработки сигналов, состояший из двух каналов, каждый из которых состоит из последовательно включенных смесителя, фильтра нижних частот, дискретизатора и аналого-цифрового преобразователя, причем первые входы смесителей соединены с входной шиной, вторые их входы соединены с выходами квадратурного генератора, а вторые входы дискретизаторов соедине2 ны с выходами задаюшего генератора, блок вычисления дискретного преобразования Фурье, входы которого соединены с выходами блока цифрового преобразования, квадратор, выходы которого соеди- . нены соответственно с первым входом интерполятора и входом блока обнаружения, выход которого соединен со вторым входом интерполятора 2 .

Данное устройство недостаточно точно.

Белью изобретения является повышение тОчнОсти устройства, Поставленная пель достигается тем, что в устройство, содержашее блок цифрового преобразования сигналов, состояший из двух каналов, каждый из которых состоит из последовательно включенных смесителя, фильтра нижних частот, дискретизатора и аналого-цифрового преобразователя, причем первые входы. смесителей соединены с входной шиной, вторые их входы — с выходами квадратурного .» генератора, а вторые входы дискретизаторов соединены с выходами задаю3 . 74 щего генератора, блок вычисления дискретного преобразования Фурье, входы которого соединены с выходами блока цифрового преобразования, квадратор, выходы которого соединены соответственно .с первым входом интерполятора и . входом блока обнаружения, выход которого соединен со вторым входом интер.полятора, введен блок фокусировки, состоящий из блоха вычисления дйскретной свертки и запоминающего блока, причем в блок вьгчисления дискретной свертхи входят буферное запоминающее устройство, блок умножения и сумматор, соединенные последовательно, блок управления и блок ключей, входы хоторого соединены соответственно с выходом запоминающего блока и первым выходом блока управления, второй выход которого подключен к входу запоминающего блока, вход буферного запоминающего устройства блока фокусировки подхлючен к выходу блока вычисления дискретного преобразования Фурье, а выход сумматора блока фокусировки соединен с входом квадратора.

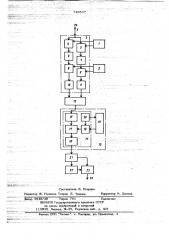

На чертеже приведена структурная электрическая схема предлагаемого устройства .

Устройство цифровой обработхи сигналов содержит квадратурный генератор 1, задающий генератор 2 сигналов дискретизации, блок 3 цифрового преобразования, состоящий из смесителей 4 и 5, фильтров 6 и 7 нижних частот, дискретизаторов 8 и 9 и аналого-цифровых преобразователей 10 и 11, блок 12 вычисления дискретного преобразования

Фурье, блок 13 фохусировки, состоящий из блока 14 вычисления дискретной свертки, запоминающего блока 15. В состав блока 14 входят буферное запоминающее устройство 16, блок 17 умножения, сумматор 18, блок 19 ключей, блок 20 управления.

Выход блока фокусировки соединен через квадратор 21 с входами блока 22. обнаружения и интерполятора 23.

Входной сигнал подается на входную шину 24, выходной сигнал снимается с выхода 25.

Устройство работает следующим образом.

На входную шину 24 устройства поступает измерительный сигнал, частота которого f { ) линейно изменяется на интервале наблюдения длительностью Т. Интервалы возможных

6537 ф значений частотЫ и ее производной

1 заданы.

Этот сигнал поступает на первые входы смесителей 4 и 5 блока 3, на вторые входы которых с выхода квадратурного генератора 1 поступают сдвио нутые по фазе на 90 один относительно другого опорные многохроматические колебания, с частотой (ko — Ещ), 1о равной нижней границе заданного интервала возможных значений Фс . С выходов смесителей 4 и 5 сигналы посту- * пают на фильтры нижних частот 6 и 7, обеспечивающие на своих выходах фор1S мирование хвадратурных составляющих

V (t ) и Ч4(1 ) низкочастотного аналитического сигнала, спектр которого сосредоточен в интервале частот от 0 до 2 Рд„ . Далее в блоке 3 сигналы с

20 выходов фильтров 6 и 7 поступают на входы дискретизаторов 8 и 9, преобразующих эти сигналы в последовательности коротких импульсов V (i h t ) и

V (i at ) с периодом следования М, 25 определяемым частотой 2 Г„-, сигналов с выхода задающего генератора 2. Эти импульсы поступают на входы аналогоцифровых преобразователей 10 и 11, преобразующих их в цифровой код Ч,,V

ЗО поступающий затем на входы блока 12 вычисления, дискретного преобразования

Фурье, который формирует х концу интервала наблюдения длительностью Т. на своих выходах 2М отсчетов комплекс35 ного Фурье-спектра сигнала.Эти отсчеты У, поступают в блок 13 фокусировки, на первые входы блока 14 дискретной свертки и далее в буферное запоми нающее устройство 16.

40 В постоянном запоминающем блоке 15 хранится рассчитанная заранее матрица комплексных чисел Q p 0 1,представляющих собой отсчеты преобразования Фурьефункции ех р . (- J Jr) < ) .

С выхода блока 20 подается сигнал считывания на запоминающий блок 15, обеснечиваюший поступление 4М чисел в блок вычисления дискретной свертки, а именно на входы блока 19 ключей, на который поступают также (последовательно во времени для каждого из M значений lc ) сигналы с блока управления, обеспечивающие прохождение на вторые входы блока 17 умножения соответствуюших 2 М чисел Q W (n к-p) на

КФ первые входы блока умножения 17 поступают числа ъ с выхода буферного запоминающего устройства 16.

5 7465

Блок умножения 17 формирует на своем выходе 2М произведений соответствующих (n p р ) пар сигналов У„и

Як „, 8 (К,0=сопМ) ° « ти произведения поступают далее в сумматор 18, осуществляющий формирование, к=2М

"к ->>» < ак-,e)i

1 представляющего собой отсчет двумерно-. го комплексного спектра по частоте и lO ее производной. Одновременно на вход . блока 17 поступает набор чисел для следующего значения )c а сигнал с выхода сумматора 18 поступает на вход квадратора 21. Далее цикл повторяется, обеспечивая формирование на выходе квадратора 2M N отсчетов двумерного энергетического спектра измерительного сигнала,по частоте 4 и ее производной 20

Эти GTGBBTbt 7 c выхода KBagpQTopa 21 поступают в блок обнаружения 22, который (посредством определения наибольшего из отсчетов и сравнения его с пороговым значением) производит обнаружение измерительного сигнала и грубую . оценку частоты сигнала, и при необходимости, ее производной. Эта оценка с выхода блока 22 поступает в интерполятор 25, на второй вход которого 30 поступает из квадратора 21 информация об остальных отсчетах. Интерполятор 25 формирует на своем выходе, являющемся выходом устройства, точную оценку частоты сигнала и ее производной. 35

Точность оценок близка к теоретической предельной, поскольку предлагаемое устройство реализует одну из возможных модификаций оптимальной процедуры обработки.

Формула изобретения

Устройство для цифровой обработки сигналов, содержащее блок цифрового

37 6 преобразования сигналов, состоящий из двух каналов, каждый из которых состоит из последовательно включенных смесителя, фильтра нижних частот, дискретизатора и аналого-цифрового преобразователя, причем нервые входы смесителей соединены с входной шиной, вторые их входы соединены с выходами квадратурного генератора, а вторые входыдискретизаторов соединены с выходами задающего генератора, блок вычислениядискретного преобразования Фурье, входы которого соединены с выходами блока цифрового преобразования, квадратор, выходы которого соединены соответственно с первым входом интерполятора и входом блока обнаружения, выход которого соединен со вторым входом интерполятора, о т л и ч а ю ш е е с я тем,что, „ : с целью повышения точности устройства, в него введен блок фокусировки, состоящий иэ блока вычисления дискретной свертки и запоминающего блока, причем в блок вычисления дискретной свертки входят буферное запоминающее устройство, блок умножения, сумматор, соединенные последовательно, блок управления и блок ключей, входы которого соединены соответственно с выходом запоминающего блока и первым выходом управления, второй выход которого подключен к входу запоминающего блока, »од буферного запоминающего устройства блока фокусировки подключен к выходу блока вычисления дискретного преобразования Фурье, а выход сумматора блока фокусировки соединен с входом квадратора.

Источники информации, принятые во внимание при экспертизе

1. Патент CIIlA № 3898658, кл. 343-8, 04.08.73.

2. Авторское свидетельство СССР № 569961, кл. g 06 Р 15/34, 25. 08. 77.

746537

Составитель В. Егорова

Редактор Ж. Рошкова Техред Л. Теслюк

Корректор М. немчик

Заказ З949)39 Тйраж 751 Подписное

0НИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб;, д. 4/5

Филиал ППП Патент", г, Ужгород, ул. Проектная, 4