Устройство для контроля цифровых блоков

Иллюстрации

Показать всеРеферат

тоСФ,„ ., пи ет;ит... ли ет . 4t

Союз Советскик

Социалистическими

Республик (1ц 746553

ИЗОБРЕТЕН ЙЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. с вид-ву— (22) Заявлено 03.05.78 (2! ) 2610553/18-2 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 07 07 80 Бюллетень №25 (51 ) М. Кл.

g06 Р) 15/46

3ооудеротввнный квинтет

СССР по лелем нзобретеннй н открытнй (53) УДК 621 3g6 (088. 8) Дата опубликования описания 09.07.80 (72) Автор изобретения

М. Г, Дубров (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

ЦИФРОВЫХ БЛОКОВ

Изобретение относится к вычислительной технике, в частности к устройствам тестового контроля логических схем и диагностики неисправйостей.

Известны устройства для контроля циф- 5 ровых блоков, содержащее блок ввода, блок сравнения, блок индикации, блок памяти (1) и (21

Недостатком устройств является малая степень автоматизации поиска неисправностей, так как при наличии большего числа неудачных исходов тестов просмотр словаря неисправностей с целью локализации неисправного элемента зани15 мает много времени.

Наиболее близким техническим решением к предлагаемому изобретению является устройство контроля цифровых блоков, содержащее последовательно соединенные блок управления, блок ввода, блок памяти, коммутатор, блох сравнения и регистры, подключенные к блоку ввода, а выходы блока управления соединены со

2 входами блоков памяти и сравнения и коммутатора (З) .

Однако это устройство сложно, так как содержит два многоразрядных регистра, разрядность которых равна числу неисправностей.

Белью предлагаемого изобретения является упрошение устройства при сохра-. нении высокой степени автоматизации поиска места неисправности (локализации места неисправности }.

Бель достигается тем, что устройство для контроля цифровых блоков содержащее блок ввода, первый и второй вы.ходы которого соединены соответственно с первыми входами блока памяти и блока управлениятсоединенного первым, вторым, третьим и четвертым выходами соответственно со входом блока ввода, со вторым входом блока памяти, первым входом блока сравнения и первым входом комм;утатора, первый и второй выходы блока памяти подключены соответственно ко вторым входам коммутатора и блова.

30

40

55

3 74655 ка сравнения, первый выход коммутатора соединен с третьим входом блока сравнения, выходы регистра со входами блока индикации, а третий вход и второй выход коммутатора являются соответст венно входом и выходом устройства, со5 держит блок переключения, первый вход которого соединен с третьим выходом блока ввода, второй вход- с пятым выходом блока управления, третий вход- 10 с выходом блока сравнения, первый выход блока переключения с единичными входами регистра, а второй выход - с нулевыми входами регистра.

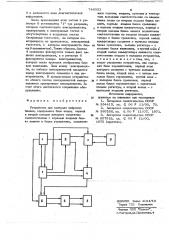

На чертеже изображена схема устройст- д5

Устройство содержит блок 1 ввода, блок 2 памяти, коммутатор 3, блок 4 сравнения, блок 5 индикации, регистр 6, блок 7 управления, блок 8 переключения и контролируемый блок 9.

Блок 1 ввода предназначен для ввода с перфоленты тестовой информации, информации с входных (выходных) контактов, информации о проверяемых неисправностях (перечень-проверяемых неисправностей), диагностической информации (номера неисправностей, проверяемых в каждом тесте) и командной информации.

Блок 2 памяти предназначен для хра- нения и выдачи через коммутатор 3 на блок 9 тестовой информации. Блок памяти 2 разделен на две зоны: в одной хранятся стимулы (набор подаваемой на входные контакты блоков), во второй— эталоны s(значенпя сигналов, которые должны появиться на выходах блока 9, если он исправлен).

Коммутатор 3 предназначен для коммутации внешних контактов блока 9, при этом входные контакты подключаются к выходам блока 2 памяти (к той части, где хранятся стимулы), выходные контакты подключаются ко входам блока 4 сравнения. Блок 5 индикации предназна чен для индикации номера неисправности.

В регистре 6 фиксируются номера обнаруженных неисправностей. Блок 8 переключения переключает диагностическую информацию на нулевые или единичные входы регистра 6.

Устройство работает следующим образом.

В ис.ходном состоянии блок 2 памяти и регистр 6 по командам с блока 7 установлены в нулевое состояние (цепи сброса не показаны). Вначале с блока 1 вводится информация с проверяемых нено

3 4. правностях и по командам с блока 7 через блок 8 записывается в регистр 6.

Информация о проверяемых неисправностях является перечнем неисправностей, проверяемых в блоке 9. Разрядность регистра 6 равна максимальному количеству проверяемых неисправностей блоков 9. При вводе информации о проверяемых неисправностях соответствующие разряды регистра 6 устанавливаются в

"1», -ый разряд регистра 6 устанавливается в 1", если -ая неисправность проверяется в данном объекте контроля. Поспе подготовки регистра 6 по командам с -блока 7 тестовая информация (стимулы и эталоны) записывается в блок 2. Стимулы из блока 2 памяти поступают через коммутатор 3 на входы блока 9, а эталоны на первые выходы блока 4 сравнения. Управление работой коммутатора 3 осуществляется по сит нилам из блока 7 управления. По результатам сравнения, если контролируемый блок исправлен, появляется высокий потенциал на выходе блока 4 сравнения..После подачи на входы блока 9 очередного набора по команде из блока

7 управления из блока 1 вводится диагностическая информация, которая через блок 8 поступает на установку в «О» разрядов регистра 6. Диагностическая информация представляет позиционный код, длина которого (разрядность) равна общему количеству проверяемых неисправ ностей. Каждому номеру неисправности из списка неисправностей соответствует ,один разряд позиционного кода, причем только в разрядах позиционного кода, соответствующих проверяемым в данном тесте неисправностям, записаны 1 .

Каждому тестовому набору соответствует своя диагностическая информация. Если в очередном тесте не обнаружены неисправности (на выходе блока сравнения—

"1"), то разряды регистра 6, соответствующие коду диагностической информации данного теста, устанавливаются в

0". Сигнал на выходе блока 4 сравна ния разрешает запись диагностической информации в регистр 6. Если же в очередном тесте обнаружена неисправность, то установление в "0" разрядов регистра 6 не происходит.

После ввода диагностической информации по командам с блока 7 управления в блок 2 памяти вводится следующий тест, который поступает затем на входы блока

5 7

9 и начинается ввод дйагностической информации.

После прохождения всех тестов в регистре 6 установлены 1" тех разрядов, которые соответствуют неисправностям, проверяемым в неисправных тестах и отсутствующие в исправных тестах (исправный тест-тест, на котором неисправность не проявляется, неисправный тест гест, в кагором неисправность блока 9 проявляется) . Таким образом, блоком, 4 сравнения фиксируется только факт наличия неисправности, а в регистре 6 фиксируются номера неисправностей, которые после проверки отображены блоком индикации. Зная номер неисправностй, по таблице неисправностей находятся номер неисправного элемента и вид неисправности. В предлагаемом устройстве из общего списка неисправностей вычеркиваются проверенные неисправности. За счет этого достигается сокращение оборудования.

Формула изобретения

Устройство для контроля цифровых блоков, содержащее блок ввода, первый и второй выходы которого соединены соответственно с первыми входами блэка памяти и блока управления, соединен46553 6 ного первым, вторым, третьим и четвертым выходами соответственно со входом, блока ввода со вторым входом блока памяти, первым входом блока сравнения и первым входом коммутатора, первый и второй выходы блока памяти подключены соответственно ко вторым входам коммутатора и блока сравнения, первый выход коммутатора соединен с третьим входом

1О блока сравнения, выходы регистра - с входами блока индикации, атретий вход и второй выход коммутатора являвлся соответственно входом и выходом устройства, о т л и ч а ю ш е е с я тем, что, с

15 целью упрощения устройства, оно содер-. жит блок переключения, первый вход которого соединен с третьим выходом блока ввода, второй вход - с пятым выходом блока управления, третий вход—

2О с выходом блока сравнения, первый выход блока переключения с единичным входом регистра, а второй выход - c нулевыми входами регистра, Источники информации, 25 принятые во внимание при экспертизе

1. Авторское свидетельство СССР

¹ 354415, кл. G 06 F 11/00, 70.

2. Авторское свидетельство СССР № 390526, кл. Qi 06 Р 11/07, 1971.

g0 3. Авторское свидетельство СССР № 607218, кл. -(06 F 1 1/00, 1975 (прототип).

UHHHIIH Заказ 4104/1B

Тираж 751 Подписное

Филиал ППП "Патент, r.Óæãîðoä,óë,ÏpîåêòHàÿ,4