Вычислительное устройство для первичной обработки информации

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 74656Я

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскин

Социалист ическик

Республик (6) ) Дополнительное к авт. свид-ву— (22) Заявлено 21.04.78 (2! ) 2606620/18-24 (5! ) М. Кл.

G 06 G 7/12

G 06 Т 3/00 с присоединением заявки ¹вЂ”

Гасударственный камнтет (23) Приоритет до делам нзобретеннй н открытий

Опубликовано 07. 07. 80. Бюллетень № 25 (53) УД К 681. .335(088.8) Дата опубликования описания 08,07.80 (72) А вторы изобретения

В. H. Лапенко, Н. Н. Шишкевич и . Г. Г, Золотова

Московский институт электронной техники (7l) Заявитель (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ Пт.. РВИЧНОЙ

ОБРАБОТКИ ИНФОРМАБИИ

Предлагаемое вычислительное устройство относится к вычислительной технике, в частности может быть использовано в устройствах преобразования аналоговых величин в цифровой код.

Известны устройства, используемые

5 для первичной обработки информации путем сжатия динамического диапазона при измерении амплитуд импульсов. Сжатие динамического диапазона при обработке одиночных импульсов необходимо вследствие узкого динамического диапазона детекторов, в частности. пиковых. НаиболЬшее распространение для э"тих целей получюти логарифмические усилители (I) .

Из известных вычислительных уст ройств наиболее близким к предложенному является вычислительное устройство для первичной обработки информации, содержащее тз усилительных каскадов, соединенных выходами со входами сумматора (n-1) элементов задержки, каждый из которых включен между соответствующими предыдущим и последующим усилительными каскадами, пиковый детектор, ключ, два пороговых блока и блок выбора порядка 12)

Недостатком этого устройства является то, что для определения параметров импульсов большого динамического диапазона (120-160 дБ) требуется большое число каскадов усиления. Например, для измерения сигналов с динамическим диапазоном в 120 дБ при разрешающей способности пикового детектора 10 дБ необходимо 12 усилительных каскадов ,с коэффициентом усиления 10 дБ и, соответственно, 11 элементов. задержки,что очень громоздко и приводит к увеличению габаритно-весовых характеристик устройства.

Бель изобретения — уменьшение объ ма оборудования при обработке сигналов большого динамического диапазона.

Поставленная цель достигается тем, что в вычислительное устройство, содержащее ет усилительных каскадов,(rl-1) 3: 746569 элементов задержки, каждый из которых капами 4 включены (включен между соответствующими предыду тельных элементов 5 щим и последующим усилительными каскада усилительных касквдо ми, ипервый сумматор, причемвыходы усили» каскада 4 подключень

5 тельных каскадов подключены к входам пер- тора 6, соединенного

". вбго сумматора, введены второй сумма- блока 7 выборки и хр тор и (дополнительных усилительных кас- Блок 7 выборки и кадов, последовательно соединенных друг с другом через (k -1) дополнительных элементов задержки, вход устройства соединен с одним из входов первого сумматора, выход первого сумматора соединен со входом первого дополнительного усилительного каскада и с одним из входов второго сумматора, другие входы которого подключены к выходам других дополнительных усилительных каскадов, выход второго сумматора связан со входом блока выборки и хранения сигнала, аналоговый выход которого является" аналоговым выходом устройства, а группа разрядных выходов — цифровым выходом устройства.

При этом блок выборки и хранения сигнала содержит элемент задержки, ключ, пиковый детектор, пороговый элемент, узел управления и счетчик, причем выход эл мента задержки через ключ подключен ко входу пикового детектора, один выход порогового элемента соединен со счетным входом счетчика, а другой выход соединен с входом узла управления, первый и второй выходы которого подключены ко входам ключа и пикового детектора, третий и четвертый . выходы узла управления соединены с управляющими входами счетчика, входы элемента задержки и порогового элемента подключены ко входу блока выборки и хранения сигнала, выход пикового детектора является аналоговым выходом, а группа разрядных выходов счетчика — группой разрядных выходов блока выборки и хранения сигнала.

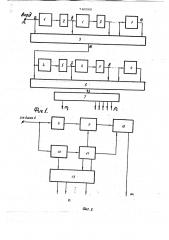

На фиг. l приведена структурная схема вычислительного устройства для первичной обработки информации, на фиг. 2функциональная схема блока выборки и хранения сигнала, нв фиг. 3 — временная диаграмма работы устройства...

Вычислительное устройство (фиг. 1) содержит г1 усилительных каскадов 1, последовательно соединенных друг с другом через элементы 2 задержки, входы усилительных каскадов 1 и выход rf го квСкада 1 подключены ко входам сумматора 3, соединенного выходом с первым из (дополнительных усилительных каскадов 4, между соответствующим предыдущим и последующим усилительными кас»

Р— 1) дополнизадержки, входы в 4 и выход K --го

r ко входам .суммавыходом со входом анения сигнала. хранения сигнала (фиг, 2) содержит элемент 8 задержки, ключ 9, пороговый элемент 10, узел

10 11 управления, пиковый детектор «2 и двоичный счетчик 13, причем вход элемента 8 задержки и вход порогового эле1 мента 10 являются входом блока 7 выборки и хранения сигнала, Один выход по15 рогового элемента 10 подключен к счетному входу счетчика 13, другой выход через блок 11 соединен со входом ключа

9 и со входоМ пикового детектора 12, выход последнего является аналоговым вы20 ходом блока 7, а группа разрядных выходов счетчика 13 является группой разрядных выходов блока 7, выход элемента 8 задержки через ключ 9 подклюl чен ко входу пикового детектора 12.

Вычислительное устройство для первичной обработки информации работает следующим образом.

Входной сигнал одновременно посту30 пает на первый усилительный каскад 1, на первый дополнительный усилительный каскад 4 и на вход сумматора 6 через сумматор 3 (фиг. 3a) и усиливается последующими усилительными каскадами

1 и 4. С выхода первого элемента 5 задержки у силенный в Кл раз (фиг, 34) импульс поступает на вход сумматора 6 через время, равное ч: зо ., а с выхода g -го каскада 4 — через (Р - «) < q g40

Время задержки т;,,, . элемента 5 задержки желательно выбирать больше длительности измеряемого импульса. С выхода первого элемента 2 задержки усиленный в к =кл раз импульс (фиг.З ) е+л поступает йа вход сумматора 3 через времяT =(Ю +1) ь3д, а с выхода д -го усилительйого каскада 1- через время, равное (O/-1) T>, с выхода сумматора 3 усиленные в к,к,к "

50 импульсы последовательно поступают на сумматор 6 и цепочку усилительных каскадов 4 (фиг.Зж). На выходе сумматора 6 получается последовательность равномерно разнесенных .импульсов (фиг. ЗР)

r причем амплитуды двух ближайших отли55 чвются в кл раз, Первый пришедший во времени импульс имеет минимальную по ! величинс амплитуду равную Ов х ампли-i

1 У туда второго пришедшего импульса

2. Устройство по п. 1, о т л и ч аю щ е е с я тем, что блок выборки и хранения сигнала содержит элемент запержки, ключ, пиковый детектор, пороговый элемент, узел управления и счетчик„ причем выход элемента задержки через ключ подключен ко входу пикового детектора, опии выход порогового элемента соепинен со счетным входом счетчика, а другой выход соединен с входом узла

5 74656 !

О „к, третьего — 0в к °" (0+1)-го

О,„. (а+2)-г -О,„. к„"" .. i-лепнего у . n(P+c)+Р

Эта пачка импульсов поступает на пороговый элемент 10 блока 7, который срабатывает при приходе импульса с амплитупой, превышающей установленный порог срабатывания U равный нижней границе пинамического диапазона пикового детектора (фиг. Зо) и выпает сигнал на узел 11 управления, который обнуляет пиковый детектор 12, записывает в счетчик 13 число на единицу большее, 1 чем количество импульсов в пачке, и разблокирует счетный вход счетчика 13 5 на время, равное (+ 1+0+ rt j с q q. В счетчике 13 записанное число по приходу импульсов с порогового элемента 10 начнет уменьшаться по тех пор, пока будут поступать импульсы с порогового элемен- 20 та 10 на счетный вход, т.е. пока измеряемый сигнал не дойдет по послепнего усилительного каскада. После прихода последнего импульса из пачки счетчик

13 блокируется. Задержанный на время обработки сигнала в элементе 8 задержки измеряемый сигнал проходит через ключ 9, открытый на это время узлом 11 управления, на пиковый детектор 12, гпе он и запоминается.

Выходной сигнал представляется в полулогарифмическом виде, гпе мантисса т ; равна выходному напряжению на пиковом детекторе 12, а поряпок Р; снимается с выходов счетчика 13. Таким образом, величина входного сигнала U.э, равна:

9 6 ! элементов задержки, каждый из которых

I включен между соответствующими пре-! дыпущим и последующим усилительными каскадами, и первый сумматор, причем выходы усилительных каскадов подключены к входам первого сумматора, о т,— л и ч а ю щ е е с я тем, что с целью уменьшения объема оборудования при обработке сигналов большого динамического пиапазона,в него введены второй сумматор и С дополнительных усилительных каскадов, последовательно соединенных друг с другом через (Р -1) дополнительных элементов эапержки, вход устройства соединен с одним из входов первого сумматора, выход первого сумматора соединен со входом первого дополнительного усилительного каскада и с одним иэ вхопов второго сумматора, другие входы которого подключены к выходам других дополнительных усилительных каскадов, выход второго сумматора связан со вхо пом блока выборки и хранения сигнала, аналоговый выход которого является аналоговым выходом устройства, а группа разрядных выходов- цифровым выходом устройства, 40

Благопаря введению новых узлов и связей и использованию усилительных каскапов с разными коэффициентами усиления, а именно: с коэффициентами усиления, соответствующими динамическому пиапазону пикового детектора и в несколько раз превышающими его, объем обо- рупования значительно уменьшается без ухудшения точности. Ероме того, при использовании предлагаемого устройства

50 значительно упрощается его схема, сни жается стоимость и улучшаются габаритно-весовые характеристики.

Формула изобретения

1. Вычислительное устройство пля пер.вичной обработки информации, содержа) щее ll усилительных каскапов, (n -1) управления, первый и второй выходы которого попключены ко входам ключа и пикового детектора, третий и четвертый выходы узла управления соединены с управляюшими входами счетчика, входы элемента задержки и порогового элемента подключены ко входу блока выборки и хранения сигнала, выход пикового детектора является аналоговым выходом, а группа разряпных выходов счетчика— группой разрядных выходов блока выборки и хранения сигнала.

Источники информации, принятые во внимание при экспертизе

1. Патент ClIIA N 3662274, кл. 329-192, опублик. 1972.

2. Авторское свидетельство СССР по заявке М., 2430928, кл. G 06 5 7/12, 1976 (прототип).

746569

Составитель Шелинова

Техред Ж. Кастелевич Корректор С. Шекмар

Редактор Т. Портная

Заказ 4106/19

Чу раж 751 П одписное

11НИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д..4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4