Частотно-импульсное интегрирующее устройство

Иллюстрации

Показать всеРеферат

Союз Соеетскик

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (и 7465?7

Ф

gi=— - - г (6l ) Дополнительное к авт. свид-ву -, (22)Заявлено 19,04.78 (21) 2606615/18-24 (5! )М. Кл. 06 Cj 7/18 с присоединением заявки.%

Гасударственный комитет

СССР

{23) Приоритет ао делам нзооретений н открытий

Опубликовано 07 07.80. Бюллетень № 25

Дата опубликования описания 08.07.80 (53) УДК 681. ,327.66 (088.8) (72) Авторы изобретения

Н, Л, Москвитин и П. В. Соловов

Рязанский радиотехнический институт (71) Заявитель (54) ЧАСТОТНОИМПУЛЬСНОЕ ИНТЕГРИРУЮШЕЕ

УСТРОЙСТВО

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении гибридных вычислительных устройств.

Известно частотно-импульсное интегрирующее устройство, содержащее счетчик

5 и блок формирования сигналов начала и конца интегрирования 11

Недостатком устройства является его низкая точность при случайном расположении сигналов начала и конца интегрирования.

Наиболее близким техническим реше-.

/ нием к предлагаемому является частотно-импульсное интегрирующее устройство, содержащее счетчик, элементы ИЛИ и

И и триггеры $2)

Недостатком этого устройства также. является низкая точность интегрирования. 20

Цель изобретения — повышение точности интегрирования.

Поставленная цель достигается тем, что устройство содержит сумматор, два

2 блока элементов И и выходной регистр, первые входы первого, четвертого и пятого элементов,ИЛИ соединены с выходом знакового разряда сумматора и первым входом первого элемента И, второй вход которого соединен с единичным выходом третьего триггера и первым входом второго элемента И, второй вход которого соединен с первым входом тре- тьего и четвертого элементов И, а вы- ход — с первым входом второго элемента ИЛИ, второй вход которого соединен со входом установки в 1 второго триггера, а выход - со входом установки в 1 первого триггера, вход установки в "0" первого триггера соединен с выходом первого элемента 9ЛИ, второй вход которого соединен с первым входом третьего элемента ИЛИ, четвертым входом пятого элемента ИЛИ и вторым входом четвертого элемента ИЛИ, выход которого соединен со входом установки в 0 третьего триггера, вход установки в "1 которого соединен с

20

3 7 третьим входом пятого элемента ИЛИ, "выход которого соединен со входом установки в "0" сумматора, второй вход пятого элемента ИЛИ соединен с первыми входами первого блока элементов

И и выходом третьего элемента И, второй вход которого соединен с нулевым выходом третьего триггера, выход первого элемента И соединен со вторым входом третьего элемента ИЛИ, выход которого соединен со входом установки в . 0" второго триггера, единичный выход второго триггера соединен со вторым входом четвертого элемента И, выход которого соединен с суммирующим входом счетчика, вычитающий вход счетчика соединен с первыми входами второго блока элементов И и выходом шестого элемента, И, первый вход которого соецинен с единичным выходом первого триггера, нулевой выход первого триггера соединен с первым входом пятого элемента И, второй вход которого соединен со вторым входом шестого элемента- И, & выход соединен со входом младшего разряда сумматора, выходы старших разрядов которого последовательно через первый блок элементов И, выходной регистр и второй блок элементов И соединены с вычитающими входами сумматора.

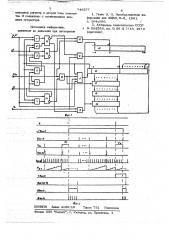

На фиг. 1 изображена блок-схема предлагаемого устройства, на фиг, 2— временные диаграммы, поясняющие его работу.

Устройство содержит элементы ИЛИ

1-5, элементы И 6 - 11, триггеры

12 — 14, счетчик 15, сумматор 16, два блока 17 и 18 элементов И и выходной регистр 19, Первые входы элементов ИЛИ 1, 4 и

5 соединены с входом элемента И 6, второй вход которого соединен с первым входом элементов И 10 и 11, а выход соединен с nepsbw входом элемента ИЛИ.

2, второй вход которого соединен со входом установки в "1" триггера 13, а выход подан на вход установки в 1 триггера 12, вход установки в "0" которого соединен с выходом элемента

ИЛИ 1, у которогo второй вход ..соединен с первым входом элемента ИЛИ 3

° четвертым входом. элемента ИЛИ 5 и вторым входом элемента ИЛИ 4, выход которого соединен со входом установки в 0" триггера 14. Единичный выход триггера 14 соединен со входом элемента И 6, а вход установки в 1"— с третьим входом элемента ИЛИ 5, вы46577 4. ход которого соединен со входом установки в "О» сумматора 16. Второй вход, элемента ИЛИ 5 соединен с первыми входами блока 17 элементов И и выходом элемента И 9, второй вход которого соединен с нулевым выходом триггера 14. Выход элемента И 6 соеди1 нен со вторым входом элемента ИЛИ 3, выход которого соединен со входом уста10 ковки в ".0" триггера 13, единичный выход которого соединен со вторым входом элемента И 11, выход которого соединен с суммирующим входом счетчика 15, вычитающий вход которого соединен с первыми входами блока элементов И 18 и выходом элемента И 9, первый вход которого соединен с единичным выходом триггера 12, нулевой выход которого соединен с первым входом элемента И 8, у которого второй вход соединен со вторым входом элемента И 9, а выход соединен со входом младшего разряда сумматора 16, выходы старших разрядов которого последовательно через первый

25 блок 17 элементов И, выходной регистр

19 и второй блок 18 элементов И соединены с вычитакщими входами сумма-Тра.

Устройство работает следующим образом.

Входной импульс Н" переводит триг1 гер 13 и, через элемент ИЛИ 2, триггер 12 в состояние "1 . С единичного выхода триггера 13 входная частота Рвх проходит через элемент ИЛИ 11 на вход младшего разряда счетчика 15. Каждый импульс частоты, накопленный в счетчике 15, несет информацию о всем предыдушем периоде входной частогы, При этом

40 тк реализуется операция й= 5., g „(6)oil Уточ.— тм пение величины интеграла на концах интервала интегрирования определяется по формуле ай =-ЮТвх)=-> вх Измерение

45 величины z и Твхосуществляется подсчетом в сумматоре 16 числа импульсов частоты заполнения о измеряемых интервалов с и Тв . Накопленный за период частоты э код периода Твх по концу этого периода (импульсу вх ) переписывается в регистр 19 через элементы И 17. По концу переписи через элемент ИЛИ 5 сумматор 16 обнуляется

Таким образом, по концу каждого периода входной частоты в регистре 19 устанавливается код предыдущего периода, который хранится в нем до конца следующего периода. Импульс начала интервала интегрирования переводит триггер 13 и через

5 7 элемент ИЛИ 2 " триггер 12 в 1". По, сигналу «1» запрещается прохождение частоты Ро измерения Ъ, ТВХ через блок 18 элементов И на сумматор 16.

В сумматоре 16 пс сигналу начала интервала интегрирования "Н" оказывается код ® 1. По сигналу "1" вспомогательная частота Р через элемент И 9 поступает на элементы И вычитания кода

М регистра 19 из дополнительных младших разрядов сумматора 16, Одновременно импульсы частоты Ро поступают на вы итающий вход младшего разряда счетчика 15. Очевидно, что число импульсов частоты Р<, поступающих на вычитающий вход счетчика 15, равно числу вычитаний v — Тв т.е, равно частотному ог деления ч;/ Te . Поступление частотыГ заканчивается по концу деления — переполнению сумматора 16, т.е. по появлению сигнала смены знака сумматора. При-. этом сигнал изменения знака сумматора

16 через элемент ИЛИ 1 ставит триггер

12 в состояние "0", тем самым вновь разрешается измерение интервалов г и T „. Сигнал конца интервала интегрирования "К ставит триггер 14 в состояние "1", и через элемент ИЛИ 5 устанавливает в "0" сумматор 16. От момента "К" до очередного импульса частоты в сумматоре 16 накапливается значение с 2. Условие "1 триггера 14 запрещает поступление очередного импульса частоты F на перепись кода Йч= в регистре 19 и установку в "0" сумматора

16. Очередной импульс частоты Ps ÷e-: рез элемент И 7 и элемент ИЛИ 2 ставит триггер 12 в "1" и тем самым начинает этап определения ч= т х

46577 6

Формула изобретения

Частотно-импульсное интегрирующее устройство, содержащее счетчик, элементы ИЛИ и И и триггеры, о т л и

5 ч а ю щ е е с я тем, что, с целью повышения точности интегрирования, оно содержит сумматор, два блока элементов

И и выходной регистр, первые входы первого, четвертого и пятого элементов ИЛИ

По концу деления сигнал смены знака . сумматора 16, устанавливает через элемент ИЛИ 1 триггер 12 в "О, через элемент И 6 и элемент ИЛИ 3 триггер

13 в "0" через элемент ИЛИ 4 триггер 14 в "0" через элемент ИЛИ 5 сумматор 16 в "0 "1 Устройство подготавливается к интегрированию входной частоты F на новом интервале интеГрйрования.

Использование предлагаемого устройства позволяет значительно повысить точ- ность интегрирования частотных сигналов.

Его применение наиболее оправдано при низких входных частотах (что характерно для большинства частотных датчиков) и малых интервалах интегрирования. соединены с выходом знакового разряда сумматора и первым входом первого элемента И, второй вход которого соединен с единичным выходом третьего триггера и первым входом второго элемента И, второй вход которого соединен с первым входом третьего и четвертого элементов

И, а выход — с первым вхоцом второго элемента ИЛИ, второй вход которого соеl1HBeH со вход м ycTGHDBKH в 1" второго триггера, а выход — со входом установки"в "1" первого триггера, вход установки в "0" первого триггера соединен с выходом первого элемента ИЛИ, второй вход которого соединен с первым входом третьего элемента ИЛИ, четвертым входом пятого элемента ИЛИ и втс» рым входом четвертого элемента ИЛИ, выход которого соединен со входом установки в "0 третьего триггера, вход установки в "1" которого соединен с третьим входом пятого элемента ИЛИ, выход которого соединен со входом установки в "0 сумматора, второй вход

35 . пятого элемента ИЛИ соединен с первыми входами первого блока элементов И и выходом третьего элемента И, второй вход которого соединен с нулевым вьходом третьего триггера, выход первого элемента И соединен со вторым входом третьего элемента ИЛИ, выход которого соединен со входом установки в "0" второго триггера, единичный выход второго триггера соединен со вто4 рым входом четвертого элемента И, выход которого соединен с суммирующим входом счетчика, вычитающий блок счеь чика соединен с первыми входами второго блока элементов И и выходом шестого элемента И, первый вход которого соединен с единичным выходом первого триггера, нулевой выход первого триггера соединен с первым входом пятого элемента И, второй вход которого соединен со вторым входом шестого элемента И, а выход соединен со входом младшего разряда сумматора, выходы старших разрядов которого последовательно через первый блок элементов И, .746577 выходной ре истр и второй блок элемен:-" тов И соединены с вычитшощими входами сумматора, <4 Вы». В

° ° °

8и». й

° ° °

1 ° Ф лбы».9

Иа». В б м Ф

Фиг

ЦНИИПИ Заказ 4106/19 Тираж 751 Подписное

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4

Источники информации,. принятые во внимание при экспертизе

1. аттис Э. П. Преобразователи информации для ЭЦВМ,М-Л., 1961, 1 64-.,166.

2. Авторское свидетельство СССР

5 М 503358, кл. G 06 G 7/18, 1974 (прототип),