Устройство для преобразования "перемещение-код-фаза

Иллюстрации

Показать всеРеферат

н)-".1 :" )" т.- . >, я .ФЫ!

Ь

О П И А Н N E (»)746653

Союз Советскмх

Соцмалмстмческмв

Реслублмк

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 24.04.78 (21) 2606552/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл. б 08 С 9/00

Н 03 К 5/00

Государственный комитет

СССР

Опубликовано 07.07.80. Бюллетень № 25 (53) УДК 621.398 (088.8) 10 делам иэобретеиий и открытий

Дата опубликования описания 17,07.80

). е мФ Ф ъ 4йтъ)))% ь% ю и х4)) и

В. М. Буянкин, Д. И. Вышецкий, И. С. Гутис, А. Л. Корбут, В. Г. Полетаев, А. И. Соловьев, А. С. Шаталов, Ю. А. Шаталов и В. А, Яковлев (72) Авторы изобретения

Ордена Трудового Красного Знамени экспериментальный научноисследовательский институт металлорежущих станков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

ПЕРЕМЕЩЕНИЕ-КОД-ФАЗА

Изобретение относится к автоматике и вычислительной технике, в частности, к об. ласти числового программного управления и может быть использовано для построения систем числового программного управления станками.

Известно импульсно-фазовое устройство для программного управления, в котором электромеханический датчик обратной связи по положению работает в фазовом режиме 111.

Недостаток известного импульсно-фазового устройства — низкая точность.

Наиболее близким техническим решением к предлагаемому является устройство для преобразования перемещение-код-фаза, содержащее преобразователь напряжение11 частота, последовательно соединенные реверсивиый счетчик н первый сумматор и последовательно соединенные генератор импульсов, опорный делитель частоты, второй сумматор, первый логический блок, блок ключей, датчик перемещения, фильтр, демо- 20 .дулятор, первый интегратор, второй выход опорного делителя частоты соединен со вторым входом демодулятора, третий выход

2 опорного делителя частоты соединен со вторым входом первого сумматора, второй выход реверсивного счетчика соединен со вторым входом второго сумматора, выходы первого сумматора соединены с другими входами первого логического блока 121.

Недостатком известного устройства является наличие-ошибки по ускорению и неоднозначность отсчета младшего разряда кода, снимаемого с устройства в статическом режиме и в режиме малой скорости измеряемого перемещения.

Цель изобретения заключается в повышении точности работы устройства.

Эта цель достигается тем, что в устройство введены второй логический блок и последовательно соединенные второй интегратор и третий сумматор, выход которого через последовательно соединенные преобразователь напряжение-частота и второй логический блок соединен со входами реверсивного счетчика, с третьим входом первого сумматора и с третьим входом второго сумматора, а выход демодулятора соединен со вторым входом третьего сумматора, выход первого интегратора соединен со входом второго ин746653

1$

2О

2$ о

Формула изобретения

$0

$$ тегратора и с третьим входом третьего сум- матора.

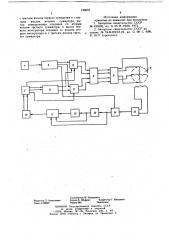

На чертеже приведена блок-схема пред- лагаемого устройства для преобразования перемещение-код-фаза, Устройство содержит генератор 1 импульсов, опорный делитель 2 частоты, первый сумматор 3, первый логический блок 4, блок

5 ключей, датчик 6 перемещения, второй логический блок 7, реверсивный счетчик 8, второй сумматор 9, преобразователь 10 напряжение-частота, третий сумматор 11, первый интегратор !2, второй интегратор 13, демодулятор 14, фильтр 15.

Устройство работает следующим образом.

Импульсы тактовой частоты от генератора 1 импульсов заполняют опорный делитель 2. На входы первого сумматора 3 информация от опорного делителя 2 и реверсивного счетчика 8 поступает в прямых кодах. На входы второго сумматора 9 информация от опорного делителя 2 поступает в прямом коде, а от реверсивного счетчика 8в обратном, Модулированные по фазе прямоугольные сигналы с выходов первого и второго сумматоров 3 и 9 через первый логический блок 4, формирующий две последовательности чередующихся раэнополярных широтно-модулированных прямоугольных импульсов, поступают на блок 5 ключей, выходы которого соединены с входными обмотками датчика 6 перемещения.

Выходной сигнал с датчика 6 через фильтр 15 поступает на демодулятор 14.

На выходе демодулятора 14 формируется напряжение рассогласования, поступающее на вход первого интегратора 12. Выходное напряжение первого интегратора 12, пропорциональное ускорению измеряемого перемещения, поступает на вход второго интегратора 13, на выходе которого формируется напряжение; пропорциональное скорости измеряемого перемещения, Выходные напряжения демодулятора 14, первого интегратора 12 и второго интегратора 13 суммируются на третьем сумматоре

11 с соответствующими масштабными коэффициентами, обеспечивающими устойчивость, точность и быстродействие устройства для преобразования перемещение-код-фаза, Выходное -напряжение третьего сумматора

11 поступает на .вход преобразователя 10 напряжение-частота, на одном выходе которого формируется последовательность импульсов при положительной полярности входного сигнала, а на другом — при отрицательной полярности этого сигнала. Эти импульсы поступают на входы второго логического блока 7. При вращении входного вала датчика 6 перемещения на выходе третьего сумматора 11 формируется сигнал, полярность которого зависит от направления вра. щения вала датчика 6 перемещения. При высокой скорости перемещения импульсы, формируемые преобразователем напряжениечаст л поступают через второй логический блок 7 на реверсивный счетчик 8. При неподвижном вале датчика 6 перемещения импульсы на выходах преобразователя 10 на пряжение-частота чередуются. Второй логический блок 7 не пропускает такие чередующиеся импульсы на входы реверсивного счетчика 8, а формирует взаимно инверсные чередующиеся логические уровни напряжений, поступающих на входы переноса в младшие разряды первого и второго сумматоров

3 и 9, что приводит к небольшим изменениям фаз прямоугольных сигналов на выходах этих сумматоров. Поэтому устройство остается замкнутым по цепи обратной связи, несмотря на. то, что информация, содержащаяся в реверсивном счетчике 8 при этом не изменяется. В связи с этим даже при малых скоростях измеряемого перемещения отсутствует неоднозначность преобразования перемещение-код, несмотря на то; что устройство в целом находится в режиме малых автоколебаний.

Использование новых элементов — второго интегратора, третьего сумматора и второго логического блока — выгодно отличает предлагаемое устройство от известных, так как указанные элементы позволяют уменьшить составляющие погрешности преобразования перемещение-код по ускорению и скорости, а также устранить неоднозначность считывания информации в статическом режиме, что позволяет существенно повысить точность работы следящих систем, в которых предлагаемое устройство будет использовано в качестве преобразователя обратной связи по положению..

Устройство для преобразования перемещение-код-фаза, содержащее преобразователь напряжение-частота, последовательно соединенные реверсивный счетчик и первый сумматор и последовательно соединенные генератор импульсов, опорный делитель частоты, второй сумматор, первый логический .блок, блок ключей, датчик перемещения, фильтр, демодулятор, первый интегратор, второй выход опорного делителя частоты соединен со вторым входом демодулятора, третий выход опорного делителя частоты соединен со вторым входом первого сумматора, второй выход реверсивного счетчика соединен со вторым входом второго сумматора, выходы первого сумматора соединены с другими входами первого логического блока, отличающееся тем, что, с целью повышения точности устройства, в него .введены второй логический блок и последовательно соединенные второй интегратор и третий сум« матор, выход которого через последовательно соединенные преобразователь напряжеwe-частота и второй логический блок соединен со входами реверсивного счетчика, 746653

Составитель И. Назаркина

Техред К. Шуфрич Корректор Г. Назарова

Тираж 682 . Подписное

UHHHllH Государственного комитета СССР по делам изобретений и .открытий

I 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4)5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор Л. Алексеенко

Заказ 4108/20 с третьим входом первого сумматора и с третьим входом второго сумматора, выход демодулятора соединен со вторым входом третьего сумматора, а выход первого интегратора соединен со входом второго интегратора и с третьим входом третьего сумматора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 435505, кл. G 05 В 19/36, 1972.

2. Авторское свидетельство СССР по заявке № 2444424/18-24, кл. G 08 С 9/00, 31.10.77 (прототип).