Устройство для передачи и приема дискретных сигналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ол 746668

- -%янез Соеетскик Социалистическими

Республик з

П т Й РЩ (5!)М. KII. (б1) Дополнительное к авт. свид-ву 9557403 (22) Заявлено 130278 (21) 2581947/18-24

С 08 С 19/28 с присоединением заявки ¹

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 070780. Бюллетень. Мо 25

Дата опубликования описания 070780 (53) УД (621. 374. 33 (088.8) (72) Авторы изобретения

Ю.В.Сулимов и Ф.Г.Фомичев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕИА ДИСКРЕТНЫХ

СИГНАЛОВ

Изобретение относится к технике передачи дискретных сигналов, предназначено для повышения достоверности передачи дискретной инФормации по дуплексным каналам .связи в условиях воздействия помех.

По основному авт. свид. 9557403 известно устройство для передачи и приема дискретных сигналов, содержащее переключатель, первый вход которого подключен к первому входу устройства, выход соединен с входом кодирующего блока и входом первого накопителя — повторителя, выход которого подключен ко второму входу 15 персключателя, первый выход кодирующего блока соединен с входом первого блока сложения, выход которого под ключен к первому выходу устройства,,второй вход кодирующего блока соеди- 20 нен с входом первого элемента задержки, второй вход устройства подключен к первому входу второго блока. сложения и к входу декодирующего блока, первый выход которого соединен с пер-2 вым входом второго накопителя — повторителя, второй выход — с вторым входом второго блока сложения и через второй элемент задержки — с вторым входом первого блока сложения, 30 третий выход — c первым входом и выходом элемента памяти и входом счетчика, первый выход которого соединен с вторым входом элемента памяти, второй выход — с вторым входом второго накопителя-повторителя, выход которо- го подключен к второму выходу устройства, а третий выход счетчика соединен с третьим входом переключателя, первые входы каждого блока сравнения подключены к соответствующим выходам первого элемента задержки, вторые входы объединены и соединены с выходом второго блока сложения, выход каждого блока сравнения подключен к входу соответствующего регистра и к первому входу соответствующего элемента управления, выход каждого регистра соединен с входами блоков памяти, выход каждого блока памяти подключен к второму входу соответствующего элемента управления, выходы элементов управления объединены и соединены с третьим выходом декодирующего блока (1)

Устройство обладает недостаточно высокой надежностью и осуществляет помехозащищенную передачу и прием дискретных сигналов лишь при условии согласования величины задержки сигна746668 лов в первом элементе задержки с величиной аппаратурных-и канальных запаздываний в прохождении сигналов по прямому и обратному каналам связи.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что в устройство, введены элемент ИЛИ, элементы И, триггер, хронизатор передачи и хронизатор приема, вход которого соединен с канальным входом устройства, первый и второй выходы хронизатора приема соединены соответственно с первыми входами первоговторого элементов Ии третьего-четвертого элементов И, первый выход хронизатора передачи соединен с вторы-. ми входами второго и четвертого элементов И, выходы которых соединены с входами триггера, выходы триггера подключены к вторым входам первого и третьего элементов И, выходы которых соединены с входами элемента ИЛИ, первый и второй элементы задержки выполнены в виде последовательно соединенных входного регистра, блока элементов И и выходного регистра, входы входных регистров соединены с входами элементов задержки, выходы выходных регистров подключены к выходам элементов задержки, управляющие входы блока элементов И подключены к выходу элемента ИЛИ, тактовые входы входного регистра первого элемента задержки и выходного регистра второго элеМента задержки соединены с вторым выходом хронизатора передачи, тактовые входы выходного регистра первого элемента задержки и входного регистра второго элемента задержки соединены с третьим выходом хронизатора приема.

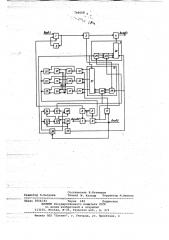

На чертеже изображено предлагаемое устройство.

Устройство содержит переключатель

1, первый накопитель-повторитель 2, кодирующий блок 3, первый блок 4 сложения, второй элемент задержки

5, счетчик 6, второй накопительповторитель 7, элемент 8 памяти, декодирующий блок 9, первый элемент

10 задержки, второй блок 11 сложения, блоки 12-14 сравнения, регистры 15-17 блоки 18-20 памяти, элементы 21-23 управления; элемент 5 задержки состоит из входного регистра 24, блока элементов И 25, выходного- регистра

26ф элемент 10 задержки состоит из выходного регистра 27, блока элементов И 28, входного регистра 29. В состав устройства также входят .первый элемент И 30, второй элемент

И 31, элемент ИЛИ 32, триггер 33, третий элемент И 34, четвертый элемент И 35, хронизатор 36 приема и хронйзатор 37 передачи.

Устройство работает следующим образом.

По сигналам, поступающим с канального входа 2, хронизатор 36 приема определяет границы кодовых комбинаций на приеме и за каждую кодовую комбинацию выдает: по третьему вы5 ходу — последовательность импульсов тактовой частоты для продвижения проверочных символов во входном регистре 24 второго элемента задержки

5 и выходном регистре 27 первого элемента задержки 10, по первому и второму выходам — управляющие сигналы с цикловой частотой, которые сдвинуты по отношению друг к другу на время, не меньшее времени вывода проверочных символов из декодирующе15 го блока 9, и не совпадающие с моментом их вывода.

Хронизатор 37 передачи определяет границы кодовых комбинаций на rrepe"" дачи и за каждую кодовую комбинацию выдает: со второго выхода — последовательность тактовых импульсов для продвижения проверочных .символов во входном регистре 29 первого элемента задержки 10 и выходном регистре 26 второго элемента задержки 5, с первого выхода — управляющий сигнал, перекрывающий по длительности последовательность тактовых импульсов со второго выхода хронизатора передачи.

На выходах четвертого элемента

И 35 и второго элемента И 31 сигнал появляется в случае совпадения управляющего сигнала с хронизатора передачи, поступаюшего на их вторые входы, и соответствующих управляющих сигналов с хронизатора приема, поступающих на их первые входы.

Выходные сигналы элементов И 31 и 35 управляют триггером 33, выходы которого подключены к первому элементу И 30 и третьему элементу И 34 таким образом, что при наличии сигнала на выходе элемента И 35 разреша- . ющий сигнал с триггера поступает на вход 2 элемента И 30, а при наличии сигнала на выходе элемента И 31— разрешающий сигнал поступит на вход

2 третьего элемента И 34.

В результате этого на выходе одного из элементов И 34 или 30 будет присутствовать сигнал, совпадающий с тем из двух управляющих сигналов хронизатора приема, который в данный момент не совпадает с управляющим сигналом хронизатора передачи. Через элемент ИЛИ 32 этот сигнал поступает на вторые входы блоков элементов И первого и второго элементов задержки, т.е. на управляющие входы блоков элементов И будет поступать сигнал íа каждую кодовую комбинацию, не совпадающий с моментами поступления проверочных символов как с кодирующего, так и с декодирующего блоков.

На параллельные входы блоков И периодически поступают проверочные символы с входных регистров, соответI

746668 ственно первого и второго элементов задержки.

Смена проверочных символов во входных регистрах происходит, соответственно в первом элементе эацержки — в моменты поступления проверочных символов с кодирующего узла, во втором элементе задержки — в моменты вывода проверочных символов из декодирующего устройства.

Между моментами ввода и вывода проверочные символы хранятся во входных регистрах и происходит их перезапись в выходные регистры.

Вывод проверочных символов из выходного регистра 26 второго элемента задержки происходит в моменты вывода проверочных символов из кодирующего блока 3..

Вывод проверочных символов из выходного регистра 27 первого элемента задержки происходит в моменты 20 поступления проверочных символов из декодирующего блока 9.

При смещении выходных сигналов хронизаторов приема и передачи друг относительно друга сигнал хронизато- 25 ра приема, по которому осуществляется перезапись проверочных символов, входит в зону управляющего сигнала хронизатора передачи, при этом происходит срабатывание триггера и пере- З0 запись контрольных символов будет осуществляться другим сигналом хронизатора приема., В этом случае возможно изменение временных отношений в пределах после- З довательности кодовых комбинаций и будет подключен другой отвод первого элемента задержки.

Пусть, например, в устройстве исользуется код (n,ê) с длиной кодоой комбинации п двоичных символов при п-к проверочных символах. При таком коде основное устройство будет иметь большую нерабочую зону, которая составляет +"- от длительности цикла.

В предлагаемом устройстве нерабочая. зона s фазовом состоянии между циклами передачи исключена, а переключение емкости элементов задержки из-за изменения фазового .состояния 50 между циклами передачи и приема, приводящее к переводу устройства в режим запроса, определяемое относительной величиной стабильности задающих генераторов и запаздывания сиг- Я налов связи, будет происходить достаточно редко.

Таким образом, в предлагаемом устройстве значительно реже появляется необходимость перевода устройства в режим запроса при определенных фазовых соотношениях между циклами передачи и приема и тем самым повышена надежность связи.

Формула изобретения

Устройство для передачи и приема дискретных сигналов по авт. свид.

9557403, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены элемент ИЛИ, элементы И, триггер, хронизатор передачи .и хронизатор лриема, вход которого соединен с канальным входом устройства, первый и второй выходы хронизатора приема соединены соответственно с первыми входами первого-второго элементов И и третьего-четвертого элементов И, первый выход хронизатора передачи соединен с вторыми входами второго и четвертого элементов И, выходы которых соединены с входами триггера, выходы триггера подключены к вторым входам первого и третьего элементов

И, выходы которых соединены с входами элемента ИЛИ, первый и второй элементы задержки выполнены в виде последовательно соединенных входного регистра, блока элементов И и выходного регистра, входы входных регистров соединенй с входами элементов задержки, выходы выходных регистров . подключены к выходам элементов задержки, управляющие входы блока элементов И подключены к выходу элемента ИЛИ, тактовые входы входного регистра первого элемента задержки и выходного регистра второго элемента задержки соединены с вторым выходом хронизатора передачи, тактовые входы выходного регистра первого элемента задержки и входного регистра второго элемента задержки соединены с третьим выходом хронизатора приема.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9557403, кл. G 08 С 19/28, 13.10.75 (прототип).

74бб68,.

4".

Ф

°;1 !;, /с, ., 4 Р4

Составитель В.Кузнецов

Редактор П.Петрова Техред M Куэьма Корректор М.Вигула

Эакаэ 3956/43 Тираж 682 Подписное

ЦНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4