Устройство для считывания информации из блоков памяти

Иллюстрации

Показать всеРеферат

,М <. 46719

Союз Советскнк

Соцнапистнческнк

Ресттублмм

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (51) Дополнительное к авт. свид-ву— (22) Заявлено 03.01.78 (21) 2566756/18-24 (5i) М. Кл.2 б 1! С 7/00 с присоединением заявки №вЂ” еееудерстееклый комитет

СССР (23) Приоритет .—

Опубликовано 07.07.80. Бюллетень № 25 (53) УДК 628.327..6 (088.8) ао делам изобретений и открытий

Дата опубликования описания 17.07.80

Н, Н. Журавский, К. Г. Самофалов, А. М. Селигей и Д. С. Тростянецкий (22) Авторы изобретения

Киевский ордена Трудового Красного Знамени завод вычислительных машин и управляющих машин (7!) Заявитель (54) УСТРОЛСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ

ИЗ БЛОКА ПАМЯТИ

Изобретение относится к запоминающим устройствам, в частности к постоянным запоминающим устройствам, н может быть использовано в вычислительной технике и автоматике.

Известно долговременное запоминающее 5 устройство, содержащее запоминающие трансформаторы, выходные обмотки которых подключены ко входам усилителей считывания; выходы усилителей соединены с регистром числа. Устройство содержит элементы совпадения и токозадающие элементы по числу разрядов, токозадающие элементы соединены со входами усилителей считывания. Устройство содержит также формирователь синхроимпульсов. Описанное включение токозадающих элементов повышает быстродействие устройства, однако это сопровождается увеличением оборудования 11).

Наиболее близким по технической сущности к изобретению является устройство для считывания информации из блоков па-: мяти, содержащее прошитые числовыми проводами запоминающие трансформаторы, одни концы обмоток считывания которых подключены к коллекторам первых, базам вторых транзисторов, другие — к эмиттерам транзисторов и шине нулевого потенциала.

Коллекторы транзисторов усилителей считывания соединены со входами триггеров регистра числа, выходы которых соединены с базами соответствующих транзисторов усилителей считывания.

К недостаткам устройства следует отнести наличие дополнительного оборудования — управляющих транзисторов (21.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что в устройстве для считывания информации из блока памяти, содержащем усилители считывания, каждый из которых выполнен на транзисторе, база которого подключена к соответствующему выходу блока памяти, а коллектор — ко входу соответствующего триггера регистра числа и через резистор— к источнику напряжения, установочные входы триггеров регистра числа соединены с шиной сброса, единичные выходы триггеров регистра числа подключены к эмиттерам транзисторов.

746719

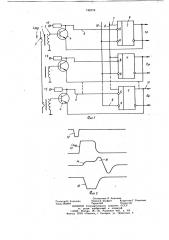

На фиг. 1 приведена схема запоминающего устройства; на фиг. 2 — временная диаграмма основных сигналов.

Устройство содержит в блоке памяти и индуктивных запоминающих элементов 1, прошитых кодовыми проводами 2 по принципу «прошито — не прошито». В качестве примера показана прошивка кодовым проводом 2 кода !О...l. Обмотки 3 считывания запоминающих элементов I подключены к базам. транзисторов 4 усилителей считывания. Коллекторы транзисторов 4 соединены со входами 5 триггеров 6, стробируемые входы 7 которых подключены к шине 8, а установочные входы 9 подключены к шине 10, Единичные выходы 11 с триггеров 6 в каждом разряде соединены с эмиттерами транзисторов 4.

Устройство работает следующим образом.

По шине 10 на установочные входы 9 поступает сигнал 12, устанавливающий во всех п разрядах триггеры 6 в нулевое состояние. При этом на единичных выходах 11 триггеров 6 устанавливаются низкие (нулевые) уровни напряжения, этим эмиттеры транзисторов 4 подключаются практически к нулевому потенциалу и разрешено последующее срабатывание транзисторов 4. При подаче импульса 13 тока опроса i,„ð по кодовому проводу 2 в обмотках 3 считывания тех разрядов, в которых прошиты единицы, индуктируются сигналы 14, открывающими транзисторы 4, при этом на их коллекторах, устанавливаются сигналы 15, переводящие совместно со стробирующим сигналом, действующим на шине 8, триггеры 6 в единичное состояние. В тех разрядах, в которых сигнал 14 отсутствует, триггеры 6 остаются в нулевом состоянии. После перехода триггера 6 в единичное состояние на его еди ничном выходе 11 устанавливается высоки уровень напряжения. При этом высоким уровнем на выходе 1! транзистор 4 смещен в обратном направлении, и сигнал 5 на коллекторе транзистора 4 прекращается. В каждом разряде триггер 6 срабатывает в течение различных промежутков времени, определяемых разбросом параметров конкретных элементов, поэтому, если закрывание транзистора 4 произошло раньше, чем окончился импульс 13 тока опроса, на базе транзистора 4 наблюдается выброс 16. Однако этот выброс не вызывает срабатывание транзистора 4, поскольку он заперт смещением в эмиттер.

По сравнению с устройством-прототипом в данном устройстве достигнуто уменьшение аппаратурных затрат, благодаря исключению управляющих транзисторов в каждом разряде.

Формула изобретения

Устройство для считывания информации из блока памяти, содержащее усилители считывания, каждый из которых выполнен на транзисторе, база которого подключена к соответствующему выходу блока па мяти, а коллектор — ко входу соответствующего триггера регистра числа и через резистор— к источнику напряжения, установочные входы триггеров регистра числа соединены с шиной сброса, отличающееся тем, что, с целью упрощения устройства, в нем единичные

36 выходы триггеров регистра .числа подключены к эмиттерам транзисторов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 466553, кл. G 11 С 17/00, 04.01.74.

2. Авторское свидетельство СССР по заявке № 2545393/24, кл. G 11 С 7/00, 2! .11.77 (прототип).

74б719

Составитель Л. Амусьева

Редактор Н. Ахмедова Техред К. Шуфрич Корректор Г. Решетиик

Заказ 3959 44 Тираж 662 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

I l3035, Москва, Ж вЂ” 35, Раушская наб., n. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4