Запоминающий модуль для матричных блоков памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

»»746728

1 1 (61) Дополнительное к авт. свид-ву— (22) Заявлено 16.02.78 (21) 2579949/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) M К

6 11 С 15/00

Гоеударствеииый комитет

СССР ио делам изооретеиий и открытий

Опубликовано 07.07.80. Бюллетень № 25

Дата опубликования описания 17.07.80 (53) УДК 681.327. .6 (088,8) (72) Автор изобретения

Я. И. Фет

Институт математики Сибирского отделения АН СССР (71) Заявитель (54) ЗАПОМИНАЮЩИИ МОДУЛЬ ДЛЯ МАТРИЧНЫХ

1 БЛОКОВ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известен запоминающий модуль для матричных блоков памяти, содержащий двоичный запоминающий элемент с вентилями записи единицы и нуля, схему сравнения и шину опроса, причем входы схемы сравнения соединены с выходами запоминающего элемента и с шиной опроса.

В ассоциативных матрицах, построенных их таких модулей, основной операцией является поиск числа, равного заданному.

Все другие вычислительные и информационно-логические операции осуществляются по микропрограммам, состоящим из последовательностей операций поиска и записи.

В соответствии с этими микропрограммами обработка ведется последовательно по разрядам и требует значительного времени.

Наиболее близок к предлагаемому запоминающий модуль для матричных блоков памяти, содержащий элемент памяти, элементы И, ИЛИ и НЕ; схему сравнения, шины опроса, записи и запрета, причем первый и второй входы схемы сравнения соединены соответственно с единичным и нулевым выходами элемента памяти, а третий

2 и четвертый — с шиной опроса и выходом первого элемента НЕ, вход которого соединен с шиной опроса, первые входы элемента памяти подключены к шине записи, шина запрета соединена с первым входом первого элемента И, второй вход которого подключен к первому входу запоминающего модуля, а выход — к первому входу первого элемента ИЛИ, выход которого соединен с первым выходом запоминающего модуля, первый вход второго элемента ИЛИ соединен со вторым входом запоминающего модуля, а выход — со вторым выходом запоминающего модуля, первые входы второго и третьего элементов И соединены с третьим входом запоминающего модуля, второй и третий входы третьего элемента И соединены соответственно с шиной опроса и нулевым выходом элемента памяти, а выход третьего элемента И вЂ” со вторыми входами первого и второго элементов ИЛИ.

В ассоциативных матрицах, построенных из таких модулей, не только операция поиска по совпадению, но и ряд операций сложного поиска (поиск всех чисел, больших заданного или меньших заданного; поиск числа, ближайшего меньшего к заданному

746728 третий 19, четвертый 20 и пятый 21 элементы ИЛИ.

Кроме того, описываемый модуль имеет входы 22 — 25 логических переменных v, у

z, е соответственно и выходы 26 — 29 логических переменных ч, у, z, е соответственно. При соединении модулей в матрицу выходы 26 и 28 каждого модуля соеди няются соответственно со входами 22 и 24 соседнего справа модуля, выход 29 — со входом 25 соседнего слева модуля, а выход 27 — со входом 23 соседнего снизу модуля.

Первый и второй входы схемы сравнения 4 соединены с соответствующими выходами элемента памяти 1, а третий и чет45

$O поиск максимального числа) выполняются аппаратно, за одну микрокоманду. Однако и в этих ассоциативных матрицах более сложные операции (например, массовые арифметические вычисления) осуществляются с помощью микропрограмм, требующих для своего выполнения значительного времени.

Целью настоящего изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что запоминающий модуль содержит четвертый и пятый элементы И, третий, четвертый и пятый элементы ИЛИ, второй элемент HE и шины маскирования и настройки, причем шина маскирования соединена с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу схемы сравнения, а выход — ко второму входу второго элемента И, выход которого соединен с первыми входами четвертого элемента И и четвертого элемента ИЛИ, вторые входы которых подключены к шине настройки, соединенной также через второй элемент НЕ с первым входом пятого элемента И; выход четвертого элемента ИЛИ соединен с третьим выходом запоминающего модуля, второй вход пятого элемента И подключен к четвертому входу запоминающего модуля, а выход — к первому входу пятого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, а выход — с четвертым выходом запоминающего модуля и со вторыми входами элемента памяти, третьи входы которого .соединены с ЗО шиной запрета, а четвертые соответственно с шиной опроса и с выходом первого элемента НЕ.

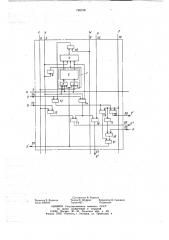

На чертеже приведена функциональнологическая схема предложенного запоминающего модуля для матричных блоков памяти.

Модуль содержит элемент памяти 1, состоящий из собственно запоминающего элемента 2 и вентилей записи единицы и нуля 3, схему сравнения 4, шину опроса 5, первый элемент НЕ 6, шину записи 7, ши- о ну запрета 8, шину маскирования 9, шину настройки 10, второй элемент HE 11, первый 12, второй 13, третий 14, четвертый 15 и пятый 16 элементы И, первый 17, второй 18, вертый входы — с шиной опроса 5 и с выходом элемента НЕ 6, вход которого соединен с шиной опроса 5. Шина маскирования 9 и выход схемы сравнения 4 соединены со входами элемента ИЛИ 19. Первые входы элементов И 13 и 14 соединены со входом 24. Второй вход элемента И 13 подключен к выходу элемента ИЛИ 19, а второй вход элемента И 14 — к шине опроса 5.

Третий вход элемента И 14 соединен с нулевым выходом элемента памяти 1. Выход элемента И 13 соединен с первыми входами элемента И 15 и элемента ИЛИ 20, вторые,входы которых подключены к шине настройки 10. Выход элемента ИЛИ 20 сое- динен с выходом 28, а выход элемента И 15 — со вторым входом элемента

ЙЛИ 21, выход которого подключен к выходу 29. Первый вход элемента ИЛИ 21 соединен с выходом элемента И 16, входы которого соединены соответственно со входом 25 и через элемент НЕ 11 — с шиной настройки 10. Выход элемента И 14 соединен со вторыми входами элементов

ИЛИ 17 и 18. Первый вход элемента ИЛИ 17 соединен с выходом элемента И 12, входы которого подключены соответственно ко входу 22 и к шине запрета 8. Первый вход элемента ИЛИ 18 соединен с входом 23, а выход — с выходом 27. Выход элемента ИЛИ 17 подключен к выходу 26. Первые входы элемента памяти 1 подключены к шине записи 7, вторые — к выходу элемента ИЛИ 21, третьи — к шине запрета 8, а четвертые — соответственно к шине опроса 5 и выходу элемента НЕ 6.

Как видно из чертежа, описанный модуль реализует следующие логические функции:

Ь = ахчах (1)

z = z(hvar)vf (2) ч = vtvzax (3) у = przax (4) е = zf(4vw) vef (5)

g = xeUt (6)

g = хе и1 (7) где х,f, t, а, U соответственно — логические переменные на шинах опроса

5; настройки 10, запрета 8, маскирования 9 и записи 7, а — состояние элемента памяти 1, Ъ вЂ” значение двоичной переменной на выходе схемы сравнения (предполагается, что в= 1 при х=а).

В ассоциативной матрице, состоящей из модулей предлагаемой конструкции, могут выполняться следующие микрокоманды: — запись «горизонтальная», — запись «вертикальная», — чтение <горизонтальное», — чтение дизъюнкти вное, — поиск по совпадению, — поиск всех чисел, больших заданного, — поиск всех чисел, меньших заданного, 746728

5 — чтение «вертикальное», — поиск ближайшего меньшего, — поиск максимального числа, — совмещенные поиск-запись.

Рассмотрим в качестве примера. выполнение поиска по совпадению и поиска чисел, больших (меньших) заданного.

Для выполнения этих поисков на все входы 24 левой границы матрицы подаются константы «1», на все входы 22 левой границы — константы <О». На все шины 8 подаются константы «1». Состояния входов

23 и шин 10 несущественны.

По шинам опроса 5 поступает поразрядно (старшими разрядами слева) код признака опроса, по шинам 9 — код маски (в маскируемых разрядах а = 1) .

Так как, согласно (2), в каждом модуie

1s ле z = к(Ы®)vf, сигнал z = 1 проходит в каждой строке матрицы до тех пор, пока незамаскированные разряды соответствующих чисел эквивалентны разрядам признака . опроса. В частном случае, в той строке, где содержится число, равное признаку (или нескольких таких строках), на выходе 28 правой границы матрицы появится сигнал «1».

Предположим, что какое-либо число совпадает с признаком опроса не по всем незамаскированным разрядам, а лишь по нескольким старшим, после чего имеется разряд, в котором а = О, x = 1. Ясно, что

Ассоциативная матрица, построенная из описанных модулей, приобретает новые положительные свойства: в ней может выполняться аппаратно, с большой эффективностью, ряд информационно-логических операций и, кроме того, возможна независимая обработка в различных полях матрицы. Этй

so такое число меньше признака опроса, независимо от соотношения дальнейших (млад/ ших) разрядов. В том модуле, где впервые а = О и х = 1, схема сравнения вырабатывает Ь = О, что приводит к z = О. Однако согласно (3) в этом модуле появляется сигнал v = 1, который проходит до правой границы матрицы и выдает там ч = 1. ss

Итак, в любой строке матрицы, содержащей число, меньшее заданного признака, на правой границе будет z = О, v = 1.

Третий случай — число больше заданного признака. При этом нарушение эквивалентности при просмотре слева направо происходит впервые за счет разряда, в котором а = 1, х = О. В таком модуле также

Ь = О, z О, но V = 1 не появляется.

Следовательно, в любой строке, содержащей число, большее заданного признака, 4 на правой границе z = О, ч = О.

6 свойства обеспечивают повышения быстродействия при решении многих задач.

Формула изобретения

Запоминающий модуль для матричных блоков памяти, содержащий элемент памяти, элементы И, ИЛИ и НЕ, схему сравнения, шины опроса, записи и запрета, причем первый и второй выходы схемы сравнения соединены соответственно с единичным и нулевым выходами элемента памяти, а третий и четвертый — с шиной опроса и выходом первого элемента НЕ, вход которого соединен с шиной опроса, первые входы элемента памяти подключены к шине записи, шина запрета соединена с первым входом первого элемента И, второй вход которого подключен к первому входу запоминающего модуля, а выход — к первому входу первого элемента ИЛИ, выход которого соединен с первым выходом запоминающего модуля, первый вход второго элемента ИЛИ соединен со вторым входом запоминающего модуля, а выход — со вторым выходом запоминающего модуля, первые входы второго и третьего элементов И соединены с третьим входом запоминающего модуля, второй и третий входы третьего элемента И соединены соответственно с шиной опроса и нулевым выходом элемента памяти, а выход третьего элемента И вЂ” со вторыми входами первого и второго элементов ИЛИ, отличающийся тем, что, с целью повышения быстродействия запоминающего модуля, он содержит четвертый и пятый элементы И, третий, четвертый и пятый элементы ИЛИ, второй элемент НЕ и шины маскирования и настройки, причем шина маскирования соединена с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу схемы сравнения, а выход — ко второму входу второго элемента И, выход которого соединен с первыми входами четвертого элемента И и четвертого элемента ИЛИ, вторые входы которых подключены к шине настройки, соединенной также через второй элемент НЕ с первым входом пятого элемента И, выход четвертого элемента ИЛИ соединен с третьим выходом запоминающего модуля, второй вход пятого элемента И подключен к четвертому входу запоминающего модуля, а выход — к первому входу пятого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, а выход — с четвертым выходом запоминающего модуля и со вторыми входами элемента памяти, третьи входы которого соединены с шиной запрета, а четвертые — соответственно с шиной опроса и с выходом первого элемента НЕ.

746728

Составитель В. Рудаков

Редактор Б. Федотов Техред К. Шуфрич Корректор В. Синицкая

Заказ 3960/45 Тираж 662 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент» r. Ужгород, ул. Проектная, 4