Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

чАлфкн в В прад ву„ие. ь.

:.бл

О Л С г Е

Союз Советских

Социалистических

Республик 1 1 746735

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 26.12.77 (21) 2560411/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) M. Кл.2

Q 11 С 19/00

Государственный камнтет

СССР пе делам нзебретеннй и еткрытнй (53) УДК 628.327..6 (088.8) Опубликовано 07.07.80. Бюллетень №25

Дата опубликования описания 1?.07.80

Г. А. Бривин и М. А. Овчинников (72) Авторы изобретения (71) Заявитель (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике, в частности, к буферным устройствам в аппаратуре обмена дискретной информацией, может быть использовано при разработке высокоскоростных буферов в цифровых устройствах.

Известно регистровое запоминающее устройство, содержащее последовательное за- поминающее устройство на сдвиговых регистрах, состоявших из ряда ячеек, каждая из которых служит для хранения одного бита и маркерной метки (1).

Недостатком устройства являются большие затраты оборудования.

Наиболее близким к предложенному является запоминающее устройство, содержащее входной регистр, группы основных регистров и, выходной регистр и ячейки управления записью, группы элементов И, схему управления, формирователь готовности (2).

Недостатками устройства являются большие затраты оборудования и наличие паузы между запросом на выдачу информации и началом этой выдачи, снижающее быстродействиее.

Цель изобретения — повышение нрдежности и быстродействия устройства.

Это достигается тем, что в устройство введены формирователь синхронизации, регистр адреса, блок опроса регистра адреса

5 и коммутатор, каждый из выходов которого соединен с соответствующими выходными шинами устройства, каждый из входов соответствующего числа соединен с выходом соответствующего разряда соответствующего регистра сдвига. Каждый из входов уп1О равления коммутатора соединен с соответ ствующим выходом блока опроса регистра адреса, каждый из входов которого соединен с первым входом формирователя импульсов готовности и выходом соответствующего раз1 ряда регистра адреса, вход записи которого ,соединен с каждым из входов записи устройства и первым входом формирователя импульсов синхронизации, второй и третий входы которого соединены соответственно со входом синхронизации и входом опроса

2О устройства.

Первый выход формирователя синхронизации соединен со входом сдвига каждого регистра сдвига и входом сдвига регистра

746735

fO

20 и зе

Формула изобретения ло

4$

И адреса, вход реверса которого соединен со вторым выходом формирователя импульсов синхронизации. Вход опроса схемы опроса регистра адреса соединен с выходом готовности устройства.

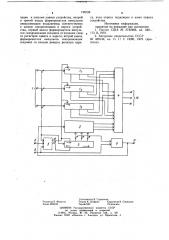

Структурная электрическая схема устройства приведена на чертеже.

Устройство содержит группу регистров

11 — 1, сдвига, регистр 2 адреса, блок 3 опроса регистра адреса, коммутатор 4, формирователь 5 импульсов синхронизации и формирователь 6 импульсов готовности.

На чертеже обозначены шины 7 записи, шина 8 синхронизации, шина 9 опроса, выходные шины 10 и шина 11 готовности устройства; выходы 12, 13 формирователя импульсов синхронизации.

Устройство работает следующим образом.

На вход 8 поступает периодическая по следовательность синхроимпульсов от внешнего генератора, формирователь 5 распределяет эту последовательность на две, каждая из которых разрешает прохождение импульсов со входов 7 на выход 12 и со входа 9 на выход 13 соответственно, обеспечивая тем самым разнесение во времени моментов сдвигов вправо и влево в регистре 2 адреса. Хранящиеся в буфере кодограммы записываются параллельным кодом по входам 7 устройства в регистры 1,— 1 сдвига, число которых равно разрядности хранимого кода (на чертеже для простоты показан случай записи трехразрядного кода — 1,, 1, 1 ), а количество разрядов в каждом регистре (в том числе и регистре 2 адреса) равно количеству кодограмм, которое буфер хранит в данном конкретном случае. При поступлении кодограммы формирователь 5 синхронизирует момент записи и сдвига в регистрах 1, — 1> по своему выходу 12; при этом «единнца», свидетельствующая о поступлении кодограммы, поступает в регистр 2 адреса (по входу записи), и содержимое регистра 2, так и содержимое регистров

1,— 1>, сдвигается на один разряд вправо.

При поступлении на вход 9 устройства запроса на выдачу очередной кодограммы из буфера формирователь 5 синхронизирует этот сигнал и сигналом с выхода 13 сдвигает содержимое («единицы» поступивших кодограмм) регистра 2 назад, влево (по входу реверса), одновременно опрашивая формирователь 6, на соответствующий вход которого поступают сигналы с выходов разрядов регистра 2, свидетельствующие о наличии «единиц» в регистре 3, а следовательно, кодограмм в регистрах 1> — 1,, при наличии которых на выход 11 поступают сигнал «Готов к выдаче очередной кодограммы» и сигнал на вход опроса блока 3. Блок 3 представляет собой схему «пирамиду» опроса, например, ключей, на которые выводится информация (поразрядно) о наличии «единиц» в регистре 2, и опрос осуществляется до «первой найденной единицы> справа налево, после чего при нахождении этой единицы сигнал об этом поступает на соответствующий вход управления коммутатора 4, переключающегося на вывод числа с соответствующих входов числа коммутатора 4 на выходы 10 устройства. Например, если единица найдена в последнем разряде регистра 2, коммутатор подключает выходы последнего разряда каждого из регистров

1i — 1, на выходы 10 устройства.

Таким образом, время поиска выдаваемой кодограммы сокращается до времени задержки переключения элементов.

Кроме того, применение коммутатора и связанного с ним оборудования позволило отказаться от широко применяемого способа «быстрого продвижения» выдаваемой кодограммы при получении запроса — к выходу регистров 1i — 1 сдвига и изъять занятое на это оборудование, что позволило значительно сократить затраты оборудования и повысить быстродействие устройства.

Предлагаемое устройство позволяет накапливать и выдавать кодограммы в режиме асинхронной работы обменивающихся устройств в вычислительной аппаратуре различного назначения.

При использовании для построения устройства интегральных модулей 134 серии экономический эффект по сравнению с прототипом (при одинаковой элементной базе) составляет 50 руб, на одно устройство и возрастает с увеличением степени интеграции логических элементов.

Буферное запоминающее устройство, содержащее регистры сдвига, входы записи которых соединены с соответствующими шинами записи устройства, формирователь импульсов готовности, выход которого подключен к шине готовности устройства, а один из входов соединен с шиной опроса устройства, н выходные шины, отличающееся тем, что, с целью повышения надежности и быстродействия устройства, оно содержит формирователь импульсов синхронизации, регистр адреса, блок опроса регистра адреса и коммутатор, числовые входы которого соединены с соответствующими выходами соответствующих регистров сдвига, управляющие входы коммутатора соединены с соответствующими выходами блока опроса регистра адреса, а выходы коммутатора подключены к соответствующим выходным шинам устройства, адресные входы блока опроса регистра адреса соединены с другим входом формирователя импульсов готовности и соответствующими выходами регистра адреса, вход записи которого соединен с первым входом формирователя импульсов синхрониса, вход опроса подключен к шине опроса устройства.

Источники информации, принятые во внимание при экспертизе !. Патент США № 3742466, кл. 340—

173 R 1972.

2. Авторское свидетельство СССР № 469142, кл. G 11 С 19/00, 1975 (прототип) .

746735 зации и шинами записи устройства, второй и третий входы формирователя импульсов синхронизации подключены соответственно к шинам синхронизации и опроса устройства, первый выход формирователя импульсов синхронизации соединен co входами сдвига регистров сдвига и адреса, второй выход формирователя импульсов синхронизации соединен со входом реверса регистра адреСоставитель В. Гордонова

Редактор Б. Федотов Техред К.Шуфрнч Корректор В. Синицкая

Заказ 3960/45 Тираа 662 Подписное

UHHHHH Государственного комитета СССР по делам изобретений и открытий

1 l 3035, Москва, )K — 35, Раушская наб., д. 4/5

Филиал ППП <Патент>, г. Ужгород. ул. Проектная, 4