Запоминающее устройство

Иллюстрации

Показать всеРеферат

I (>i) 746745

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ . (6l ) Дополнительное к авт. свид-ву— (22)Заявлено 17.04.78 (2! ) 2606194/18-24 (51) M. Кл.

Ci 11 С 29/00 с присоединением заявки %в

Гооударстееииый комитет (23) Приоритет -. по делам изобретений и открытий (53) УДК 681.327.,66{ 088. 8) Опубликовано 07,07.80. Бюллетень Ле 25

Дата опубликования описания 10,07,80

В. И. Корнейчук, А. В. Городний Е. Н, Сосновчик, В. А. Журба и В. Я. Юрчишин (72) Авторы изобретения

Киевский ордена Ленина политехнический институт им. 50 летия Великой Октябрьской социалистической революции (73) Заявитель (54) ЗА ПОИ ИНАЮШЕЕ УСТРОЙСТВО

Изобретение относится к вычислитель-ной технике и может быть использовано при разработке устройств памяти на сдвиговых регистрах с большой степенью интеграции.

Известно запоминающее устройство (ЗУ} на сдвиговых регистрах, в которых реализуется динамическое хранение информации. Каждый сдвиговый регистр хранит одноименные разряды всех слов, информационное слово записывается со вхоца ЗУ параллельно на входы всех сдвиговых регистров, затем происходит сдвиг информации и в освободившиеся первые разряды записывается последующее слово, выходы сдвиговых регистров подключаются к их входам и при последующих сдвигах информация вновь пе редвигается в пределах сдвигового регистра от входа к выходу jl) .

Нецостатком укаэанного устройства является искажение информации в случае наличия отказавших элементов, причем, ввиду сдвигового характера накопителя, каждый отказавший элемент влияет на все информационные разряды, которые сдвигаются через него.

Наиболее близким к предлагаемому является ЗУ на сдвиговых регистрах, содержащее накопитель, генератор фаз, блок адрееных цепей, входной и выходной регистры )2).

Недостатком этого устройства является отказ накопителя при выходе иэ строя. запоминающих элементов.

Hem, изобретения - повышение надеж» ности ЗУ за счет устранения отказов основного блока памяти.

Поставленная цель достигается тем, что в ЗУ содержащее основной блок памяти, первый вход которого соединен с выходом адресного блока, управляющий генератор, выход которого соединен со вторым входом основного блока памяти,,входной и выходной регистры, введены последовательно соединенные блок тестового контроля, первый блок кодирования и первый дополнительный блок памяти, 5 ф исправностей сдвиговых регистров зависит от способа кодирования ситуаций.

Например, коЮнрованне может производиться следующим образом,: 00 - нет нскажений; 01 искажается 0; 10 -искажается 1

Искажаться одновременно 1 н 0 не могут при предположенин, что имеются отказы (генераторы 1 н О), так как характер нскаженая всей информации, про двнгающейсй через сдвнговый регистр, определяется видом отказа ближайшего к выходу запомннаюшего элемента. Таким образом, режим тестового контроля заканчивается эапопненнем первого дополнительного блока 10. При записи информационного слова с шины 13 через входной регистр 1, адрес которого подается с шины 15 на адресный блок 12, в блоке 8 кодирования происходит кодирова ние на основанйи данных о значении разрядов ннформаиибййого слова -и состояния сдвиговых регистров, которые считываются из блока 10 памяти при каждом обращении к нему при записи.

Принцип кодирования распределения инверсий может быть показан на следующем примере.

Пусть на.второй дополнительный блок

1 1 памяти постуйает о -разрядное информационное слово, представляющее конкретную комбинацию 0 и 1. С блока 10 поступают коды состояния сдвиговых регистров.

Norye" йоявнться следующие ситуации.

Если искажается 0 (эалипание в 4, . то разряды, содержащие О, нужно инверти ровать. И наоборот, если искажается 1, то необходимо инвертнровать разряды, содержащие 1. Если направление искажения (О или 1) совпадает с цифровым значением раэрада то в"этом случае нельзя инвертировать, н данный разряд записывается только в прямом коде, Распределение инверсий можно, например, кодиро- . вать по аналогии с кодом Хэмминга (при инвертировании каждой группы Хамминга" в.соответствующий разряд записывается

1). В блок 11 записывается полученный код инвертирования по соответствующим адресам, которые задаются с адресного блока 1 2. В блоке 7 кодирования информация, поступившая с входного регистра

1, кодируется и соответствии с кодами инвеотирования, поступающими с блока

11, и зййисыиается в соответствующие разряды блока 4. При считывании информации по адресу, который задается с шиФ

3., 7467 дешифратор, второй блок кодирования, второй дополнительный блок памяти и третий блок кодирования, один нэ входов которого саедынен с выходом входного регнстра и одним HG входов второго блока коднрования, другой вход второго блока кодирования подключен к первому выходу второго дополнительного блока памяти, первый вход которого соединен с вЬкодом третьего блока кодирования, 0 другой вход третьего блока кодирования сЗВЙй:йей-с вйхбдом первого дополнительного блока памятн, выход-адресного бло Ка подключен ко второму входу второго дополнительного блока памяти, второй 15 вь1ход которого соедннен с одним иэ входов дешифратора, другой вход дешнфратора соединен с первым выходом основного блока памяти, второй выход которого сЫдКнен с другим входом блока тестово- 20 го контроля, выход дешнфратора соединен со входом виходногЬ ре3 истра, выход второго блока кодирования соединен с третьим входом основного блока памяти, чет25 вертый.вход к<йорого соединен с другим

Выходом блока тестового контроляв

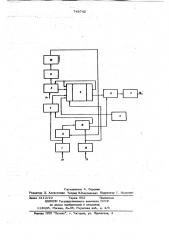

На чертеже представлена функциональная схема устройств.

Устройство содержит входной регистр

1, выходной регистр 2, управляющий гезо .нератор 3, основной блок 4 памяти, блок

5 тестового контроля, блоки 6, 7 н 8 кодирования, дешифратор 9, дополнйтельные блоки 10 и 11 памяти, адресный блок 12, информационную шину 13, уп35 равляющне шины 14, 15, выход 16 устройства.

Накопитель основного блока 4 памяти выполнен на сдвиговых регистрах. .!

Устройство работает следующим образом.

Перед началом работы ЗУ с управляю щего входа 14 пульта "уцравлейия вй ючается режйм тестового контроля, при котором s блоке 5 тестового контроля генерйруются тестовые после!цовательности, "icîòîðìå эапнсываются в основном блоке 4 йамятн, Через время, равное циклу . полного заполнения ЗУ информацией, она

50 считывается с блока 4 памяти и анализируется в блоке 5 тестового койтроля.

Результаты анализа кодируются в блоке

6 йМирования н с его выходов записы- ваются в первый дополнительный блок 10 памяти. Чисао слов, хранящихся в блоке

10, соответствует разрядности слов, за :писанных параллельно в основной блок 4 памяти, а раэрядйость кодов состояния

5 74 ны 15, адресный блок 12 организует выборку нужного слова из блока 4 и кода инвертирования, соответствующего данно» му слову, из блока 1 1. Информация деко» дируется в блоке 8 и через выкодной регистр 2 слово считывается на выходе 16.

Таким образом, предложенное устройство ,позволяет существенно повысить надежность ЭЦВМ и компоновать накопитель не только из годных, но и частично бракованных матриц, что резко снижает себестоимость памяти. формула изобретения

Запоминающее устройство, содержащее основной блок памяти, первый axon которого соединен с выходом адресного блока, управляющий генератор, выход которого соединен со вторым входом основного блока памяти, входной и выходной регистры, о т л и ч а ю щ е е с я. тем, что, с целью повышения надежности устройства за счет устранения отказов основного блока памяти, в него введены последовательно соединенные блок тестового контроля, первый блок кодирования и первый дополнительный блок памяти, дешифратор, второй блок кодирования, второй дополнительный блок памяти и

6 третий блок кодирования, один из входов которого соединен с выходом входного регистра и одним из входов второго блока кодирования, другой вход второго бло ка кодирования подключен к первому выходу второго дополнительного блока памяти, первый вход которого соединен с выходом третьего блока кодирования, другой вход третьего блока кодирования

10 соединен с выходом первого дополнитель,ного блока памяти, выход адресного блока

1подкдючен ко второму входу второго дополнительного блока памяти, второй выход которого соединен с одним из входов де

И шифратора, другой вход дешифратора соединен с. первым выходом основного блока памяти, второй выход которого соединен с другим входом блока тестового контроля, выход дешифратора соединен со вхо20 дом выходного регистра, выход второго блока кодирования соединен с третьим входом основного блока памяти, четвертый вход которого соединен с другим выходом блока тестового контроля.

25 Источники информации, принятые во внимание, при экспертизе

1. Патент США М 3889243s кл. 5 11 С 29/00, опублик. 1976.

2. Авторское свидетельство СССР

З0 М 410465, кл. G 11 С 19/00, опублик.

l0,04.72 (прототип).

746745

Составитель А. Воронин

Редактор Л. Алексеенко Техред Ж,Кастелевнч Корректор Г. Назарова

Заказ 4112/22 Тираж 602 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений, и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4