Счетчик джонсона

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

В. Э. Петров и Е. Ф. Тошева (71) Заявитель (54) СЧЕТЧИК ДЖОНСОНА

Изобретение относится к автоматике и вычислительной технике.

Известен счетчик Джонсона, построенный на основе замкнутого в кольцо. регистра сдвига Pg.

Однако он не обеспечивает коррекции запрещенных состояний.

Известен также счетчик Джонсона, со-. держащий тактовую шину, Я -разрядный регистр сдвига, в каждый разряд которо

?o го, кроме первого и последнего, включены два элемента И, выходы которых соединены соответственно с входами установки в единицу и ноль разрядов, во всех, за исключением второго, разрядах инверсный вь?ход последнего разряда ре гистра сдвига соединен с информационным входом первого разряда, тактовая шина соединена со счетными входами разря дов, выходы первого и второ-о элементов И второго разряда соединены со входами установки в единицу и ноль последнего разряда, первые входы первых и вторых элементов И соединены соответствен2 но с инверсным и прямым выходами первого разряда, в каждом разряде, кроме второго, вторые входы элементов И соединены с прямым и инверсным выходами предыдущего разряда, вторые входы элементов И второго разряда соединены с . прямым и инверсным выходами предпоследнего разряда.

В этом счетчике при появлении вследствие сбоя запрешенной комбинации происходит ее коррекция, и счетчик устанав- ливается в разрешенное состояние 21.

Недостатком,его является. большое время выхода из запрещенных состояний.

Целью изобретения является уменьшение времени выхода из запрещенных состояний.

Для достижения поставленной цели в счетчике Джонсона, содержащем тактовую шину, К - разрядный регистр сдвига, в каждый разряд которого, кроме первого и последнего, включены цва элемента И, Bb? Ro??M которых сскэдинены соответственно с входами установки в единицу и ноль т а".о ыаы . ее а

746783

I ециницу и в ноль разрядов 1 - 2 — 1 - 7 соединены соответственно с выхоцами элементов И 2-1, 3-1,..., 7-1 и с выходами элементов И 2 - 2,3 - 2, 7-2; прямой и инверсный выходы разряда 1 — 1 соединены соответственно

1 с первыми входамй элементов И 2 - 1

4-1 иэлементовИ2-2и 4-2; прямой и инверсный выходы разряда

10 1 - 2 соединены соответственно с первыми входами элементов И 3 - 1 и

3 - 2; прямой и инверсный выходы разряда 1 - 4 соединены соответственно со вторыми входами элементов И 2 - 10

15 3 - 1, с первыми вхоцами элементов

И 5 - 1 и 6 - 1 и со вторыми вхоцами элементов И 2 - 2 q 3 - 2, первыми входами элементов И 5 - 2 д 6 - 2; прямой выход разряда 1 - 8 соецинен . со вторыми входами элементов И 4 - 10

6 - 1 и с первым входом элемента И

7 — 1р инверсный выхоц разряда 1 - 8 соединен со вторыми вхоцами элементов

И 4 — 2 И 6 - 2 и с первым входом элемента И 7 - 2; прямой и инверсный выходы разряда 1 - 6 соединены соответственно со вторыми входами элементов

И 5 - 1, 7 - 1 и 5 - 2, 7 - 2. разряцов, во всех, за исключением второго, разрядах инверсный выход послед1

1 него разряда регистра сдвига соединен с информационным входом первого разряда, тактовая шина соецинена со счетными входами разрядов, выходы первого и второго элементов И второго разряда соединены соответственно с входами установкй в ециницу и ноль второго разряда, прямые и инверсные выходы первой пары разрядов регистра сдвига с номерами 1, Й соединены соответственно с входами первого и второго элементов И первого среднего разряда с номером А, равным лелей части числа 1 н, прямые

2 выходы каждого из вторых пар разрядов с номерами 1, А и А, N соединены с вхо дами первых элементов И соответственно второго среднего разряда с номером В, 20 равным нелой части числа 1 + А я

2 третьего среднего разряда с номером С, равным нелОй частя числа A + N ннвер2 25 сные выходы каждого из.вторых пар разрядов с номерами 1, А и А, N соедине» ны с входами вторых элементов И соот» ветственно второго среднего разряда с номером В и третьего среднего разряда 30 с номером С, прямые выходы третьих пар разрядов с номерами 1, В; В, А;

А, С и С, hl соединени соответственно с входами первых элементов И четвертого, пятого, шестого и седьмого средних 35 разрядов с номерами, равными целым частям чисел 1+В, В+А, А+С и С+Й

2 - 2 2 2 входы вторых элементов И которых соединены соответственно с инверсными вы- 40 ходами третьих пар разрядов с номерами

1,В; В,А; A,С; С, N,. прямые и инверсные = вйходь1 последующих If8p разрядоВ соединены. аналогичным образом с входами элементов И последующих средних разрядов 45 с соответствующими номерами.

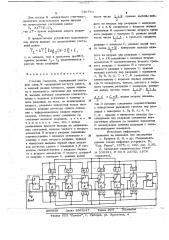

На чертеже изображен счетчик Джонсо-. на на восемь разрядов.

Счетчик содержит регистр 1 сдвига с разрядами 1 - 1,1 - 2, 1 - 3, 1 — 4,1- 50

- 5,1 - 6, 1 — 7,1 - 8; элементы И

2- 1, 3-1,..., 7- 1; 2-2, * 3 — 2,..., 7 — 2 тактовую шину 9.

Тактовая шина 9 с oåäèíåíå со счетными входами разрядов 1 - 1, 1 - 2,...,15

1 - 8, инверсный выход последнего из которых соединен с информационным вхо-! дом разряде 1 — 1; входы установки в

lo

Номер первого среднего разряда

1 - 4 определен целой частью числа

1 а 8 номера второго срелнего раеря2

1 — 2 и третьего среднего разряда 1 -6 определены соответственно целыми частямя чясел 1 е 4 я 4 + 8, номера

2 2 четвертого среднего разряда 1 — 3, пятого среднего разряда 1 — 5 и шестого среднего разряда 1 — 7 определены соответственно целыми частями чисел

3+44+6,н6+8 .2 2 2 Предлагаемое устройство беэ наличия сбоев функционирует как обычный счетчик Джонсона. При состоянии

00000001 и наличии сбоя, например, в разряде 1 - 1 счетчик Джонсона переходит в состояние, относящееся к истинному циклу работы в следующей последбвательности: 10000001 -+ 100100014

11010101 1111111

В устройстве-прототипе при возникновении подобного сбоя последовательность состояний будет следующей:

10000001 11000001 — 11100001.- "

13,110001 -4- 11111001 --" 11111101-8.

11111111.

746 (8

11ля случая М -разря диого счетчика- ), прототипа максимальное время выхода из запрещенных состояний равно:

T) «Л ) (М 2)) с где Ь Р- время коррекции одного разря5 да.

В предлагаемом устройстве.максимальное время выхода из запрещенных состоГ яний равно

)2 --ЛТ((ОД (X-2)) е т. е. меньше, чем в прототипе прий 5, причем разница Т - Т увеличивается с ростом числа разрядов.

1S

Формула изобретения

Счетчик 1(жонсона, содержащий тактовую шину, Й -разрядный регистр сдвига, 20 в каждый разряд которого, кроме первого и последнего, включены два элемента

И, выходы которых соединены соответственно с вкодами установки в единицу и ноль разрядов, во всех, за исключением 25 второго, разрядах инверсный выход последнего разряда регистра сдвига соединен с информационным входом первого разряда, тактовая шина соединена со счетными входами разрядов, о т л и - 30 ч а ю шийся тем, что, с целью уменьшения времени выхода иэ запрещенных состояний, выходы первого и второго элементов И второго разряда соединены соответственно с входами установки в З единицу и ноль второго разряда, прямые и инверсные выкоды первой пары разрядов регистра сдвига с номерами 1,М соединены соответственно с входами первого и второго элементов И первого средне- го paapsma с номером А, равным целой

6 части числа 1 + М, прямые выходы каж2 дого из вторых пар разрядов с номерами

1, А и А, Я соединены с входами первых элементов И соответственно второго среднего разряда с номером В, равным целой части числа 1 + А, и третьего среднего

2 разряда с номером С, равным целой части числе А + Х, инверсные выхоцы кеж2 дого из вторых пар разрядов с номерами

1, А и АМ соедийены с входами вторых элементов И соответственно второго среднего разряда с номером В и третьего среднего разряда с номером С, прямые выходы третьих пар разрядов с номерами

1, В; В, А; А, С и С, М соединены соответственно с входами первых элементов И четвертого, пятого, шестого и седьмого средних разрядов с номерами, равными целым честим чисел +В, В + А

2 2

А + C и С + И, виолы вторых елемен2 2 тов И которых соединены соответственно с инверсными выходами третьик пар разрядов с номерами l, В; В, А; А, С;

С, М, прямые и инверсные выходы по»следующих пар разрядов соединены аналогичным образом со входами элементов

И последующих средних разрядов с соответствующими номерами.

Источники информации, принятые во внимание при экспертизе

1, Букреев И. Н. и др. Микроэлектронные схемы цифровых устройств. М., "Сов. Радио, 1975, с. 202, рис. 5.35.

2. Авторское свидетельство СССР

N. 539381, Н 03 К 23/02, 1976 (прототип) .

ЦНИИПИ Заказ 3965/47 Тираж

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4