Фазовый дискриминатор

Иллюстрации

Показать всеРеферат

о п -й4дты к

И ЗОБРЕТЕНия

Союз Советских

Социалистических

Республик (iii 746862

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву

{22) Заявлено 02.12.77 (21) 2549923/18-21 (51) М; Кл.

Н 03 D 13/00 с присоединением заявки РЙ (23) Приоритет

Опубликовано07,0780. Бюллетень ¹25 (5З) УЙК 621.396 (088.8) дата опубликования описания 10.07.80

В. А. Гончарук, О. M. Дерфель и A. H Олейнико (72) Авторы изобретения (7I) Заявитель (54) ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к измерительной технике, оно предназначено для определении знака и величины сдвига . фаз двух импульсных сигналов.

Известен фазовой дискриминатор, со5 держаший формирователь прямоугольных импульсов, два триггера, входные и выходные схемы И" Я. Однако этот фазовый дискриминатор обеспечивает работоспособность только при входных импульсах малой длительности с величиной задержки между сигналами, превышаюшей длительность входного импульса.

Известен также фазовый дискриминатор, содержаший два импульсно-фазовых раэличителя, каждый иэ которых состоит из триггера, инвертора и двух логических схем И, и логическую схему ИЛИ, входы которой подключены к выходам соответствуюшей логической схемы И каждого из импульсно-фазовых различителей, на входы которого поданы входные сигналы, а также две линии задержки, каждая из которых включена между

* г

ГевударстванныИ комитет

СССР пю делам нзебретеннй и еткрытнй

2 соответствуюшим входом дискриминатора и входом триггера соответствуюшего импульсно-фазового различителя, а каждый вход дискриминатора подключен непосредственно к входам инвертора и схемы И противоположного импульснофаэового различителя f2).

Однако в этом дттскриминаторе минимальная величина сдвига фаз ограничивается величиной времени линий задержки (т1:л ). При сдвиге фаэ между входными сигналами меньшем, чем

Г сигнал на выходе дискриминатора отсутствует, то есть схема не предназначена для определения величины сдвига фаз, меньшего, чем величина Г„ °

Кроме того, момент выключения выходного сигнала определяется не моментом появления сигнала на "отстеощем входе дискриминатора (что соответствовало бы величине измеряемого сдвига фаэ), а моментом появления этого сигнала на выходе линии задержки, т.е. укаэанная схема имеет погрешность

6862

3 74 формирования длительности выходного . сигнала на величину („

Цель изобретения — расширения диапазона и повышение точности дискриминации

Поставленная цель достигается тем, что в фазовый дискриминатор, содержащий два инвертора, три элемента И, триггер знака, триггер фазы, причем выход первого инвертора подключен к одному из входов второго элемента И, а выход второго инвертора подключен к одному из входов первого элемента И, введены два повторителя-ограничителя длительности импульса, вь|ход одного из

Которых подключен ко- вторбМ Г входу первого элемента И, а выход другого ко второму входу второго элемента И, " IIpH этом выход 11epaoro элемента И соединен с первыми входами триггеров знака и фазы, выход второго элемента И со вторыми входами триггербв знака . и фазы, а третий вход триггера фазы подключен к выходу третьего элемента И, входы которого цодсоединены соответствейно к первому и второму входам устройства.

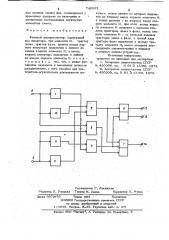

На чертеже представлена структурная схема предлагаемого фазового дискриминатора.

Этот дискрмминатор содержит два, инвертора 1 и 2, три элемента И 3,4 и 5, триггер 6 знака, триггер 7 фазы, две вхддные клеммы 8 и 9, два повторйтещ1- ограничителя 2,0 и 11 длительностй ймпульса, две выходные клеммы

12 и 13 знака и выходную клемму 14 фазы.

Выход первого инвертора 1, вход которого соединен с входной клеммой 8, подключен к одному из вх6дов второго элемента И 4, а выход второго инвертора 2, вход которого соедийен со. второй входной клеммой 9, подключен к одному из входов первого элемента И 3 Повторитель-ограничитель 10 включен между. входной клеммой 8 и первым элементом

И 3, а повторитель- ираничитель 11между входной клеммой 9 и вторым элементом И 4. Выход первого элемента И 3 соединен с одними входами триггеров

6 и 7 знака и фазы, выход второго элемента И 4 — с другими входами триггеров 6 и 7 знака и фазы, а сбросовый вход триггера 7 фазы подключен к выходу третьего элемента И 5, входы которого подсоединены соответственно к первой и второй входным клеммам 8 и 9.

Предлагаемый дискриминатор ра ботает следующим образом.

На входные клеммы 8 и 9 поступают меандровые сигналы одинаковой частоты. Если сигнал на входной клемме 8 опережает сигнал на входной клемме 9, то в момент прихода переднего фронта сйгйала на входную клемму 8 на выходе повторителя-ограничителя 10 формируется короткий импульсный сигнал, по которому через первый элемент

И 3 (на втором входе элемента И 3 присутствует разрешающий потенциал с выхода инвертора 2) триггеры 6 и 7 устанавливаются в "единичное" состояние.

При поступлении второго задерж анного по фазе сигнала на входную клемму 9, срабатывает третий элемент И 5, сигнал с выхода которого переводит в нулевое состояние триггер 7, в результате чего на выходной клемме 14 формируется импульсный сигнал, длительность которого равна сдвигу фаз между входными сигналами. Состояние триггера 6 сохраняется до момента перемейы знака сдвига фаз.

При опережении сигнала на входной клемме 9 триггер 7 устанавливается в единичное", триггер 6 в нулевое состояние по сигналу.с выхода второго

ЗО элемента И 4, на первый вход которого поступает сформированный повторителемограничителем 11 короткий импульс, а на второй вход - разрешающий потенциал с выхода инвертора 1. Формирование выходного сигнала на выходной клемме 14 осуществляется аналогично описанному выше установкой триггера 7 в нулевое состояние при поступлении на входную клемму 8 Отстающего сигнала и совпаде40 нии обоих входных сигналов на третьем элементе И 5.

Введение в фазовый дискриминатор повторителей эграничителей 1О и 11 обеспечивает включение выходного сигнала (ха4 рактеризующего величину сдвига фаз) сразу же цри поступлении опережающего входного сигнала, Организация включения триггера 7 фазы по сигналам от первого и второго

50 элементов И 3 и 4 (входы которых управляются от выходов инверторов 1 и 2) обеспечивает блокировку повторного включения триггера 7 при поступлении отстающего входного сигнала, а наличие третьего элемента И 5 обеспечивает при этом формирование сигнала выключения триггера 7, в результате чего повышает| ся точность измерения достаточно ма5

Формула изобретения

Фазовый дискриминатор, содержащий два инвертора, три элемента И, триггер знака, триггер фазы, причем выход пер- Î вого инвертора подключен к одному из входов второго элемента И; а выход второго инвертора подключен к одному из входов первого элемента И, о т л и— ч а ю щ и Й с я тем, что, с Белью рас- 35 ширения диапазона и повышения точности дискриминапии,, в него введены два повторителя-ограничителя длительности им5 74 лых величин сдвига фаз, соизмеримых с временами задержек на включение и выключение составляющих логических элементов схемы.

862 пульса, выход одного из которых подключен ко второму входу первого элемента И, а выход другого — ко второму входу второго элемента И, при этом выход первого элемента И соединен с первыми входами триггеров знака и фазы, выход второго элемента И вЂ” со вторыми входами триггеров знака и фазы, а третий вход триггера фазы подключен к выходу третьего элемента И входы которого подсоединены соответственно к первому и второму входам устройства .

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 450308, кл. Н 03 D 13/00, 1973.

2. Авторское свидетельство СССР № 450309, кл. Н 03 D 13/00, 1973.

Составитель С. Лукинская

Редактор Л. Ушакова Техред М. Петко Корректор И. Муска

Заказ 3972/50 Тираж 995 Подписное

11НИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ЛПП Патент, г. Ужгород, ул. Проектная, 4