Селектор импульсов

Иллюстрации

Показать всеРеферат

Рсе;.о .: .:..т

О П И"С А Й-И Е

ИЗОБРЕТЕН ИЯ

<>i) 7468Я9

Союз Советскик

Социалистическии

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (й ) Дополнительное к авт. свид-ву(22) Заявлено28. 12.77 (2! ) 2561059/18-21 с присоединением заявки И— (51)М. Кл.

Н 03 К 5/18 (23) Гасударственный.комитет

СССР па делам изобретений и открытий

Приоритет.

Опубликовано 07.07.80. Бюллетень Рй 25 (53) УДК 621

:37 4(088,8) Дата опубликования описания 08.07.80.

А. И. Воробьев и М. В. Акинин (72) Авторы изобретения (7I) Заявитель (54) СЕЛЕКТОР ИМПУЛЪСОВ

Предлагаемый селектор импульсов предназначен для использования в радиотехнических установках различного назначения, в частности для выделения периодической последовательности импульсов на фоне хаотических помех, а также для разделе-.

Ф 1 ния совокупности серий импульсных сигналов с различными частотами следования.

Известен селектор импульсов, содержапптй блок задержки, пересчетную схему и цепь сброса, вход которой соединен с первым и вторым входами элемента совпадения, а выход — с нулевым входом триггера (1) .

Недостатком известного селектора импульсов является низкая надежность его.

Бель изобретения — повышение надежности селектора. 20

Поставленная пель достигается тем, что в селектор импульсов, содержаший блок задержки, пересчетную схему, вход и цепь сброса которой соединены соот

2 ветственно с первым и вторым входами элемента совпадения, а выход — с нулевым входом триггера, в негб введены элементы ИЛИ-НЕ и И-НЕ, выход роследнего из которых соединен с первым входом блока задержки, второй вход которого подключен к выходу элемента

ИЛИ-НЕ, первый вход которого соединен с выходом пересчетного элемента а второй вход — с выходной шиной, с выходом элемента совпадения и с единичным входом триггера, нулевой выход которого подключен к первому входу элемента И-НЕ, второй вход которого подключен к входной шине, а единичный выход триггера подключен к третьему входу блока задержки, выход которого подключен к первому входу .элемента совпадения.

Блок задержки этого селектора состоит иэ генератора тактовой частоты, выход которого подключен к счетным входам триггеров регистра сдвига, первого и второго триггера, 1 -вход которого соединен с единичным выходом триггера

3 7468 старшего разряда регистра сдвига и одт ним из 1 -входов первого триггера, второй g- вход которого подключен к третьему входу блока задержки, К-вход — к нулевому выходу триггера старшего разряда регистра сдвига и к входу второго триггера, вход установки нуля регистра сдвига которого соединен со вторым вхо дом блока задержки, щервый вход которого подключен ко входу установки еди- 10 ницы первого триггера, единичный и нулевой выходы которого соединены соответственно с $ - и К-входами триггера младшего разряда регистра сдвига.

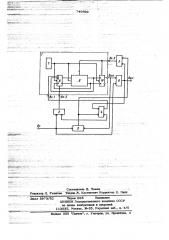

На чертеже представлена структурная 15 схема селектора импульсов.

Селектор импульсов содержит блок

1 задержки, второй вход которого соединен с выходом элемента И-НЕ 2, первый вход которого подключен к входу св- 20 лектора в цепи сброса пересчетной схемы

3. Выход пересчетной схемы соединен с нулевым входом триггера 4, единичный

-вход которого подключен к второму входу алемента ИЛИ-НЕ 5 и выходу элемента 25 совпадения 6. Кроме того, блок 1 задержки имеет генератор 7 тактовой частоты, -"выход которого соединен с счетными входами триггера 8, триггера регистра сдвига 9 и триггера 10. J — и К - входы 30 триггера 10 подключены соответственно к единичному и нулевому выходам триггера старшего разряда регистра сдвига, а также второму 1 -входу и К-входу триггера 8. 35

Нулевые входы триггера 10, и триггеров регистра сдвига 9 соединены с третьим входом блока 1 задержки, который является выходом элемента ИЛИ-НЕ

5. Первый и второй входы блока эадерж40 ки подключены соответственно к первому g -входу и единичному входу тригге4 ра 8. Единичный и нуле вой выходы триггера 8 соединены соответственно 145 и К-входами триггера младшего разряда регистра сдвига 9, Единичный выход триггера 10 подключен к выходу блока 1 задержки. Первый вход алемента совпадения 6 соединен с входом пересчетной схемы 3 и выходом блока 1 задержки.

Второй вход элемента совпадения 6 подключен к цепи сброса пересчетной схемы

3, выход которой соединен с первым входом алемента ИЛИ-НЕ 5. Единичный

55 и нулевой выходы триггера 4 соответственно подключены к первому входу блока

1 задержки и второму входу элемента

И-НЕ 2.

99 4

Селектор импульсов работает следующим образом.

В исходном состоянии триггеры 8 и

10 и триггеры регистра сдвига 9 находятся в нулевом состоянии, так как ге/ нератор 7 тактовой частоты все время вырабатывает импульсы сдвига, а триггер 8 заблокирован по первому 1„-входу нулевым потенциалом с единичного выхода триггера 4. (обратная связь регистра сдвига разомкнута).

Импульсы входной последовательности проходят через алемент И-НЕ 2, который имеет разрешение по второму входу на единичный вход триггера 8, устанав лйвая его в единичное состояние. Одновременно тактовыми импульсами с генератора 7 происходит сдвиг этой информании по разрядам регистра, Точность селектирования определяется частотой следования 7 импульсов генератора 7 тактовой частоты, которая подсчитывается по формуле

Р = (N+4) ,где Й вЂ” количество триггеров в регистре сдвига, — частота следования импульсов селектируемой последовательности.

Выходные импульсы с триггера 10 и импульсы входной последовательности поступают на соответствующие входы 6 эл мента совпадения, выделяющего импульсы заданной частоты из входного сигнала в

Первый импульс с элемента 6 совпадения, пройдя через элемент ИЛИ-НЕ

5, осуществляет сброс триггеров регистра сдвига 9 и триггера 10. Кроме того, атим импульсов опрокидывается триггер

4, в результате чего с нулевого выхода этого триггера выдается запрет на элемент И-HE 2 (дальнейшая запись информации в регистр сдвига не происходит) а с единичного выхода — выдается разреI шение на первый — вход триггера 8 (кольцевая обратная связь регистра сдвига замыкается) и логическая единица, записанная до атого в триггере 8, будет циркулировать по регистру сдвига Из ра ряда в разряд с частотой следования импульсов генератора тактовой частоты до окончания импульсной последовательности.

Очередные прямоугольные импульсы на единичном выходе триггера 10 будут появляться с частотой следования селектируемых импульсов и при их совпадении на алементе 6 будет происходить выделение

746899 6

Формула изобретения и пульсов полезного сигнала из входной посл довательности.

Одновременно прямоугольные импульсы с триггера 10 поступают на пересчетную схему 3 и прь отсутствии совпадения этого импульса с импульсом полезного сигнала, что соответствует пропуску импульсов в селектируемой последовательности, пересчетная схема подсчитывает число пропущенных импульсов. Причем

J если во входной последовательности имеются пропуски полезного сигнала и при этом их число не превышает коэффициента пересчета схемы 3, то это не нарушает работы селектора. Если число пропущенных импульсов превышает коэффициент пересчета схемы 3, последняя подсчитывает заданное число пропусков и вырабатывает импульс, которым осущест вляется сброс триггеров 4 и 10 и триг- 20 геров регистра сдвига 9 в нулевое состояние. Селектор снова готов к работе.

С поступлением первого после пропуска импульса последовательности пересчегная схема 3 сбрасывается и производится 25 запуск селектора.

Предлагаемый селектор импульсов содержит лишь девять функциональных узлов. При этом сохраняются все электрические характеристики прототипа, а имен- ЗО но: высокая надежность селектирования при наличии пропусков в селектируемой последовательности; исключение ложного срабатывания се- И лектора при наличии помех как внутри, так и перед селектируемой последовательноCT bIO.

Это позволяет сократить габариты, уменьшить потребление энергии и снизить 4© стоимость селектора.

Исходя из принципа построения предлагаемый селектор может быть полностью реализован на одной системе элементов, например импульсно-потенпиаль- 45 ной системе элементов (транзисторнотранзисторная логика), а благодаря в его составе только одного функционального узла — генератора тактовой частоты требующего предварительной настройки, значительно упроцается настройка и регулировка селектора.

1. Селектор импульсов, содержащий блок задержки, пересчетную схему, и ход и цепь сброса которой соединены соответственйо с первым и вторым входами элемента совпадения, а выход — с нулевым входом .триггера, о т л и ч а ю— шийся тем, что, с целью повышения надежности селектора, в него введены элементы ИЛИ-НЕ и И-НЕ, выход посЯ леднего из которых соединен с первым входом блока задержки, второй вхоц которого подключен к выходу элемента

ИЛИ-НЕ, первый вход которого соединен с выходом пересчетной схемы, а второй вход — с выходной шиной, с выходомэле-мента совпадения и с единичным входом триггера, нулевой выход которого подключен к первому входу элемента И-НЕ

> второй вход которого подключен к входной шине, а единичный выход триггера подключен к третьему входу блока задержки, выход которого подключен к первому входу элемента совпадения.

2. Селектор импульсов по п. 1, о т— личающи йся тем, чтоблок задержки состоит из генератора тактовой частоты, выход которого подключен к счетным входам триггеров регистра сдвига, первого и второго триггера, -вход которого соединен с единичным. выходом триггера старшего разряда регистра сдвига и одним из Т -входов первого триггера, второй $ -вход которого подключен к третьему входу блока задержки, К-вход к нулевому выходу триггера старшего разряда регистра сдвига и к входу. второго триггера, вход установки нуля регистра сдвига, соединен со вторым входом блока задержки, первый вход которого подкжочен ко входу установки единицы первого триггера, единичный и нулевой выходы которого соединены соответственно с j — и К-входами триггера младшего разряда регистра сдвига.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство по заявке

М 2413041/21, кл. Н 03 К 5/18

197 6.

746899 г

Составите»ь В Чижов

Редактор Л, Ушакова Танкред. Ж. Кастелевич Корректор Е. Пап

Заказ 3973I51 Тираж 995 Подписное

0НИИПИ Государственного комитета СССР по делам изобретений и открытий .

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, у». Проектная, 4