Анализатор вершины импульсных сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАНИНА .ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнх

Социалистическик

Республик 746906

3 T (4 (61) Дополнительное к ввт. свил-ву (22) Заявлено 04,05.78 (21) 2611621/18 21 с присоелинением заявки J% (23) Приоритет (51)M. Кл.

Н 03 К 5/20

Гесудврстввиный комитет

II0 делам изобретений и еткрытяй

Опубликовано 07.07.80. Бюллетень J% 25

Дата опубликования описания 07.07.80 (5З) УДК 621.374,,33 (088.8) (72) Авторы изобретения

В. Т, Осьминин и В. С.Васильев (71) Заявитель (54) АНАЛИЗАТОР ВЕРШИНЫ ИМПУЛЬСНЫХ

СИГНАЛОВ

Изобретение относится к области радиоэлектроники и измерительной техники.

Анализатор вершины импульсных сигналов предназначен, в частности, для использования в электроизмерительных установках для контроля параметров полупроводниковых приборов, 5 где анализатор применяется в узле разбраковки испытуемых приборов.

Известно устройство, содержащее последовательно соединенные блок суммирования, преоб1О раэователь переменного напряжения в постоянное, компаратор и триггер с блоком сброса в исходное состояние, электронные ключи, блок управления (1), Указанное устройство позволяет расширить частотный диапазон обнаруживаемых искажений до 1 кГц. Однако оно неспособно обнаружить искажения вершины импульсных сигналов в случаях, когда частота генерации соизмерима с длительностью самого импульса, так как при о этом резко уменьшается чувствительность устройства.

Другим недостатком является то, что срабатывание триггера зависит только от амплитуды н частоты генерации н не зависит от уровня постоянной составляющей импульса, в результате чего устройство невозможно настроить на обнаружение импульсов с искажениями плоской вершины, уровень которых превышает заранее заданный, выраженный в процентах относительно уровня исследуемого сигнала.

Таким образом, явно выраженными недостатками, снижающими эффективность использования известного устройства, являются ограниченный частотный диапазон обнаруживаемых искажений и невозможность перестройки его в широких пределах иа обнаружение импульсов с определенным уровн м искажений вершины.

Целью изобретения является расширение функциональных воэможностей путем обнаружения искажений плоской вершины импульсных сигналов, превышающих заданный уровень, а также расширение частоп-oro диапазона обн руживаемьтх искажений в сторону нижних частот.

Ляя достижения укаэанной цепи в анализатор вершины импульсных сигналов, содержащий последовательно соединенные блок суммирования, преобразователь переменного напряжения в постоянное, компаратор и триггер с блоком сброса в исходное состояние, электронные ключи, блок управления, выходы которого раздельно подключены к управляющим входам блока сброса электронных ключей, подключенных выходами к блоку суммирования, а вход пер5 ваго электронного ключа соединен са входом блока управления и шиной входчых сигналов, введены аналоговый элемент памяти и блок управленйя элементом памяти, причем вход ана- 1а логоваго элемента памяти подключен ко входу блока управления элементом памяти, выходом соединенного с управляющим входом аналогового элемента памяти и шиной входных сигналов, а выход — ко входу второго электронного 15 ключа и второму входу кампаратора.

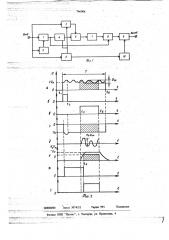

На фиг. 1 приведена функциональная схема анализатора; на фиг. 2 — временные диаграммы, поясняющие принцип его работы.

Анализатор содержит аналоговый элемент 1 20 памяти с блоком 2 управления, электронные ключи 3 и 4 с блоком 5 управления, блок 6 суммирования, преобразователь 7 переменного напряжения в постоянное, компаратар 8 и триггер 9 с блоком 10 сброса в исходное 25 состояние.

Аналоговый элемент 1 памяти предназначен для запоминания постоянного уровня анализируемого сигнала, поступающего на его вход, являющийся входом анализатора. Аналоговый за элемент 1 памяти представляет собой операционный усилитель (ОУ) с коммутируемым входом, в цепи обратной связй которого включен запоминающий конденсатор. Первый вход аналогового элемента 1 памяти подключен ко входам 35 анализатора, блоков 2 и 5 управления памятью и ключами соответственно и электронного ключа 3, второй вход — к выходу блока 2 управления памятью, а выход — к сигнальному входу электронного ключа 4 и второму входу камна- 4а ратора 8.

Блок 2 управления памятью может быть выполнен на одновибратаре, электронные ключи

3 и 4 — на палевых транзисторах. Управляющие входы электронных ключеи 3 и 4 подклю- 45 чены к выходу блока 5 управления электронными ключами, а их выходы — ко входам блока 6 суммирования, блок 5 управления электронными ключами предназначен для формирования задержанного относительно начала вход-5а його импульса сигнала, управляющего работой электронных ключей 3 и 4. Блок 5 управления. представляет собой два последовательно включенных однавибратора. Блок 6 суммирования выполнен на операционном усилителе и предназначен для выделения усиления искажений плос.

° кой вершины анализируемого импульса. Выход блока 6 суммирования соединен со входом преобразователя 7 переменного напряжения в

3 746906 4 постоянное, представляющим собой пиковый детектор, предназначенный для преобразования переменного сигнала, поступающего на его вход с выхода блока 6 суммирования, в постоянный по размаху амплитуды. Компаратор 8 предназначен для сравнения сигналов, поступающих на его входы с выходов аналогового элемента 1 памяти и преобразователя 7. Компаратор 8. может быть выполнен на операционном усилителе, Триггер 9 выполнен в виде RS-триггера и прецназначен для вырабатывания сигнала признака искажений вершины импульса, Блок

10 сброса триггера в исходное состояние предназначен для формирования сигнала, возвращающего триггер s исходное состояние. Он может быть выполнен в виде дифференцирующей цепи, подключенной входом к выходу блока 5 управления электроннымй ключами.

Работа анализатора происходит следующим образом.

Анализируемый импульс длительностью Т с искаженной плоской вершиной поступает в момент времени tt (фиг. 2а) на входы аналогового элемента 1 памяти, электронного ключа 3 и блоков 2 и 5 управления памятью и электронными ключами соответственно. При этом блок 2 управления памятью вырабатывает импульс длительностью tg — 1 (фиг. 2б), который, поступая на управляющий вход аналогового элемента 1 памяти, переводит его в ьймент

tq в режим запоминания уровня входного сигнала и хранения этого уровня в течение времени, равного длительности Т входного импульса.

Сигнал на выходе аналогового элемента 1 памяти показан на фиг. 2 г. Передним фронтом входного импульса запускается первый одио.вибратор блока 5 управления электронными ключами, который, в свою очередь, в момент времени t3 запускает второй одновибратор блока 5. На выходе блока 5 формируется импульс длительностью tq — 1з, меньшей длительности аьилизируемого импульса (фиг. 2 а, в), что позволяет исключить влияние переходных процессов при нарастании и спаде анализируемого импульса на работу анализатора. Импульс с выхода блока 5 управления поступает на входы электронных ключей 3 и 4 и открывает. их.

Через открытые ключи 3 и 4 на входы блока 6 суммирования поступают сигналы длительностью

tq — tq . со входа анализатора — участок входного импульса, а с выхода аналогового элемента 1 памяти — участок импульса противоположной полярности с плоской неискаженной вершиной (на фиг. 2 а, г названные участки заштрихованы) .

Блок 6 суммирования: осуществляет алгебраическое сложение указанных сигналов, в результате чего выделяются и усиливаются в К„ раз искажения плоской вершины, где К

5 746906 6

L коэффициент усиления блока 6 с м уммирования. пульса любой формы, что качественно отличает

Сигнал на выходе блока 6 с мми ования и у мирования пока- его от устройства — прототипа, которое выявляе зан на фиг. 2 д. Преобразователь 7 преобразует лишь искажения в виде модулированного сигэтот сигнал в постоянное напряжение по уровню нала определенной амплитуды и частоты. Частотразмаха 2MIUIH QHblx 3va em . При этом на вы- ный диапазон в предлагаемом анализаторе эначиходе преобразователя 7 вырабатывается ностоян- тельно расширен в сторону нижних частот и. ный уровень напряжений И, соответствующий Фактически определяется длительностью анализиабсолютному значению искажений, усиленных в pyeMoro импульса, в то время как в устройствеКо раз (фиг. 2е). Компаратор 8 осуществляет прототийе практически невозможно обнаружить сравнение сигнала, полученного с выхода преоб- >р искажения частоты, соизмеримой с длительносразователя 7 (фиг. 2е) с сигналом, поступаю- тью анализируемого импульса. щим с выхода аналогового элемента 1 памяти, уровень которого соответствует уровню постоянной составляющей анализируемого импульса с

Формула изобретения точностью величины К, определяемой соотно- 15 Анализатор вершииы импульсных сигналов, шепнем:

UH содержащии носледовательно соединенные блок суммирования, преобразователь переменного где 0„— величнйа абсолютного размаха ампли- напряжения в постоянное, компаратор и триг туды искажений; гер с блоком сброса в исходное состояние, 0 — в

„— величина постоянного уровня анализи- >О электронные ключи, блок управления, выходы которого раздельно подключены к управляющим

К вЂ” действительное значение уровня иска- входам блока сброса и электронных ключей, подключенных выходами к блоку суммирования, а вход первого электронного ключа соедизаданного значения, определяемого коэффици- gg нен ср входом блока управления и шиной ентом усиления К, т. е. К ) Ко, компаратор 8 входных сигналов, отличающийся срабатывает (фиг. 2 ж, момент в емени t u перебрасывает т игге 9 в п отивоположное устойчивое состояние (фиг 2 з) . Возвращение плоской вершины импульсных сигналов, претриггера 9 в исходное состояние о ояние осутцествляется jg вышающих заданный уровень, а также расшив момент времени с пос едством лока р q р дством блока 10,, рения частотного диапазона обнаруживаемых который срабатывает от заднего фронта выход- искажений в сторону нижних частот, в него ного импульса блока 5 управления ключами. введены аналоговый элемент памяти. и блок

Изменением коэффициента усиления блока 6 управления элементом памяти, причем вход суммирования задают в процентном отношении . аналогового элемента памяти подключен ко входу допустимый уровень искажений вершины им- блока управления элементом памяти, выходом соединенного с управляющим входом аналогового пульса.

fT e р длагаемый анализатор позволяет обнаружи- элемента памяти и шиной входных сигналов, вать искажения вершины импульсных сигналов а выход — ко. входу второго электронного неизвестной амплитуды, превышающие опреде- ключа и второму входу компаратора.

40 ленный уровень, заданный в процентном от- Источники информации P+ ý ношении к уровню постоянной составляющей принятые во внимание при экспертизе анализируемого импульса, При этом устройство 1. Авторское свидетельство СССР по эаявобнаруживает искажения плоской вершины им- ке N 2353072/21, 12.04.78.

74б906

Юо, а

0 e in

Оо о,@ate. 2

ЦНИИПИ Заказ 3974/52

Подписное

Тираж 995

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4