Преобразователь кода в частоту следования импульсов

Иллюстрации

Показать всеРеферат

(,746921

ОП ИСАЙ ИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) ДополнительнОе к авт. саид-ву(22) Заявлено 30,12.74 (21) 2090378/18«21 с присоединением заявки.%(23) П риоритет

Опубликовано 07.07.80. Бголлетень № 2->

Дата опубликования описания 10.07.80 (51)М. Кл.

Н 03 К 13/20

Государстввииый комитет

СССР ло делам изобретеиий и открытий (53 ) УД К 681. 325 (088.8) (72) Автор изобретения

В, Ф. Митина

Новочеркасский орцена Трудового Красного Знамени политехнический институт имени Серго Орджоникидзе (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ

С ЛЕ ЛОВА НИ Я И М ПУЛ ЬС ОВ

Изобретение относится к области дискретно-аналоговой техники, а именно, к частотно-импульсным системам.

Известен преобразователь кода в частоту следования импульсов, содержащий в контуре регулирования управляемый

5 аналоговым сигналом, пропорциональным входному коду, генератор выходной частоты, у которого в цепи обратной связи включен блок сравнения образцовой час-. го таты и частоты, пропорциональной выходной частоте преобразователя и обратной пропорциональной значению входного кода Г11 .

Такой преобразователь имеет низкое быстродействие из-за большой инерционности цепи обратной связи.

Наиболее близким техническим решением к данному изобретению является преобразователь, который соцержит генератор образцовой частоты, устройство преобразования входного кода в аналоговый сигнал, управляемый генератор импульсов, на выходе которого включен уп2 равляемый делитель частоты с коэффициентом деления, пропорциональным вхоцному коду, блок сравнения частот, оцин вход которого соединен с выходом управляемого делителя частоты, а второй.с выходом генератора образцовой частоты, накапливающий сумматор ошибки и суммирующий элемент, один вход которого соединен с выходом устройства преобразования входного кода в аналоговый сигнал, второй вход - с выходом накапливающего сумматора ошибки, а выходсо входом управляемого генератора частоты 2) .

Недостатком известного преобразователя является низкая динамическая точность и невысокое быстродействие.

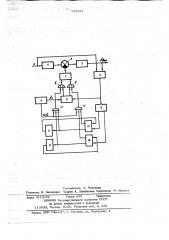

Цель изобретения — повышение динамической точности и быстродействия преобразователя, Поставленная цель достигается тем, что в преобразователь кода в частоту следования импульсов, соцержащий генемирующий элемент 8, триггер со счетным входом 9, включенный на выходе управляемого делителя частоты, два триггера с раздельными вхоцами 10, два элемента задержки 11, два логических элемента

И 12. Импульсные вхоцы элементов 12 подключены к цополнительному выходу генератора 4. Потенциальные входы первого элемента 12 соединены с первыми

10 выходами триггеров 10, а потенциальные входы второго элемента 12 — со вторыми выходами тех же триггеров 10.

Выход каждого элемента 12 соецинен со входом одного из элементов 5. Вто15 рой вход каждого логического элемента

ИЛИ 5 соединен с одним из выходов блока сравнения частот 6. Выходы элементов 5 соединены со входами накапливающегоо сумма тора ош ибки 7, вы ход которо20 ro соединен со входом суммирующего элемента 8. Второй вход суммирующего элемента 8 соединен с выходом устройства

1. Выход суммирующего элемента 8 соединен со входом управляемого генерато25 ра 2. Каждый элемент задержки 11 включен между первым выходом и вторым входом триггера 10.

Преобразователь работает следующим

30 образом.

Входной коц N поступает на входы устройства 1. Аналоговый сигнал с выхода устройства 1 через суммируюший элемент 8 подается на вход управляемо-. го генератора 2, на выходе которого ус35 танавливается приближенное значение выходной частоты т пропорциональное входному коду, Частота 1, делится в управляемом делителе 3 на число, пропорциональное входному коду. Выходная

40 частота управляемого делителя 3 сравнивается блоком 6 с образцовой частотой и одновременно подается на счето ный вход триггера .9, который является

45 входом устройства выделения разности периодов образцовой частоты 1 и частоты с выхода управляемого целителя 3.

Триггер 9 поочередно устанавливает триггеры 10 в состояние, при котором открываются элементы 12. В этом состоянии триггеры 1 0 находятся постоянное время, определяемое элементами задержки

1 1 и равное периоду образцовой частоты . Злементы 12 будут открыты о ч ц.< часы; ты т, в течение времени, равного разности периодов образцовой частоты и частоты с эыкоца. управляемого целителя 3. Если эта разность больше периода частоты rn9z, то на выходе одного

3 746921 ф ратор образцовой частоты, устройство преобразования входного кода в аналого- вый сигнал, управляемый генератор импульсов, на выходе которого включен управляемый делитель частоты с коэффициентом деления, пропорциональным входно му коду, блок сравнения частот, один вход которого соединен с выходом управляемого делителя частоты, а второй - о выходом генератора образцовой частоты, накапливающий сумматор ошибки и суммирующий элемент, один вход которого соединен с выходом устройства преобразования входного кода в аналоговый сигнал, второй вход — с выходом накапливающего сумматора ошибки, а выходсо входом управляемого генератора частоты введен триггер со счетным входом, — два триггера с раздельными входами, два элемента задержки, два логических элемента И и два логических элемента

ИЛИ, причем выход управляемого делителя частоты соединен со входом триггера со счетным входом, соединенного выходами с первыми входами триггеров с раздельными входами, в каждом из которых первый выход соединен через элеМент задержки со вторым входом, первые входы логических элементов ИЛИ соединены с выходом блока сравнения частот, второй вход каждого логического элемента ИЛИ соединен с выходом соответствующего логического элемента И, потенциальные входы первого логического элемента И Соединены с первыми выходами триггеров с раздельными входами, потенциальные входы второго логического элемента И соединены со вторыми выходами тех же триггеров, выходы логических элементов ИЛИ соединены со входами накапливающего сумматора ошибки, а дополнительный выход генератора образцовой частоты соединен с импульсными входами логических элементов И.

На чертеже приведена структурная схема преобразователя.

Преобразователь содержит устройство преобразования входного кода в аналоговый сигнал 1, управляемый генератор импульсов 2, выход которого соединен со входом управляемого делителя частоты 3, коэффициент деления которого пропорцио- нален входному коду, генератор образцовой частоты 4, — с выхода которого снимается образцовая частота ; а с дополнительного выхода — частота п 1, где коэффициент m)7 1, два логических элемента ИЛИ 5, блок сравнения частот

6, накапливаюший сумматор ошибки 7, сум»

5 7 из элементов 12 за один период образцовой частоты, появится пачка импульсов частоты т, количество импульсов в которой пропорционально разности периодов образцовой частоты .1 и частоты с выкода управляемого делителя 3.

Сигнал с выхода каждого элемента

12 подается через свой элемент 5 на

/ вход накапливающего сумматора ошибки

7, выходной сигнал которого в качестве отрицательной обратной связи поступает через суммирующий элемент 8 на вход управляемого генератора 2. Если разность периодов образцовой частоты и частоты с выхода управляемого целителя 3 меньше периода частоты m E то регулирование происходит только по сигналу с выхода блока сравнения частот 6.

Процесс регулирования заканчивается при равенстве частоты с выхода управляемого делителя 3 и образцовой частоты, т. е. когда íà выходе преобразова-; теля установится частота F y = И

Преимущество предлагаемого преобразователя состоит в том, что создается возможность значительно сократить время установления выходной частоты пре образователя и уменьшить динамическую погрешность при сохранении высокой статической точности.

Преобразователь. кода в частоту сле- 35 дования импульсов, содержащий генератор образцовой частоты, устройство преобразования входного кода в аналоговый сигнал, управляемый генератор импульсов, на выходе которого включен управ- 4р ляемый делитель частоты с коэффициентом деления, пропорциональным входному коду, блок сравнения частот, один вход которого соединен с выходом управляемого делителя частоты, а второй - с вы- 45

Формула изобретения

46921 6 ходом генератора образцовой частоты, накапливающий сумматор ошибки и суммирующий элемент, один вход которого соединен с выходом устройства преобраэования входного кода в аналоговый сигнал, второй вход - с выходом накапливающего сумматора ошибки - а выход - со вкодом управляемого генератора частоты, о т— л и ч а ю шийся тем, что, с целью

)p повышения быстродействия и динамической точности, в преобразователь введены триггер со счетным входом, два триггера с раздельными входами, два элемента задержки, два лргических элемента И и

15 два логических элемента ИЛИ, причем выход управляемого делителя частоты соединен со входом триггера со счетным входом, соединенного выходами с первыми входами триггеров с раздельными входа2О ми, в каждом из которых первый выход соединен через элемент задержки со вторым входом, первые входы логических элементов ИЛИ соединены с выходом блока сравнения частот, второй вход каждо25 го логического элемента ИЛИ соединен с выходом соответствующего логического элемента И, потенциальные входы первого логического элемента И соединены с первыми выходами триггеров с раэдельЗО ными входами, потенциальные вкоды второго логического элемента И соединены со вторыми выходами тех же триггеров, выходы логических элементов ИЛИ соединены со входами накапливающего сумматора ошибки, а дополнительный выкод генератора образцовой частоты соединен с импульсными входами логических элементов И.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

% 341159, кл. Н 03 К 13/02, 1972.

2, Авторское свидетельство СССР

М 278249, кп. Н 03 К 13/02, 1970 (прототип). (° 5

746921

Составитель А. Вентелев

Редактор Н. Зинзикова Texpeg А. Щепанская Корректор N, Шароши

Заказ 4113/22 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4