Делитель частоты

Иллюстрации

Показать всеРеферат

пятен; H а

Союз Советскик

Социалистическим

Ресттубпии

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6 I ) Дополнительное к акт. свил-ву (22) Зая влено 19.12.77 (21) 2554880Д8-21 с присоединением заявки Ж (23) Приоритет— (51)М. Кл.

Н 03 К 23/02

Гееудеретеенный комитет

СССР

Опубликовано 07.07.80. Бюллетень М 25

Дата опубликования описания 07.07.80 не деви нзабретенкй и етнритнй (53) УДК 621374. .44(088 8) (72) Автор изобретения

В. И. Лобанов (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ

Изобретение относится к импульсной тех- нике, оно может быль использрвано в авто- е матике, измерительной и вычислительной технике для построения пересчетных схем с дробным коэффициентом деления.

Известно пересчетное устройство, состоя5 щее из пересчетной схемы, дискретных и ло- . гических схем (1j. В этам устройстве реализуется дробный коэффициент пересчета с ошибкой положения выходных импульсов по от10 ношению к импульсам требуемой выходной последовательности, не превосходящей половины периода входной частоты, для чего предлагается из входной последовательности импульсов на выход устройства пропускать только т% те, которые близко отстоят от импульсов требуемой выходной последовательности. Однако такое устройство не обеспечивает точного деления частоты. Кроме того, структура пересчетного устройства зависит от выходной частоты.

Наиболее близкий по технической сущности к изобретению делитель частоты с дробным переменным коэффициентом деления, содержащий декадные счетчики, схемы совпадения, построенные на элементах И-НЕ и инверторах, элементы ИЛИ, триггеры и делитель, составленный из трех декад с переменным коэффициентом деления 12}.

Однако и это устройство не обеспечивает точного деления частоты, которое может быть получено при подключении к устройству филь- . тра, выделяющего первую гармонику выходной частоты

Цель изобретения — повышение точности деления.

Цель достигается тем, что в делителе частоты импульсов, содержащем асинхронные RSтриггеры, ювертор, элементы И вЂ” HE и элементы

И вЂ” ИЛИ вЂ” НЕ, 8 и R входы первого асинхронного RS-триггера подключены к выходам соответственно первого и второго элементов И-НЕ, прямой выход — к первым входам третьего и четвертого элементов И вЂ” НЕ, а инверсный выход — к первым входам пятого и шестого эле ментов И вЂ” НЕ, $ н R входы второго асинхронного RS-триггера соединены. с выходами соответственно третьего и пятого элементов И вЂ” НЕ

3 7 прямой выход — с первыми входами элементов °

И вЂ” ИЛИ вЂ” НЕ, а инверсный выход — со вторыми их входами, S u R входы третьего асинхронного RS-триггера подключены к выходам соответственно первого и второго элементов

И вЂ” ИЛИ вЂ” НЕ, прямой выход —. ко вторым входам четвертого и шестого элементов И вЂ” НЕ, а инверсный выход —. к первым входам первого и второго элементов И вЂ” НЕ, 8 н R входы четвертого асинхронного RS-триттера соединены с выходами соответственно четвертого и шестого элементов И вЂ” НЕ, прямой выход — с третьими входами элементов И вЂ” ИЛИ вЂ” НЕ и со вторым входом второго элемента И вЂ” НЕ, а инверсный выход —.с четвертыми входами элементов И вЂ” ИЛИ вЂ” НЕ и-со вторым входом первого элемента И вЂ” НЕ, прн этом третьи входы первого и шестого элементов И вЂ” НЕ, вто- рой вход пятого элемента И вЂ” НЕ и пятые входы элементов И вЂ” ИЛИ вЂ” НЕ подключены к входной шине непосредственно, а второй вход третьего элемента И вЂ” НЕ, третьи входы второго и четвертого элементов И вЂ” НЕ и шестые входы элементов И вЂ” ИЛИ вЂ” НŠ— через инвертор.

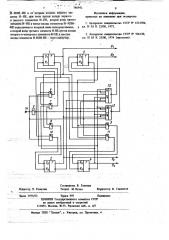

На чертеже представлена структурная электрическая схема делителя частоты.

Делитель частоты содержит асинхроннные

RS триггеры 1 — 4, инвертор 5, элементы И вЂ” НЕ

6-11, элементы И вЂ” ИЛИ вЂ” НЕ 12 и 13. Входная шина 14 делителя частоты соединена со входом инвертора 5, с третьим входом первого элемента И вЂ” НЕ 6, выход которого соединен с S-входом первого триггера 1; с входом первого элемента И вЂ” ИЛИ вЂ” НЕ 12,выход которого соединен с S входом третьего триггера 3; с входом второго элемента И вЂ” ИЛИ вЂ” НЕ 13, выход которого соединен с Й-входом третьего триттера 3; с третьим входом шестого элемента И вЂ” НЕ ll, выход которого соединен с

R-входом четвертого трипера 4; и вторым входом пятого элемента И вЂ” НЕ 10, выход которого соединен с R-входом второго триггера 2.

Выход ннвертора 5 соединен с третьим входом второго элемента И вЂ” НЕ 7, выхбд которого соединен с R-входом первого триггера 1, со входами первого элемента И вЂ” ИЛИ вЂ” НЕ 12 и второго элемента И вЂ” ИЛИ вЂ” НЕ 13, с входами вторым третьего 8 и третьи четвертого 9 элементов И вЂ” НЕ 13, с входами вторым третьего 8 и третьим четвертого 9 элементов И вЂ” НЕ, выходы которых соединены с S-входами соответственно четвертого 4 и второго 2 триггеров.

Прямой вход первого триттера 1 соединен с первыми входами третьего 8 и четвертого

9 элементов И вЂ” НЕ, инверсный выход 1тервого триггера l соединен с первыми входами пятого

46942

10 и шестого 11 элементов И НЕ, прямой выход третьего триггера 3 соединен с вторыми .входами четвертого 9 и шестого ll элементов

И вЂ” ЙЕ, инверсный выход третьего триггера 3

5 соединен с первыми входами первого 6 и второго 7 элементов И вЂ” НЕ, прямой выход второго триггера 2 соединен с входами первого элемента И вЂ” ИЛИ вЂ” НЕ 12 и второго элемента

И вЂ” ИЛИ вЂ” НЕ 13, инверсный выход второго триггера 2 соединен со входами первого элемента И вЂ” ИЛИ вЂ” НЕ 12 и второго элемента

И вЂ” ИЛИ вЂ” НЕ 13, прямой выход четвертого триггера 4 соединен со вторым входом второго элемента И вЂ” НЕ 7, с входами первого 12 и

15 второго 13 элементов И вЂ” ИЛИ вЂ” НЕ инверсный

l выход четвертого триггера 4 соединен с вторым входом первого элемента И вЂ” НЕ 6, со входами первого 12 и второго 13 элементов И-ИЛИ вЂ” НЕ.

Устройство работает следующим образом.

Пусть первоначально все RS-триггеры находятся в нулевом состоянии и на входной шине 14 делителя частоты входной сигнал

Х=О.

Учитывая, что

81 У4 3 X

R1 У4 УЗ

S3 = У4 У2 Х + У4 У2 Х

НЗ = У4 У2 Х + У4 У2 Х

8,=У Х

В2 =У1 Х

R4 =УзУ1 Х

84 УЗУ1Х где S;, R1 — логические переменные, описывающие сигналы на входах i-ого триггера;

У; — логическая переменная, описывающая сигнап на выходе i-oro триггера;

Х вЂ” логическая переменная, описывающая входной сигнал, Получаем 81 = R1 = О, 82 = О, R3 1, 83 "2 = 84 п4

В соответствии с принципом работы RS-триггера see выходные сигналы не изменят своих уровней, т.е.

У! = У2 Уз = У4 О

С приходом Х = 1 на входах RS-триггеров устанавливаются сигналы S1 1, R1 = О, 8, = Вз = О, 8, = О, Я - 1 8 - .В = О и RS-триггер 1 изменяет свое состояние, т.е, У1 =l,а У2 Уз = У4 = О. Изменение состояния RS-триггера 1 приводит при неизменном

Х=l к изменению сигнала на R-входе RS-триггера 2 (R2 1), которое не изменит состояние триггеров. Дальнейшее изменение состояний триггеров при изменении входных сигналов отражено в таблице переключений триггеров.

746942

Х $ R 8з Rç 8з йз $а Я4 У4 Уг Уз Уз

1 О О О О О О О

О О

0 О

1 1 О О 0 О 1 О О О О О 1

1 1

О О

О О О О О

О О

О 1

О О

О О О 1 О О О

О О . О 1 О О О

0 1 О О О О О

О О 1

О 1 О 1

О О

1 1

О 1

1 О

О О О О О О

1 1

О 1

0 О

О О О 1 О 1 О . 1 1 1

О О О 1. О 1 0 1

О О

1 О О О О 1

1 О g О

1 О О 0

1 О О О О 1

О О

1 0 О 1 О О О 1 1

1 О О О О О О 1 1

О О

1 О О . О О 1

-О О

1 О

1 0

О О

О О 1 О О

О О 1 1 О О О О О

О О 0 1 О О О О О

О О О О 1 О 1

1 О

О О О О 1 О 1

1 0

0 0 1 О О О О

О О

О О прямой выход — с первыми. входами элементов

И вЂ” ИЛИ вЂ” НЕ, а инверсный выход — со вторыми их входами, S u R входы третьего асинхронного RS-триггера подключены к выходам соответственно первого и второго элементов

И вЂ” ИЛИ вЂ” НЕ, прямой выход — ко вторым входам четвертого и шестого элементов И вЂ” НЕ, а инверсный выход — к первым входам первого и второго элементов И вЂ” HE, $ и R входы

I четвертого асинхронного RS-триггера соединены ° с выходами соответственно четвертого и шестого элементов И вЂ” НЕ„прямой выход — с третьими входами элементов И-ИЛИ вЂ” НЕ и со вторым ! входом второго элемента И вЂ” НЕ, а инверсный выход — с четвертыми входами элементов

Формула изобретения

Делитель частоты импульсов, содержаший асинхронные RS-триггеры инвертор, элементы .

И вЂ” НЕ и элементы И вЂ” ИЛИ-НЕ; о т л и ч аю ш и и с я тем, что, с целью, повышения точ- ности деления, $ и R входы первого асинхронного RS-триггера подключены к выходам соответственно первого и второго элементов И вЂ” НЕ, прямой выход — к первым входам третьего и четвертого элементов И-НЕ, и инверсный выход — к первым входам пятого и шестого элементов И-HE, S u R входы второго асинхронного RS-триггера соединены с выходами соответственно третьего и пятого элементов И вЂ” НE, 1 О

1 О

1 О

О О

О О

О О

О О

О О

О О

1 О

1 О

1 О ». 44 ч

1. Авторское свидетельство СССР И 4253586, кл. Н 03 К 23/00, 1972.

2. Авторское свидетельство СССР Р 506130, кл. Н 03 К 23/00, 1974 .(прототип).

Составитель В. Глатман

Техред М; Петко Корректор В. Синипкая

Редактор Л. Ушакова

Заказ 3975/53 Тираж 995 Подписное

ЦЯИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", z. Ужгород, ул. Проектная, 4

/ ф, 7. 746942, И вЂ ИЛИ вЂ и со вторым входом первого элемента И вЂ” НЕ, фи этом" тфетйй входй первогои шестого элементов И вЂ” НЕ, второй вход пятого элемента И вЂ” НЕ и пятые входы элементов И-ИЛИ—

-НЕ подключены к входной шине непосредственно, 5 а второй вход третьего элемента И-НЕ,третьи входы второго и четвертого элементов И-НЕ и шестые входы элементов И-ИЛИ-НŠ— через инвертор.

Источники информапии, принятые во внимание при экспертизе