Делитель частоты следования импульсов на 5,5

Иллюстрации

Показать всеРеферат

п®тен:,,ОПИС Й

Союз Советски к

Соцмалистическик

Реснублик

746945

ИЗОБРЕТЕН

К АВТОРСКОМУ СВИДЕТЕЛЬ (6l ) gloïîëíèòåëüíîå к авт. свил-ву (22) Заявлено 27,03.78 (21) 2594753/

1jM. Кл.

Н 03 К 23/02 с присоелипемием заявки J%

Гаеударстввнивй камитвт

СССР аю делам изабретений и аткрытий (23) Приоритет

Опубликовано 07 07 80. 5нэллет

3) УДК

621.374.22 (088.8) Дата опубликования описания (72) Авторы изобретения

В. А. Грехнев и В. Н. Гиленок (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ НА 5,5

Изобретение относится к автоматике и вычислительной технике, может быть использовано в устройствах, где необходимо деление последовательности импульсов на дробное число 5,5.

Известны делители частоты следования им5 пульсов, содержащие счетные разряды, состоящие из триггеров памяти и коммутационных триггеров, причем нулевые выходы первых коммутационных триггеров данного разряда соединены с обоими входами вторых коммутаl0 ционных триггеров следунипего старшего разряда t11.

Недостатком описанного устройства является невозможность получения дробного коэффициента деления, Наиболее близким но технической сущности к изобретению является делитель частоты следования импульсов, содержащий четыре разряда, Первые трн из которых состоят из триттера памяти и двух коммутационных триггеров, а четвертый — из триттера памяти, коммутационного триггера и элемента И вЂ” НЕ, а в первых трех разрядах единичный выход триггера памяти соединен с единичным входом второ2 го коммутационного триггера, нулевой выход которого соединен с единичным входом триггера памяти, а единичный выход — с нулевым входом первого коммутационного триггера; единичный выход первого коммутационного триггера соединен с нулевыми входами триггера памяти и второго коммутационного триггера; нулевой выход первого коммутационного триггера первого разряда соединен с обоими входами второго коммутационного триггера второго разряда и со входом первого дополнительного элемента И вЂ” НЕ; нулевой выход первого коммутационного триггера второго разряда соединен с нулевым входом второго коммутационного триггера третьего разряда; нулевой выход первого коммутационного триггера третьего разряда соединен со входом элемента И вЂ” НЕ четвертого разряда, выход которого соединен со входом трг:гера памяти и со входом второго дополнительного элемента И-НЕ; единичные выходы триггеров памяти третьего и четвертого разрядов соединейы со входами первого дополнительного элемента И вЂ” НЕ, выход которого соеди46945 ф

50

3 7 нен со входом второго дополнительного элемента И вЂ” НЕ и с единичным входом первого коммутационного триггера первого разряда; единичный выход коммутационно? о триггера четвертого разряда соединен с нулевым входом триггера памяти этого разряда и с едиййчным входом первого коммутационного триггера первого разряда (21.

--:-"--; .Недостатком данного устройства является низкая надежность, Цель изобретения — повышение надежности устройства, Эта цель достигается тем, что в делителе частоты следования импульсов иа 5,5,состоящем из четырех разрядов, в первых трех из которых, содержащих триггер памяти и два коммутационных триггера, единичный выход триггера памяти соединен с единичным входом второго коммутационного триггера, нулевой выход которого соединен с единичным входом триггера памяти, а единичный выход—

" с йулевьъ входом" первого коммутационного триггерЭ, единичный выход которого соединен с нулевыми входами триггера памяти и второго коммутационного триггера, в четвертом — триггер памяти, коммутационный триггер и элемент И-НЕ, и двух дополнительных элементов И вЂ” НБ, вход первого из которых соедийаи со входами второго коммутационного триггера второго разряда и с ну- левым выходом первого коммутационного триггера первого разряда; нулевой выход первого коммутационного триггера второго разря" да соединен с нулевым входом второго кома мутацйонйого триггера третьего разряда; нулевой выход первого коммутационного триггера третьего разряда соединен со входом элемента

И вЂ” НЕ четвертого разряда, выход которого соединен со входом триггера памяти этого разряда и со входом нтброггб дополйительного элемента И вЂ” НЕ; единичные выходы триггеров памяти третьего и четвертого разрядов соединены со входами первого дополнительного эле. мента И вЂ” НЕ, выход которого соединен со входом второго дополнительного элемента

И вЂ” НЕ и с единичным входом первого коммутационного триггера первого разряда; единичный выход коммутационного триггера чет вертого разрядаi сбефФен с нулевым-входом триггера памяти этого разряда и с единичным входом первог О коммутационного триггера первого разряда; нулевой выход первого коммутационного триггера второго разряда соединен с единичным входом первого коммутационного триггера третьего разряда и со входом элемента И вЂ” НЕ четвертого разряда, : "выход которого соединен с единичным входом коммутационного триггера этого разряда; единичный выход этого триггера соединен с ну1

ЗО

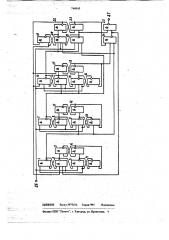

55 левыми входами триггер» памяти и первого коммутационного триггера третьего разряда; нулевые выходы первых коммутационных триггеров первого и третьего разрядов соединены с единичными входами коммутационного триггера четвертого разряда, а нулевой выход триггера памяти четвертого разряда соединен с нулевым входом коммутационного грщтера этого разряда, На чертеже изображена структурная электрическая схема делителя частоты следования импульсов на 5,5.

Схема содержит элементы И вЂ” НЕ 1 — 4, попарно образующие первый H второй коммутационные триттеры первого разряда, элементы

И вЂ” НЕ 5-6, попарно образующие триггер памяти этого разряда, элементы И вЂ” НЕ 7 — 10, образующие аналогично коммутационные триггеры, элементы И вЂ” НЕ 11, 12, образующие триггер памяти второго разряда, элементы

И-НЕ 13-18, образующие триггеры третьего разряда, элементы И вЂ” НЕ 19, 20, образующие коммутационный триггер четвертого разряда, элемент И вЂ” НЕ 21 этого разряда, элементы И вЂ” НЕ 22, 23,образующие трщтер памяти четвертого разряда, элемент И вЂ” НЕ 24 первый дополнительный элемент И вЂ” НЕ 25 второй дополнительный, шину 26 тактирующего сигнала, выходную шину 27. г

Устройство работает следующим образом.

В исходном состоянии триггеры памяти первых двух разрядов находятся в единичном состоянии, триггеры памяти третьего и четвертого разрядов — в нулевом состоянии.

Под действием тактирующего сигнала в делителе происходит обычный пересчет поступающих импульсов в двоичном коде. При этом осуществляется следующая последовательность смены состояний триггеров памяти делителя:

0, 0011

1 0100

2 0101

3 0110

4 011?

5 1000

6 1001

7 1010

8 1011

9 1100

10 1101

11 0011

Видно, что с приходом пятого по счету тактирующего сигнала на выходе элемента 21 появляется сигнал, равный логическому нулю, . который устанавливает триггер памяти четвертого разряда в единичное состояние и который через шину 26 поступает на выходную шину устройства, Далее происходит обычный пересчет поступающих импульсов, и с

5 74694 приходом десятого импульса в делителе устанавливается код 1101. После окончания действия десятого импульса на выходе элемента

1 появляется сигнал, равный логической единице. При этом элемент открывается, и на его выходе появляется сигнал, равный логическому нулю, который через элемент 25 поступает на выходную шину 27. Одновременно сигнал, равный логическому нулю, с выхода элемента 24 поступает на вход элемента

И вЂ” НЕ 2.

С приходом одиннадцатого по счету тактирующего импульса открываются элементы 9 и 20. На выходе этих элементов появляются сигналы, равные логическому нулю, которые устанавливают триггер памяти второго разряда в единичное состояние, а триггеры памяти третьего и четвертого разрядов — в нулевое, элемент 24 закрывается, и прекращается формирование выходного сигнала. Триггер памя- що ти первого разряда свое состояние не изменяет, поскольку элемент 2 остается закрытым сначала сигналом, равным логическому нулю, с выхода элемента 24, а затем сигналом с выхода элемента 20.

После окончания действия тактирующего сигнала устройство возвращается в исходное состояние 0011.

Таким образом, на 11 входных импульсов делитель частоты следования импульсов на

5,5 выдает два выходных,т.е, происходит деление частоты на 5,5, причем выходные сигналы формируются через равные интер, валы времени.

В данном устройстве за счет новых связей сокращено количество элементов И вЂ” НЕ, что позволило повысить надежность работы делителя частоты следования импульсов на

5,5. второго дополнительного элемента И вЂ” НЕ и с единичным входом первого коммутационного триггера первого разряда, единичный выход коммутационного триггера четвертого разряда соединен с нулевым входом триггера памяти этого разряда и с единичным входом первого коммутационного триггера первого разряда, о т л и ч а ю ш и и с я тем, что, с целью повышения надежйостй работы устройства, нулевой выход первого коммутационного триггера второго разряда соединен с единичным входом первого коммутационного триггера третьего разряда н со входом элемента И вЂ” НЕ четвертого разряда, выход которого соединен с единичным входом коммутационного триггера этого разряда, единичный выход этого триггера соединен с. нулевыми входами триггера памяти и первого коммутационного триггера третьего разряда, нулевые выходы первых коммутационных триггеров первого и третьего разрядов соединены с единичными входами коммутационного триггера четвертого разряда, а нулевой выход триггера памяти четвертого разряда соединен с нулевым входом коммутационного триггера этого разряда.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Р 444330, кл. Н 03 К 23/02, 18.03.71.

2. Авторское свидетельство СССР по заявке

Р 2471724/18-21, кл. Н 03 К 23/02 (прототип).

Формула изобретения

Делитель частоты следования импульсов на

5,5, состоящий из четырех разрядов, s пер-, вых трех из которых, содержащих трипер памяти и два коммутационных триггера, единичный выход триггера памяти соединен с еди. ничным входом второго коммутационного триттера, нулевой выход которого соединен с единичным входом триггера памяти, а единичный выход — с нулевым входом первого коммутационного триггера, единичный выход

5 6 которого соединен с нулевыми входами триггера памяти и второго коммутационного триг гера, в четвертом — триггер памяти, коммутационный триггер и элемент И вЂ” НЕ, и двух дополнительных элементов И вЂ” НЕ, вход первого из которых соединен со входами второго коммутационного триггера второго разряда и с нулевым выходом первого коммутационного триггера первого разряда, нулевой выход первого коммутационного триггера второго разряда соединен с нулевым входом второго коммутационного триггера третьего разряда, нулевой выход первого коммутационного триггера третьего разряда соединен со входом элемента И вЂ” НЕ четвертого, разряда, выход которого соединен со входом триггера памяти этого разряда и со входом второго дополнительного элемента И вЂ” НЕ, единичные выходы триггеров па-. мяти третьего и четвертого разрядов соединены со входами первого дополнительного элемента

И вЂ” НЕ, выход которого соединен со входом