Устройство для оценки достоверности приема дискретных сигналов

Иллюстрации

Показать всеРеферат

пвТентно"твхи„

" Фнал б блиотега ),1 G ô, Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свид-ву— (22) ЗаЯвлено 03.05.78(21) 2610636/18-09 (5l )M. Кл. с присоединением заявки нв

Н 04 В 3/46

Гасударственный крмнтет

СССР (23.) ПриоритетОпубликовано 07.07.80. Бюллетень J% 25

1 пс делам нзебрвтений и аткрмтнк (53) УДК 621.395. . 664 (088. 8) Дата опубликования описания 07.07,80 (72) Авторы изобретения

Ю. Я. Личицов, В. А. Бортунов и В. Г. Трофименко (71) Заявитель (54) УСТРОЙСТВО ДЛД ОБЕНКИ ДОСТОВЕРНОСТИ ПРИЕМА

ДИС КРЕТН Ы Х С И ГН АЛОВ

Изобретение относится к электросвязи и может использоваться цля оценки качест» ва канала по информации сигналам.

Известно устройство для оценки достоверности приема дискретных сигналов, содержащее блок автоматической регулировки усиления и поспедовательно со- . единенные счетчик ошибок, мультиплексор, обратный функциональный преобразователь, !

О демультиплексор, первый блок памяти и сумматор, второй вход которого через второй блок памяти соединен с вторым выходом демультиплексора, а также блок инцикации, блок сравнения и блок управления, соответствующие выходы которого подключены к управляющим вхоцам мультиплексора, демультиплексора, первого и второго блоков памяти и первого и второго элементов И, причем на первый вход, блока управления подан сигнал тактовой частоты, а на его второй вход, объединенный с ffllp&BIIBIQIIIHM входом счетчика ошибок, поцан сигнал пуска (Ц, 2

Однако такое устройство отличается сложностью, возрастающей с увеличением степени полинома, аппроксимирующего зависимость аргумента сложной функции от соотношения сигнал/шум.

Цель, изобретения-упрощение устройства путем исключения блоков формирования аппроксимирующего полинома без сни- жения точности оценки.

Это достигается тем, что в извес ное устройство для оценки достоверности приема дискретных сигналов введены формирователь весового коэффициента, блок вычитания, формирователь порогов дискриминации сигналов, переключатель и дополнительный сумматор, при этом выход блока автоматической регулировки усиления через последовательно соединенн ьте формирователь весового коэффициента, блок вычитания, второй вход которого соединен с выходом формирователя порогов дискриминации сигналов, второй элемент

И, переключатель и дополнительный сумматор, подключен к второму входу мульти»

3 . 7469 плексора, выход которого подключен к первому входу блока индикации, второй вход которого соединен с третьим входом блока управления и выходом блока сравнения, первый, второй и третий входы которого соединены соот5 . ветственно с выходом обратного функционального преобразователя, выходом сумма.тора и управляющим входом первого эле мента И, выхоп которого подключен к второму входу дополнительного сумматора, третий. вход которого объединен .: с вторым входом блока управления, первый вход которого объединен с тактовыми вхо дами формирователя порогов дискриминации сигналов, первого элемента И и переключателя, выход которого подключен к сигнальному входу счетчика ошибок.

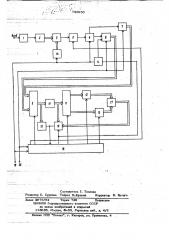

На чертеже, приведена структурйая алектрическая схема предлагаемого устройства, Устройство для оценки достоверности приема дискретных сигналов содержит блок 1 автоматической регулировки усиления (АРУ), формирователь 2 весового 25 коэффициента, блок 3 вычитания, первый и второй элементы И 4 и 5, пере- ключатель 6, счетчик 7 ошибок, сумматор

8, мультиплексор 9, обратный .функцис нальный преобразователь 10, демульти- 30 плексор 11, первый и второй блоки 12 и 13 памяти, формирователь 14 порогов дискриминации сигналов, блок 15 индикации, блок 16 сравнения, сумматор 17, блок 18 управления, иа первый вход 19 З5 которого подан сигнал тактовой частоты, а на его второй вход 20, объединенный с управляющим входом счетчика 7, подан сигнал пуска. Вход блока 1 АРУ являет» ся входом устройства. 40

Устройство работает следующим образом.

Сигналом Пуск" счетчик 7 ошибок, сумматор 8 и блок 18 управления, устанавливаются в исходное состояние. На-, чиная с этого момента, блок 18 управления разрешает прохождение сигналов; через элемент И 5. Входной сигнал поступает на блок 1 АРУ, который стандар- 50 тизует его по уровню. По этому стандартизированному сигналу формирователь 2, используя тактовую частоту, вырабатывает на длине каждой посылки сигнал, величина которого пропорциональна либо

S5 площади посылки при интегральном приеме

P либо амплитуде сигнала при приеме методом короткого контакта. На выходе формирователя 2 имеется положительный curk

50 4 нал. Таким образом, сформированный си нал, пропорциональный весовому коэффициенту посылки, сравнивается в блоке 3 вычитания с двумя сигналами, пропорциональными двум порогам дискриминации сигнала, которые хранятся в формировате ле 14. При атом, .если первый порог диспискриминации принимается равным некоторой величине д, то второй порог дискриминации принимается .равным <У (2-д

Если какой либо порог дискриминации превышает величину весового коэффи- циента посылки, то блок 3 вычитания фоформирует сигнал ошибки, который через элемент И 5 и переключатель 6 поступает либо на счетный вход счетчика 7, либо на первый вход сумматора 8. Счет ошибок проводится на всем объеме выборки, задаваемом блоком 18 управления, Когда объем выборки будет исчерпан, блок 18 управления запрещает прохождение сигналов через элемент И 5. B начальный момент после окончания Счета ошибок на вход обратного функционального преобразователя 10 поступает через мультиплексор 9 значение функции, сформированное на счетчике 7. По этому значению функции на выходе обратного функционального преобразователя 10 формируется значение аргумента, которое запо-! минается в пэрвом блоке 12 памяти.

Импульс, разрешающий запись в блок 12 памяти, формируется блоком 18 управления. После этого мультиплексор 9 по сигналу с блока 18 управления переключает ся в пругое состояние, в котором на ехоп обратного функционального преобразователя 10 коммутируется сигнал, хранимый в сумматоре 8. По атому сигналу обратный функциональный преобразователь 10 формирует второе значение аргумента, которое записывается по разрешающему сигналу с блока 18 управления на второй блок

13 памяти. Сигналы„хранимые а блоках

12 и 13 памяти, суммируются в сумматоре 17, после чего сумма поступает на блок 16 сравнения.

После этого по сигналу с блока 18 уп» управления разрешается прохождение импульсов через элемент И 4 на второй вход сумматора 8, которые последовательно уменьшают значение числа, хранимс го в нем. В соответствии: с этим изменяется значение аргумента на выходе об ратного функционального преобразователя

10. Этот процесс продолжается до тех пор, пока не сравняется значение аргументов На выходе сумматора 17 и обрат

5 7469 ! ного функционального преобразователя 10.

При сравнении значений аргументов на вы.ходе блока 16 сравнения появляется сигнал, который разрешает запись значения функции на блок 15 индикации, и по5 ступая на блок 18 управления, устанавливает устройство в исходное состояние.

Зафиксированное на блоке l 5 индикации число и является оценкой достоверности приема дискретных сигналов, характери- 1О зуемой частотностью появления ошибок.

Предлагаемое устройство позволяет значительно сократить габариты, повысить надежность и увеличить степень оценки достоверности приема дискретных сигналов по сравнению с известным.

Формула изобретения гю

Устройство для оценки достоверности приема дискретных сигналов, содержащее блок автоматической регулировки усиления и последовательно соединенные счетчик ошибок, мультиплексор, обратный функ-2s циональный преобразователь, демультиплексор, первый блок памяти и сумматор, второй вход которого через второй блок памяти соединен с вторым выходом демультиплексора, а также блок индикации, блок зо, сравнения и блок управления, соответствующие выходы которого подключены к управляющим входам мультиплексора, демультиплексора, первого и второго бло«ов памяти и первого и второго элемен- у ,тов И, причем на первый вход блока управления подан сигнал тактовой частоты, а на его второй вход, объединенный с управляющим входом счетчика ошибок, подан сигналпуска, отличающееся щ

50 6 ! тем, что, с целью упрощения устройства ,рутем исключения блоков формирования

:аппроксимирующего полинома без снижения точности оценки, введены формирова тель весового коэффициента, блок вычита ния, формирователь порогов дискриминации сигйалов, переключатель и дополнительный сумматор, при этом выход блока ав томатической регулировки усиления. через последовательно „соединенные формирователь весового коэффициента, блок вычитания, второй вход которого соединен с выходом формирователя порогов дискриминации сигналов, второй элемент И, переключатель и дополнительный сумматор подключен к второму входу мультиплексора, выход которого подключен к первому входу блока индикации, второй вхоц которого соединен с третьим входом блока управления и выходом блока сравнения, первый; второй и третий входы которого соединены соответственно с выходом обратного функционального преобразователя, выходом сумматора и управляющим входом первого элемента И, выход. которого подключен к второму входу дополнительного сумматора, третий вход которого объединен с вторым входом блока управ ления, первый вход которого объединен с тактовыми входами формирователя порогов дискриминации сигналов, первого элемента И и переключателя, выход котс рого подключен к сигнальному входу счетчика ошибок.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке №2426910/18-09, кл. Н 04 В 3/46, 07.12.76.

746950

Составитель Г. Теплова

Редактор С. Суркова Техред М.Кузьма Корректор B. сутяга

Заказ 3976/54 Тираж 729 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент, г. Ужгород, ул. Проектная, 4