Устройство для цифрового анализа сигналов

Иллюстрации

Показать всеРеферат

<11748267

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДН ЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву (22) Заявлено 300178 (21) 2573317/18-21 с присоединением заявки № (51)М. Кл.

G 01 R 23/00

Государственный комитет

СССР ио делам изобретений и открытий (23) Приоритет

Опубликовано 1507,80. Бюллетень ¹ 26 (53) УДК 621. 317. .757(088.8) Дата опубликования описания 150780 (72) Авторы изобретения

В.И.шульгин, Л.A.Êðàñíoâ и A.A.×óìà÷åíêî

Харьковский авиационный институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЦИФРОВОГО АНАЛИЗА СИГНАЛОВ

Изобретение относится к радиоиэмерительной технике. Устройство может быть использовано в системах траекторных измерений для определения скорости и ускорения объектов.

Известны устройства для цифровой обработки сигналов, содержащие квадратурные каналы преобразования сигнала в цифровую форму, генератор линейно-модулированных сигналов„ дискриминатор и решающий блок (11 .

Однако точность анализа их недостаточна.

Известны также устройства, содержащие формирователь чисел, квадратор, сумматор, делитель, умножитель, счетчик и блок регистрации (2).

Эти устройства не обеспечивают совместного измерения частоты и производной частоты исследуемого сигнала, что снижает точность обработки.

Цель изобретения — повышение точности измеречий. цель достигается эа счет того, что25 устройство для цифрового анализа сигналов, содержащее последовательно соединенные формирователь нульпересечений, первый умножитель, сумматор и вычислительный блок, а также первый квадратор, подключенный к выходу формирователя нуль-пересечений, вход которого объединен с входом счетчика, при этом первый выход счет-. чика подключен к второму входу первого умножителя, дополнительно содержит блок прореживания нуль-пересечений, подключенный к объединенным входам формирователя и счетчика, второй квадратор, подключенный к второму выходу счетчика, второй умножитель, один вход которого соединен с выходом первого квадратора, а другой — с первым выходом счетчика, блоки возведения в третью и четвертую степени, входы которых соединены с выходом формирователя нуль-пересечений, и четыре сумматора, через которые выходы второго квадратора, второго ум-, ножителя и блоков воздействия в третью и четвертую степени подключены к входам вычислительного блока.

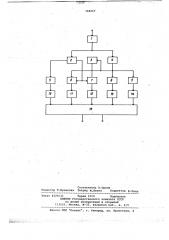

На чертеже представлена структурная схема устройства.

Оно содержит блок 1 прореживания нуль-пересечений, счетчик 2 числа нуль-пересечений, первый квадратор

3, формирователь 4 нуль-пересечений, второй квадратор 5, первый блок 6

748267 умножения, второй блок 7 умножения, блок 8 возведения в третью степень, блок 9 возведения в четвертую степень, сумматоры 10-14, вычислительный блок 15.

Работает устройство следующим образом.

Поток нуль-пересечений исследуемого сигнала поступает на вход блока 1 прореживания нуль-пересечений, который обеспечивает выделение из потока нуль-пересечений некоррелированных, т.е. наиболее информативных, нуль-пересечений. Это достигается делением входного потока нуль-пересечений в и, раз. Полученный прореженный поток нуль-пересечений поступает IS на вход формирователя 4 чисел, соответствующих моментам нуль-пересечений, на выходе которого формируются числа 1к, несущие информацию о моментах выпадения R --x нуль-пересечений. 20

Счетчик 2 числа нуль-пересечений подсчитывает количество импульсов, поступивших на его вход с выхода блока 1 прореживания нуль-пересечений с момента начала измерения, и формирует номер каждого из приходящих нуль-пересечений. В квадраторе 3, на вход. которого поступают числа

1к с выхода формирователя 4 чисел, соответствующих моментам нуль-пересечений, формируются числа к . В

R квадраторе 5, на вход которого поступают числа К с выхода счетчика 2 числа нуль-пересечений, формируются числа R и подаются на вход сумматора 10, который вычисляет сумму

И=1

В блоке 6 умножения вычисляется произведение Rt< чисел R, поступающих с выхода счетчика. 2 числа нуль- рр пересечений, и чисел 1к, поступающих с выхода формирователя 4 чисел, соответствующих моментам нуль-пересечений. Полученное произведение подается на.вход сумматора 11, который формирует на своем выходе сумму

X Pt . В блоке.7 умножения, на входы которого поступают числа К с: выхода счетчика 2 числа нуль-пересечений и числа 1 с выхода квадраток ра 3, вычисляется произведение R4 которое затем подается на вход сумматора 12, формирующего на своем выхбде сумму

Ь1

В блоке b возведения в третью степень и блоке 9 возведения в четвертую степень„ на входы которых йоступают числа 1, с выхода формирователя 4 чисел, соответствующйх моментам нуль-пересечений, формируются числа t и t4 соответственно.

Затем эти числа поступают на входы соответственно сумматора 13 и сумматора 14, которые вычисляют соответст4 вующие суммы „и к=1 к=

С выходов сумматоров 10-14 указанные суммы чисел поступают на соответствующие входы вычислительного блока 15, который производит обработку поступающей информации и формирует на своем выходе оптимальные оценки частоты f и ее производной У в соответствии с критерием максимума логарифма отношения правдоподобия.

Данное устройство обеспечивает точность измерения указанных параметров сигнала, близкую к потенциальной, т.к; реализует оптимальные методы обработки в соответствии с критерием максимума логарифма от- ношения правдоподобия. Оптимальная структура схемы измерителя позволяет осуществить его реализацию с помощью стандартных блоков вычислительной техники в сравнительно малом объеме.

Формула изобретения

Устройство для цифрового анализа сигналов, содержащее последовательно соединенные формирователь нульпересечений, первый умножитель, сумматор и вычислительный блок, а также первый квадратор, подключенный к выходу формирователя нуль-пересечений, вход которого объединен с входом счетчика, при этом первый выход счетчика подключЕн к второму входу первого умножителя, о т л и ч а ю щ е е с я тем, что, с целью повышения точности измерений, оно дополнительно содержит блок прореживания нуль-пересечений, подключенный к объединенным входам формирователя и счетчика, второй квадратор, подключенный к второму выходу счетчика, второй умножитель, один вход которого соединен с выходом первого квадратора, а другой — с первым выходом счетчика, блоки возведения в третью и четвертую степени, входы которых соединены с выходом формирователя нуль-пересечений, и четыре сумматора, через которые подключены выходы второго квадратора, второго умножителя и блоков возведения в третью и четвертую степени к входам вычислительного блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское .свидетельство СССР по заявке Р 2354266/09, кл. G 06 F 15/34, 29.10.76.

2.- Андреева И.С., Снитко Б.Н.

Об измерении частоты по переходам напряжения через нулевой уровень, "Радиотехника", т.29, Р 6, 1974, с,76.-79.

748267

Составитель А.Орлов

Редактор Т.Юрчикова Техред М.Петко . корректор Е.Папп

Заказ 4229/31 Тираж 1019 Подписное

ЦНИИПИ Росударственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4