Интегратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик о >748439 (61) Дополнительное к авт, свид-ву (51)pA. Кл.з (22) 3аявлено 040578 (21) 2612161/18-24 с присоединением заявки ¹ (23) Приоритет ь 06 6 7/18

Государственный комитет

СССР по делам изобретений н открытий

Опубликовано 15.07.80.Бюллетень № 26 (53) YQK681. 335 (088.8) Дата опубликования описания 15.0780 (72) Авторы изобретения

М. А. Радько и Д. В. Морошан (71) За яв ител ь (54) ИНТЕГРАТОР рования от влияния сопротивления открытого NOII-ключа, управляющего процессом интегрирования, а также сравнительно большая погрешность из-за влияния дрейфа нуля операционных усилителей.

Целью изобретения является повышение точности интегрирования.

Поставленная цель достигается тем, что в интегратор, содержащий интегрирующий усилитель, выход которого соединен с инвертирующим входом корректирующего операционного усилителя, масштабный резистор, один вывод которого является входом интегратора, интегрирующий конденсатор, подключенный одной обкладкой к выходу интегрирующего усилителя, запоминающий конденсатор, включенный между шиной нулевого потенциала и неинвертирующим входом интегрирующего усилителя, и два ключа, каждый из которых выполнен на МОП-транзисторе, цепь стокисток МОП-транзистора первого ключа включена параллельно интегрирующему конденсатору, второго — между выходом корректирующего операционного усилителя и неинвертирующим входом интегрирующего усилителя, а зат.воры МОП-транзисторов ключей соеди1

Изобретение относится к области автоматики и электроиэмерительной техники и может быть использовано при построении устройств измерения сигналов низкого уровня в присутствии помех.

Известен интегратор, содержащий операционный усилитель, и интегри.— рующую цепь, состоящую из резистора и конденсатора $1) . 10 .Известный интегратор имеет низкую точность интегрирования, так как его выходной сигнал является функцией не только входного сигнала, но и напряжения дрейфа нуля one- 15 рационного усилителя.

Наиболее близким к предлагаемому устройству по технической сущности является интегратор, содержащий

-интегрирующий и корректирующий опе- 20 рационные усилители, интегрирующую цепь, состоящую иэ резистора и конденсатора, конденсатор запоминания напряжения коррекции дрейфа нуля устройства и MOIL-ключи управления 25 процессом интегрирования, коррекцией дрейфа и разрядом интегрирующего конденсатора (2) . ./

Недостатком этого интегратора яв.ляется наличие погрешности ичтегри748439 иены с входом сброса интегратора, введены дополнительные ключи, выполненные на МОП-транзисторах,дополнительный масштабный резистор и инвертор, причем цепь сток-исток MOILтранзистора первого дополнительного ключа включена между шиной нулевого потенциала и инвертирующим входом интегрирующего усилителя, цепь стокисток МОП-транзистора второго дополнительного ключа подключена между вторыми выводами масштабного резистора и интегрирующего конденсатора, соединенными через цепь сток-исток

МОП-транзисторов соответственно третьего и четвертого дополнительных ключей с инвертирующим входом интегрирующего усилителя и с первым выводом цополнительного масштабного резистора, второй вывод которого подключен к инвертирующему входу интегрирующего усилителя, затворы МОП- 2Q транзисторов второго и третьего дополнительных ключей соединены, со входом управления процессом интегрирования, затвор МОП-транзистора первого дополнительного ключа подключен ко входу сброса интегратора, соеди25 ненному через инвертор с затвором

МОП-транзистора четвертого дополнительного ключа.

Это пбзволяет значительно уменьшить влияние на точность интегрирования сопротивления МОП-ключей, управляющих процессом интегрирования, а также дрейфа нуля корректирующего операционного усилителя.

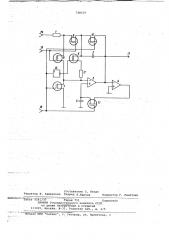

На чертеже показана схема интегратора, на которой обозначены масш-.àáHûé резистор 1., интегрирующий конденсатор 2, интегрирующий 3 и корректирующий 4 операционные усилители, запоминающий конденсатор 5, ключи 4Q

6 — 11, выполненные на MOIL-транзисторах, дополнительный резистор 12, инвертор 13, вход интегратора 14, вход управления процессом интегрирования

15, вход сброса интегратора 16, вы- 45 ход интегратора 17.

Интегратор работает следующим образом.

С поступлением импульса сброса по входу 16 интегратора открываются ключи 10, 11 и 7 и закрывается ключ

9. С помощью ключа 10 осуществляется разряд интегрирующего конденсатора 2, ключом 11 подключается выход корректирующего операционного усилителя к запоминающему конденсатору 5 и к неинвертирующему входу интегрирующего операционного усилителя 3. Ключ 7 замыкает инвертирующий вход интегрирующего операционного усилителя 3 на шину нулевого потен- ц циала, а ключ 9 разрывает цепь отрицательной обратной связи интегратора. Одновременно с разрядом интегрирующего конденсатора начинается процесс коррекции дрейфа нуля операционных усилителей. При этом напряжение на выходе корректирующего операционного усилителя будет равно где Оя„ и д Π— входное напряжение и напряжение дрейфа нуля этого усилителя, коэффициент усиления этого усилителя.

Так как выход корректирующего операционного усилителя соединен с инвертирующим входом интегрирующего операционного усилителя, цепь отрицательной обратной связи последнего разомкнута, и его инвертирующий вход подключен к шине нулевого потенциала, выходное напряжение интегрирующего усилителя можно записать (2)

0 =,U +дц

ВЬ!ХЛ 8Ь|Х Л1кл О Х где д0л — напряжение дрейфа нуля интегрирующего операционного усилителя, кл — его коэффициент усиления.

Решая совместно уравнение (1) и (2), получим

Ди2К -Д „К„К, 8ЫХ l Л+К К

Л

Поскольку к„>p 1 и KzI> 1, 1 + K

usb,x=- — -du .

КЛ Л

После окончания импульса сброса открывается ключ 9, замыкая цепь отрицательной обратной связи интегрирующего операционного ус1ллителя 3 через интегрирующий конденсатор 2.

С поступлением на вход управления процессом интегрирования устройства

15 сигнала, разрешающего интегрирование, замыкаются ключи б и 8. Начинается интегрирование входного напряжения, подаваемого по входу 14.

После окончания процесса интегрирования (при включении ключей б и 8) интегРатор входит в режим хранения проинтегрированного входного сигнала.

Выходное напряжение интегратора будет иметь вид

О и ХРанения (R+R ср х (RtR 4 к

Л8 О + Ля С о где К вЂ” сопротивление .масшта бного ре з йстора, R18 - эквивалентное сопротивление, МОП-транзисторов .

748439

Применение предлагаемого интегратора в измерительных устройствах позволяет значительно повысить их точность. Так, дрейф нуля интегратора по сравнению с прототипом уменьшается в K„ раз, где К, — коэффициент усиления интегрирующего усилителя.

Использование дополнительных клю-. чей и дополнительного резистора в цепи коммутации масштабного резистора уменьшает влияние сопротивления этих ключей на точность интегрирования. Так, если даже сопротивление дополнительного резистора равно нулю, точность интегрирования возрастает в два раза по сравнению с прототипом. При превышении сопротивления дополнительного резистора над сопротивлением открытого ключа в 100 раз, влияние сопротивления открытого ключа на точность интегрирования уменьшается в 100 раэ по сравнению с прототипом.

Формула изобретения 25

Интегратор, содержащий интегрирующий усилитель, выход которого соединен с инвертирующим входом корректирующего операционного уси- 30 лителя, масштабный резистор, один вывод которого является входом интегратора, интегрирующий конденсатор, подключенный одной обкладкой к выходу интегрирующего усилителя, за- 35 поминающий конденсатор, включенный между шиной нулевого потенциала и неинвертирующем входом интегрирующего усилителя, и два ключа, каждый иэ которых выполнен на МОП-транзис- 4р торе, цепь сток-исток МОП-транзистора первого ключа включена параллельно интегрирующему конденсатору, второго — между выходом .корректирующего операционного усилителя и неинвертиру45 ющим входом интегрирующего усилителя, а затворы МОП-транзисторов ключей соединены с входом сброса интегратора, отличающийся тем, что, с целью повышения точности интегрирования, в него введены дополнительные ключи, выполненные на МОПтранзисторах, дополнительный масштабный резистор и инвертор, причем цепь сток-исток МОП-транзистора первого дополнительного ключа включена между шиной нулевого потенциала и инвертирующим входом интегрирующего усилителя, цепь сток-исток МОПтранзистора второго дополнительного ключа подключена между вторыми выводами масштабного резистора и интегрирующего конденсатора, соединенными через цепь сток-исток МОП-транзисторов соответственно третьего и четвертого дбполнительных ключей с инвертирующим входом интегрирующего усилителя и с первым выводом дополнительного масштабного резистора, второй вывод которого подключен к инвертирующему входу интегрирующего усилителя, затворы МОП-транзисторов второго и третьего дополнительных ключей соединены со входом управления процессом интегрирования, затвор МОП-транзистора первого дополнительного ключа подключен ко входу сброса интегратора, соединенному через инвертор с затвором МОП-транзистора четвертого дополнительного ключа.

Источники информации, принятые во внимание при экспертизе

1. Ж. Марше. Операционные усилители и их применение, "Энергия", .М., 1974, с. 70..

2. A. И. Наконечный. Интегра= тор на микросхеме с автоматической компенсацией дрейфа нуля. Контрольно-измерительная техника. Республиканский межведомственный научнотехнический сборник, Киев, 1975, вып. 18 (прототип) .

748439

Составитель С. Белан

Редактор Н. Каменская Техред Я,Бирчак Корректор Г. Решетник

Заказ 4241/37 Тираж 751 Подписное

ЦИНИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 !. н Ммгм « » а>илиал ППП Патент", r Ужгород, ул. Проектная, 4