Устройство для моделирования линейных систем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕПЬСТВУ (11748448

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. сеид-ву(22) Заявлено 10О478 (21)2601769/18-24 с присоединением заявки М

{23) Приоритет

Опубликовано 15.0780, Бюллетень йо 26

Дата опубликования описания 150".80 (51)М. Кл.

G 06 G 7/48

Государственный комитет

СССР по делам изобретений и открытий (5Ç) УДК 681.ЗЗЗ (088. 8), (72) Авторы изобретения

Л.И.Гутенмахер и Ю.A.Тимошенко (71) Заявитель

Одесский ордена Трудового Красного Знамени политехнический институт (54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЛИНЕЙНЫХ

CHCTEN

Изобретение относится к моделиру ющим устройствам линейных динамических систем и объектов и может быть использовано в тех случаях, когда известна экспериментальная переход- 5 ная или импульсная переходная функция исследуемого объекта.

Известно модулирующее устройство для воспроизведения динамических характеристик линейных объектов и сис- 10 тем, содержащее элементы задержки, звенья, моделирующие передаточную функцию запаздывания f,l).

Недостаток устройства — низкая точность моделирования. 15

Наиболее близким техническим решением к изобретению является устройство для моделирования линейных систем,содержащее блоки памяти, блоки резисторов, сумматоры, ключи, коль- 20 цевой распрелелитель (2).

Недостатком устройства является низкая точность моделирования.

Цель изобретения — повыаение точности моделирования. 25

Цель достигается тем, что в устройстве для моделирования линейиых систем,содержащем генератор тактовых импульсов, блок памяти, выполненный s виде ячеек памяти, причем выходы не- 30

2 четных ячеек памяти подключечы к входам R-сетки, первый выход которой через первый сумматор соединен с первым входом второго сумматора, ячейки памяти соединены последовательйо, управляющие входы нечетных ячеек памяти подключены к выходу генератбра тактовых импульсов, выход которого соединен с входом инвертора, выходом подключенного к управляющим входам четных ячеек памяти, второй выход R-сетки соединен с вторым входом второго сумматора.

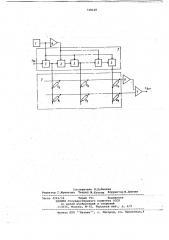

На чертеже показана схема устройства.

Схема содержит генератор 1 тактовых импульсов, блок :памяти 2, состоящий иэ ячеек памятиЗ, ннвертор 4, R-сетку 5, сумматоры 6 и 7.

Величины сопротивлений резисторов

R, R„ R-сетки 5 устанавливаются пропорционально значениям в общем случае смещенной по оси ординат импульсной переходной функции объекта в дискретные равностоящие на величину длительности периода импульсов генератора l.моменты времени. Смещение динамической характеристики по оси ординат обеспечивается с помощью резисторов R R-сетки, причем ве748448 личина смещения может регулироваться в заданных пределах изменением коэффициента передачи сумматора 6. Число разрядов и в блоке памяти 2 и соответственно число вертикальных шин

R-сетки 5 определяются эаданйым уровнем дискретизации временной переменной, так что т=na i! где Т вЂ” длительность импульсно-переходной функции;

4 — период тактовых импульсов генератора 1 °

Устройство работает следующим образом.

При поступлении импульса генератора 1 на управляющие входы нечетных ячеек памяти 3 в них происходит эапоминание входного сигнала, поступа ющего по информационному входу, и его хранение на время, не меньшее вели"чины длительности периода тактовых импульсов генератора 1.

Напряжения с выходов нечетных ячеек блока памяти 2 через соответствующйе резисторы R -сетки 5 поступают на вход сумматора 7.На другой вход сумматора 7 поступает напряжение смещения, образуемое сумматором 6.На выходе сумматора 7 формируется значение выходного сигнала системы на данном такте.

В период паузы генератора 1 тактовых импульсов на управляющие входы четных ячеек памяти 3 поступает импульс с выхода инвертора 4. При этбм в четных ячейках памяти проиСходит запоминание текущего напряже ния, поступающего с выхода нечетной ячейки памяти предыдущего данному разряда на время, большее лйбо равное длительности импульса инвертора.

По приходе следующего импульса генератора в блоке памяти 2 происходит запоминание сигналов, поступающих на информационные входы всех нечетных ячеек намяти 3. Таким образом, последовательно такт за тактом входной сигнал системы перемещается по разрядам блока памяти 2, На выходах R-сетки 5 образуются новые значения соответствующих напряжений, которые в сумматоре 7 образуют очередное значение выходного сигнала. г

В дальнейшем работа устройства происходит аналогично описанному выше, Нетрудно показать, что выходная величина ХЬ „(1) в момент времени

4-.mat равна сумме реакций линейной ста5 ционарной динамической системы от каждого предшествующего импульса входного сигнала

ff1 х6„„(t) =,K h(t 1ьТ) хь ((.д)ЛС. (1)

В пределе выражение (1) представляет собой интеграл суперпозиции, позволяющий определить точное значение

x6„,„„(t):

x(,„„(t)=Jb(t-i)к () ( где h(t-t) — смещенная импульсная переходная фуíKi;èÿ динамичеcKой системы.

При условии знакопостоянства функ— ции Ь(t) схема устройства упрощается, 20 поскольку отпадает необходимость наличия резисторов смещения R в R-сетке 5 и сумматора 6, и повышается точность моделирования.

25 формула изобретения

Устройство для модели рования линейных систем, содержащее генератор такЗО товых импульсов, блок памяти, выпол-, ненныйв виде ячеек памяти, причем вы; ходы нечетных ячеек памяти подключены к входам R-сетки, первый выход которой через первый сумматор соединен с первым входом второго сумматора, о т л и ч а ю щ е е с я тем, что, с целью повышения точности моделирования, ячейки памяти соединены последовательно, управляющие входы нечетных ячееек памяти подключены к выходу генератора тактовых импульсов, выход которого соединен с входом инвертора, выход которого подключен к управляющим входам четных ячеек памяти, второй выход R-сетки соединен с вторым входом второго сумматора.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

9 219915, кл, G G 7/40, 1967.

5р 2 ° Авторское свидетельствб СССР

9 384108, кл, G 06 G 7/48,, 1971.

748448

Составитель И. Дубинина

Редактор Г . Юрчиков а Техред М, Кузьма Корректор М. Демчик

Заказ 4242/38 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная,4