Устройство для контроля постоянной памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<1Ц 748514 (61) Дополнительное к авт. свид-ву (22) Заявлено 05. 06. 78 (21) 2624178/18-24 (51)М. Кл.G 11 С 29/00 с присоединением заявки Hо (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 150780. Бюллетень Мо 26

Дата опубликования описания 17.0780 (53} УДК681. 327 (088. 8) В. П. Андреев, Б. П. Шурчков, А. Н. Пресняков, A. Н. Иванов, E. A. Егоров и В. В. Васин (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ

ПАМЯТИ

Изобретение относится к области запоминаюших устройств.

Известны устройства цля контроля постоянной памяти (1), $2j .

В одном иэ известных устройств контроль постоянных эапоминаюших блоков осуществляется последовательным считыванием некоторого массива информации с образованием контрольного кода этого массива и последующим сравнением этого кода с эталонным значением (1) .

Недостатком такого устройства является невысокая эффективность контроля. 15

Из известных устройств наиболее близким техническим решением к данному изобретению является устройство для контроля постоянной памяти, содержашее блок эталонной памяти, вы- 20 ход которого подключен к одному иэ входов блока управления, другой вход которого соединен со входом устройства, а первый выход — со счетным входом первого счетчика (2) .

Недостатком этого устройства является то, что контроль постоянного запоминающего блока выполняется только при последов< тельном считывании инфор° ъл различных адресных переходах не про- веряется, в результате чего снижается достоверность контроля и надежность устройства.

Целью изобретения является повышение надежности устройства,- контроля и расширение области его применения.

Поставленная цель достигается тем, что устройство содержит второй счетчик и коммутатор, причем счетный вход второго счетчика подключен ко второму выходу блока управления, третий выход которого подключен к одному из входов коммутатора, выход которого соединен с выходом устройства, одни иэ выходов второго счетчика подключены к разрядным входам первого счетчика, другие выходы второго c÷åò÷èêà и выходы первого счетчика соединены соответственно со входом блока эталонной памяти и другими входами коммутатора.

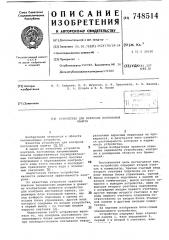

На чертеже изображена блок-схема описываемого устройства.

Устройство содержит блок эталонной памяти 1, блок управления 2, первый 3 и второй 4 счетчики, ком748514

Формула изобретения

К выходам и входам устройства подключается блок контролируемой постоянной памяти 6.

Выход блока эталонной памяти 1 подключен к одному из входов блока управления 2, другой вход которого соединен .со входом устройства, а первы@ выход — со счетным входом первого счетчика 4. Счетный вход второго счетчика 3 подключен ко второму выходу блока управления 2, третий выход которого соединен с одним из входов коммутатора 5.

Одни из выходов счетчика 4 подключены к разрядным входам счетчика

3, другие выходы счетчика 4 и выход счетчика 3 соединены соответст- 15 венно со входом блока 1 и другими входами коммутатора 5, выход которого является выходом устройства.

Устройство работает следующим образом. 20

По командам с блока управления 2 начальный адрес счетчика 3 устанавливается в соответствии с состоянием и младших разрядов счетчика 4 и входы счетчика 3 подключаются через коммутатор 5 к контролируемой постоянной памяти 6. Запускается счетчик 3. Происходит перебор адресов с обращением в реальном масштабе времени к контролируемой постоянной памяти 6. После этого блок управления 2 выдает команду на прохождение через коммутатор

5 и старших разрядов счетчика 4 (без нарушения темпа обращений) и на сравнение информации блока контролируемой постоянной памяти 6 с информацией бло- ка эталонной памяти 1 по адресу проверки, определяемому состоянием п старших разрядов счетчика 4. При совпадении информации, полученной с блока контролируемой постоянной памяти 4()

6 по данному адресу с эталонной, блок управления 2 выдает сигнал, изменяющий состояние счетчика 4 на "+1".

Счетчик 3 устанавливается в соответствии с новым состоянием и младших разрядов счетчика 4, и цикл проверки повторяется. При несовпадении проверка прекращается или фиксируется результат сбоя.

Таким образом, описанное устройство позволяет обеспечить контроль постоянных запоминающих блоков при всех возможных адресных переходах на реальной частоте обращений, что расширяет область применения устройства, повышает достоверность контроля и надежность работы устройства.

Устройство для контроля постоянной памяти, содержащее блок эталонной памяти, выход которого подключен к одному из входов блока управления, другой вход которого соединен со входом устройства, а первый выход — со счетным входом первого счетчика, о тл и ч а ю щ е е с я тем, что, с целью .повышения надежности устройства оно содержит второй счетчик и коммутатор, причем счетный вход второго счетчика подключен ко второму выходу блока управления, третий выход которого подключен к одному из входов коммутатора, выход которого соединен с выходом устройства, одни из выходов второго счетчика подключены к разрядным входам первого счетчика, другие выходы второго счетчика и выходы первого счетчика соединены соответственно со входом блока эталонной памяти и другими входами коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 516102; кл. G 11 С 29/00, 1974.

2. Авторское свидетельство СССР ,Э 510753, кл. G 11 С 29/00, 1974 (прототип).

ЦНИИПИ Заказ 4247/40

Тираж 662 Подписное

Филиал ППП Патент, r,Óæãoðoä,ул.Проектная.4