Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ р11 7485 1 5 (61) Дополнительное к авт. свид-ву (22) Заявлено 08. 06. 78 (21) 2631178/18-24 (51)М. Кл. с присоединением заявки Йо

G 11 С 29/00

Государственный комитет,СССР по делам изобретений н открытий (23) Приоритет

Опубликовано 150780. Бюллетень ¹ 26

Дата опубликования описания 170780 (53) УДК 681 327 (088. 8) (72) Автор изобретения

В. Н. Горшков Пушкинское высшее ордена Красной Звезды училище радиоэлектроники противовоздушной обороны (71) Заявитель (54) ЗАПОМИНАПЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к области запоминающих устройств.

Известны запоминающие устройства с самоконтролем.

Одно из известных устройств содер- 5 жит адресный и ассоциативные запоминающие блоки (1) .

Недостатком этого устройства является применение ассоциативных запоминающих блоков для записи данных при отказах ячеек адресного запоминающего блока, что усложняет устройство.

Из известных устройств наиболее близким техническим решением к дан- !5 ному изобретению является запоминающее устройство с самоконтролем, содержащее накопитель, регистры числа, группы элементов ИЛЙ, регистры адреса, счетчик адресов, блок контроля, блок управления и блок местного управления, причем выход накопителя подключен к первым входам первого регистра числа и второго регистра числа и ко входу третьего регистра 25 числа, входы накопителя соединены с выходами элементов ИЛИ, входы элементов ИЛИ первой группы подключены к выходам первого регистра адреса и второго регистра адреса, вход кото- ЗО рого соединен с выходом счетчика адресов, первый выход второго регистра числа и выход первого регистра чис1 ла подключены к одним из входов второй группы элементов ИЛИ, вторые вход и выход второго регистра числа соединены соответственно с выходом блока местного управления и первым входом блока контроля, второй вход которого соединен с выходом третьего регистра числа, один из выходов блока управления подключен к управляющим входам накопителя, первого и второго регистра адреса, счетчика адресов первого, второго и третьего регистров числа, блока контроля и блока местного управления E21 .

В этом устройстве в работоспособ« ные разряды отказавшей ячейки накопителя записывается адрес резервной ячейки.

Недостатком этого устройства является неполное использование работоспособных разрядов в отказавшей ячейке, при записи в нее адреса резервной ячейки, что приводит к сниже-. нию эффективной емкости устройства.

Целью изобретения является увеличение эффективной емкости запоминающего устройства.

74

Поставленная цель достигается тем, что устройство содержит четвертый регистр числа, коммутаторы и счетчик разрядов, причем входы четвертого ре гистра числа подключены соответствен но к выходам накопителя и первого коммутатора, а выходы - к другим входам второй группы элементов ИЛИ и первому входу второго коммутатора, выход которого соединен со вторым входом первого регистра числа, выход ко- торого подключен к первому входу первого коммутатора, вторые и третьи входы первого и второго коммутаторов соединены соответственно с первыми : выходами блока контроля и счетчйка разрядов, вторые выходы которых.подключены соответственно ко входам счет,чика разрядов и блока управления, управляющие входы четвертого регистра числа коммутаторов соединены с другими выходами блока управления.

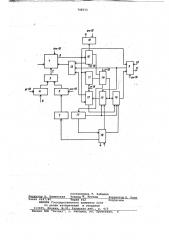

На чертеже изображена блок-схема предложенного устройства.

Устройство содержит накопитель 1, имеющий входы 2, первую группу элементов ИЛИ 3, первый регистр адреса 4, второй регистр адреса 5, входы 6 первого-регистра адреса, счет-.. чик адресов 7. К выходам 8 накопи- „., теля подключены первые входы первого регистра числа 9, второго регистра: числа 10, вход третьего регистра 11 и один иэ входов четвертого 12 регистра числа.

Устройство содержит также вторую группу элементов ИЛИ 13,. блок конт-, роля 14, первый 15 и второй 16 коммутаторы, счетчик разрядов 17, блок, управления 18 и блок местного управ- . ленйя Х9, вход 20 и выход 21 уст- ...— ройства.

Входы 2 накопителя 1 соединены с выходами элементов или 3, вхбдй ко- торых подключены к выходам первого 4 и второго 5 регистров адреса. Вход регистра 5 соединен e -вйходбЯ счетчика адресов 7. Выход регистра числа 9 и первый выход регистра чис" „ ла 10 "подклйчены к одним из входов элементов ИЛИ 13, Йййод котбфИ. под-" ключен к входу накопителя 1. Вторые

) ,вход и выход регистра числа 10 со- единены соответственно с выходом " " блока местного управления 19 и первым входом блока контроля 14, второй вход которого подключен к выходу третьего регистра числа 11. Другой вход четвертого регистра числа 12 подключен к выходу первого коммута- тора 15, а выходы регистра 12 - к

" другим входам элементов ИЛИ 13 и пер-... вому вхоДу второго коммутатора 16;— выход которого соединен со вторым входом первого регистра числа 9, выход которого соединен с первым входом первого коммутатора 15. Вторые ,и третьи входы первого 15 и второго

М коммутаторов соединены соответст8515 ф венно с первыми выходами блока контроля 14 и счетчика разрядов 17. Вто рой выход блока контроля 14 подключен ко входу счетчика разрядов 17,второй выход которого соединен со входом блока управления 18.Один иэ выходов блока управления 18 подключен к управляющим входам накопителя 1, первого

4 и второго 5 регистров адреса, счетчика адресов 7, первого 9, второго

10, третьего 11 и четвертого 12 регистров числа, блока контроля 14 и блока местного управления 19, другие

,,выходы блока управления 18 соединены с управляющими входами коммутаторов

15 и 16.

1$

Устройство работает следующим образом.

В исходном состояиии счетчик разрядов 17 обнулен. Для каждого линейного участка программы -или для массива чисел, которые будут записывать- . ся и считываться последовательно, выделяются резервные ячейки накопителя 1. В счетчик адресов 7 при этом записывается адрес первой резервной

25 ячейки, а на вхОд 6 основного регистра адреса 4 поступает адрес первой ячейки записываемого или считываемого массива чисел..

При записи чйсло через вход 20 поступает в регистр 9, и содержимое регистра адреса 4 через элементы

ИЛИ 3 подается на вход, накопителя 1.

Обратный код из регистра 9 через элементы ИЛИ 13 записывается в ячейку йакопителя 1. Затем содержимое ячей ки считывается на регистр 11. После этого производится запись-считывание прямого кода числа на регистр 10 °

Содержимое регистров 10 и 11 подается на блок контроля 14. В случае, если отказавших- разрядов в ячейке нет, то в регистр 4 на вход 6 подается следующий адрес и аналогично производится запись второго числа. Если же в ячейке есть. отказавшие разряды, то блок контроля 14 и счетчик разрядов

17 выдают на коммутатор сигналы, по которым из регистра 9 в младшие разряды регистра 12 передаются разряды числа, соответствующие отказавшим разрядам ячейки, Затем с блока контроля 14 в счетчик разрядов 17 записывается код, соответствующий количеству отказавших разрядов ячейки. Из блока управления 18 в блок местного управленйя 19 поступает сигнал, йо . которому в маркерный разряд ячейки накопителя через регистр 10 записывается код "1". Аналогично производится запись числа во вторую отказавшую ячейку, только соответствующие раэряды регистра 9 записываются в, следующие младшие незанятые разряды регистра 12. После того, как все разряды регистра 12 будут заполнены, Фчетчик разрядов выдает сигнал заполз.

748515

Запоминающее устройство с самоконтролем, содержащее накопитель, ре гистры числа, группы элементов ИЛИ, регистры адреса, счетчик адресов, Ьлок контроля, блок управления и бЛок

Местного управления, причем выход накопителя подключен к первыМ входам

hepaoro и второго регистров числа и ко входу третьего регистра числа, входы накопителя соединены с выхода- ми элементов ИЛИ, входы элементов

ИЛИ первой группы подключены к выходам первого регистра адреса и второго регистра адреса, вход которого

-соединен с выходом счетчика адресов, первый выход второго регистра числа и выход первого регистра числа подключены к одним из входов второй группы элементов ИЛИ, вторые вход и выход второго регистра числа соединены соответственно с выходом блока местного управления и первым входом блока контроля, второй вход которого соединен с выходом третьего регистра числа, одни из выходов блока управлейия подключены к управляющим входам накопителя, первого и второго регистров адреса, счетчика адресов, первого, второго и третьего регистров числа, блока Контроля и блока местного управления, о т л и ч а ю щ е е с я тем, что, с целью увеличения эффективной емкости устройства, оно содержит четвертый регистр числа, коммутаторы и счетчик разрядов, причем входы четвертого регистра числа подключены соответственно к выходам накопителя и первого коммутатора, а выходы — к другим входам элементов

ИЛИ второй группы и первому входу второго коммутатора, выход которого соединен со вторым входом первогорегистра числа, выход которого подключен к первому входу первого коммутатора, вторые и третьи входы пер- вого и второго коммутатора соединены соответственно с первыми выходами блока контроля и счетчика разрядов, вторые выходы которых подключены соответственно ко входам счетчика разрядов и блока управления, управляющие входы четвертого. регистра числа и коммутаторов соединены с другими

:выходами блока управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 529490, кл. G 11 С 29/00, 1976.

2. Авторское свидетельство СССР Э 519767, кл. G 11 С 29/00, 1976 (прототип). технико-экономические преимущест- 5$ ва изобретения заключаются в значительном сокращении количества резервных ячеек в накопителе при последовательном выборе адресов. Например, если разрядность накопителя равна 32, @ а в выбранном для записи массиве чисел участка памяти отказали по 2 разряда в 16 ячейках, то в известном устройстве потребуется 16 резервных ячеек, в предоженном - всего лйшь оды нения в блок управления 18. Адрес резервной яч; йки из счетчика адреса 7 поступает на регистр адреса 5 и через элементы ИЛИ 3 на вход 2 накопителя

1. Содержимое регистра 12 через элементы ИЛИ 13 записывается в первую резервную ячейку массива чисел. После этого по сигнаЛу из блока управления

18 в счетчике адреса 7 формируется адрес следующей резервной ячейки.

Чтение информации производится следующим образом. В регистр адреса 4 через вход 6 подается адрес первой ячейки считываемого массива чисел, а в счетчик адреса 7 записывается адрес первой резервной ячейки массива чисел.

Счетчик разрядов 17 при этом находится15 в нулевом состоянии. По сигналу из блока управления 18 производится передача содержимого счетчика адреса 7 через регистр адреса 5 и элементы ИЛИ 3 на вход 2 накопителя 1. Производится Щ чтение числа из первой резервной ячейки на регистр 12. Затем из регистра адреса 6 поступает адрес первой ячей- ки считываемого массива чисел и производится чтение на регистры 9 и 10. Ес-)$ ли в маркерном разряде код "0", то, следовательно, в ячейке не было отказавших разрядов и число из регистра 9 поступает на выход 21.

Если же в маркерном разряде код ЭО

"1", то производится запись-чтение обратного кода числа на регистр 11. Содержимое регистров 10 и 11 подается на блок контроля 14. По сигналам из блока контроля 14 и счетчика разрядов 17 через второй коммутатор 16 производится передача младших разрядов регистра 12 в регистр 9. Разряды отказавшей ячейки, таким образом, подменяются разрядами резервной ячейки.

Число иэ регистра 9 поступает на вы- ® ход 21. В счетчик разрядов 17 записывается код, соответствующий количест- ву использованных разрядов регистра

12. Если все разряды регистра 12 будут использованы, на что указывает 45 соответствующее состояние счетчика разрядов 17, то по сигналу из блока управления в счетчике адреса 7 формируется адрес следующей резервной ячей ки. Содержимое резервной ячейки счи- 50 тывается на регистр 12 и аналогично продолжается считывание массива чисел с подменой отказавших разрядов. ячейка, за счет чего значительно увеличивается эффективная емкость предложенного запоминающего устройства.

Формула изобретения

748515

Составитель.T. Зайцева

М, Кузьма Ко ректо Е. Папп р бб2

ЦНИИПИ Государственного кОМитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Раушская наб. д. 4 5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4