Устройство для автоматической регулировки усиления

Иллюстрации

Показать всеРеферат

:оюз Советских

COQHilHHCTH9OCKHX

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено;070378 (21) 2588063/18-09 (51)М. Кл.

Н 03 G 3/20 с присоединением заявки ¹

Государственный комитет

СССР по делам изобретений н открытий (23) Приоритет

Опубликовано 150780. Бюллфтень ¹ 26 (53) УДК 621 396

666 (088. 8) Датаопублико аниясписания 150780 (72) Авторы изобретения

l0. М. Коршунов, А. В. Симкин и В. В. Симкин (71) Заявитель

Рязанский радиотехнический институт (54) УСТРОЙСТВО ЛЛЯ АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ

Изобретение относится к устройствам регулирования усиления и может использоваться для автоматического регулирования усиления с постоянным быстродействием, не зависящим от уровня входного сигнала, в системах телемеханики с время-иьатульсной, широтно-импульсной, частотно-импульсной н кодр-импульсной модуляцией. 10

Известно устройство для автоматической регулировки усиления, содержащее последовательно регулируемый усилитель, к управляющему входу которого подключен интегратор, элемент сравнения с заданным уровнем и перемножитель, а между выходом регулируемого усилителя:и входом сброса интегратора включены последовательно блок статистического обнаружения, 20 интервала существования импульсного сигнала и блок обнаружения исчезновения импульсной последовательности, причем другой вход перемножителя подключен к выходу блока статистическо- 25 го обнаружения интервала существования импульсной последовательности (1) .

Однако в известном устройстве быстродействие приведения последователь- 3п ности импульсов к нормированному уровню зависит от их амплитуды.

Цель изобретения — получение независимого от амплитуды входных импульсов быстродействия.

Для этого в устройство для автоматической регулировки усиЛения, -содержащее последовательно соединенные регулируемяй: усилитель, к управляющему входу которого подключен интегратор, элемент сравнения с заданным уравнем и перемножитель, а между выходом регулируемого усилителя и входом сброса интегратора включены последовательно блок статистического обнаружения интервала существования импульсного сигнала и блок обнаружения исчезновения импульсной последовательности, причем другой вход перемножителя подключен к выходу блока статистическогб обнаружения интервала существования импульсной последовательности, между выходом перемножителя и первым "входом,нйтегратора включен первый аттенюатор, Между выходом элемента сравнения с заданным уровнем и вторым входом интегратора включены последовательно дополнительный перемножитель и второй аттенюатор, а меж748801 ду выходом интегратора и управляющим входом каждого аттенюатора включена цепь нелинейной обратной связи, при этом другой вход дополнительного перемножителя соединен с противофаэным выходом блока статистического обнаружения интервала существования импульсной последовательности.

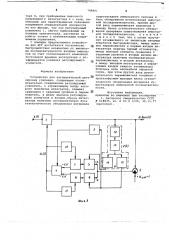

На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - кривая зависимости сопротивления аттенюаторов

R(u) в зависимости от выходного напряжения U(t):èíòåãðàòoðà.

Устройство à автоматической регулировки усиления содержит регулируемый усилитель 1, элемент 2 сравнения с заданным уровнем, перемножитель 3, интегратор 4, блок 5 обнаружения исчезновения импульсной последовательности, блок 6 статистического обнаружения интервала существования им-2О пульсного сигнала, первый аттенюатор

7, второй аттенюатор 8, дополнительный перемножителЬ 9, цепи 10 и 11 нелинейной обратной связи.

Блок 6 статистического обнаружения 25 интервала существования импульсного сигнала может, например, состоять из блока 12 смещения, активного вероятностного реле 13 и парафазных блоков

14 и 15. 30

Устройство работает следующим образом.

В исходном состоянии, при отсутствии сигнала 2 (t) на входе устройства, напряжение на выходе регулируемого усилителя 1 и на выходе интегратора 4 равны нулю. Сопротивление R(u) второго аттенюатора 8 имеет

1 бесконечно большое значение.

При поступлении на вход регулируемого усилителя 1 импульсной последо- 4О вательности, искаженной высокочастотной помехой, эта последовательность усиливается им в Йо (Д вЂ” коэффициент усиления) раз и подается на вход элемента 2 сравнения с заданным уровнем 4 стабилизации, принятым за единицу

Ucr = 1, На выходе элемента 2,сравне. ния образуется сигнал рассогласования Я (t) = Z (t) - 1, который поступает на первые: входы перемножителей 3 и 9. Одновременно сигнал с выхода регулируемого усилителя 1 через блок

12 смещения, смещающий этот сигнал на уровень — 0,5()„, поступает на зход активного вероятностного реле 13, ;.оторое обнаруживает моменты начала окончания импульсного сигнала, искаженного помехой на уровне нулевого порога (rio входу блока 12 смещения этот уровень соответствует значению порога + О, 5 0 ., ) . Активное вероят- 40 ностное реле 13 выдает на выходы перемножителей 3 и 9 через парафазные блоки 14 и 15 разнополярные напряжения + g (ф) и — Ч (% ), соответствующие по модулю вероятности превышейия 65 полезным импульсныМ сигналом порога

+ 0,5 U< . С выхода перемножнтеля 3 произведение 6.V положительной полярности поступает на вход первого аттенюатора 7, величина сопротивления которого определяется выходным сйг алом:цепи 10 нелинейной обратной связи, Первый аттенюатор 7 так же, как и второй аттенюатор 8 выполняет роль нелинейного сопротивления интеrратора 4: через первый аттенюатор 7 происходит заряд емкости интегратора

4, а через второй аттенюатор 8 — ее перезаряд. Сигнал U (t) с выхода интегратора 4 поступает на управляющий вход регулируемого усилителя 1, под действием которого изменяется коэффициент усиления Н (ц) регулируемого усилителя 1. При возрастании U на выходе интегратора 4 коэффициент усиления К регулируемого усилителя 1 уменьшается от максимального значения Ко до некоторого минимального значения. Одновременно .уменьшается ,и сопротивление первого аттенюатора

7 по кривой 16 (фиг. 2). Эта кривая по форме совпадает с кривой изменения коэффициента усиления Мо регулируемого усилителя. Такое согласованное изменение коэффициента усиления К (u) регулируемого усилителя 1 и сопротивления R ((/) первого аттенюатора 7 позволяет получить независимость быстродействня приведения последовательности импульсов к фиксированной амплитуде от величины их амплитуды.

В том случае, когда амплитуда: импульсного сигнала()Зь» (t.) на выходе регулируемого усилителя 1 за счет уменьшения амплитуды входного импульсного сигнала Z (t) становится меньше напряжения Ucт = 1, на выходе элемента сравнения 2 образуется сигнал рассогласования Е.(t) отрицательной полярности. Этот сигнал умножается в дополнительном перемножителе 9 на сигнал вероятности превышения импульсным сигналом порога 0,5 Uc . С выхода дополнительного перемножителя 9 сигнал отрицательной полярности — ЯЧ через второй аттенюатор 8 поступает на интегратор 4, где он интегрируется.

При этом сигнал О (t) на выходе интегратора уменьшается, что приводит к увеличению сопротивления разряда

R(U) емкости интегратора, роль которой выполняет второй аттенюатор 8.

При этом величина сопротивления второго аттенюатора 8 меняется по кривой

17 (фиг. 2). Эта кривая большей своей частью совпадает с кривой 16 и только при значении напряжения U, . близком к нулю, кривая 17 проходит выше кривой 16 и при дальнейшем приближении U к нулю уходит в бесконечность за счет специального выбора параметров цепи 11 нелинейной обратной связи . Такое увеличение сопротивления

R(U) цепи переэаряда емкости интегра148801 тора 4, при приближении выходного напряжения U интегратора 4 к нулю, необходимо для предотвращения появления напряжения отрицательной полярности на его выходе, так как регулируемый усилитель 1, обычно выполняемый на 5 полевых транзисторах, рассчитан на работу только с положительным напряжением управления.

С помОщью предлагаемого устройства для АРУ достигается постоянство быстродействия независимо от амплитуды последовательности входных импульсов за счет согласованного изменения постоянной времени интегратора с коэффициентом усиления регулируемого усилителя.

Формула изобретения

Устройство для автоматической pery- o лировки усиления, содержащее последовательно соединенные регулируемый усилитель, к управляющему входу которого подключен интегратор, элемент сравнения с заданным уровнем и перем- 5 ножитель, а между выходом регулируемого усилителя и входом сброса. интегратора включены последовательно блок статистического обнаружения интервала существования импульсного сигнала и блок обнаружения исчезновения импульсной последовательности, причем другой вход перемножителя подключен к выходу блока статистического обнаружения интервала существования импульсной последовательности, о т л и ч а

io щ е е с я тем, что с целью получения независимого от амплитуды входных импульсов быстродействия, между выходом перемножителя и первйм входом интегратора включен первый аттенюатор, между выходом элемента сравнения с заданным уровнем и вторым входом интегратора включены последовательно перемножитель и второй аттенюатор, а между выходом интегратора и управляющим входом каждого аттенюатора включена цепь нелинейной обратной связи, при этом другой вход дополнительного перемножителя соединен с противофазным выходом блока статистического обнаружения интервала существования импульсной последовательности.

Источники информации, принятые во "внимание при экспертизе

1. Авторское свидетельство СССР

9 618В35, кл. Н 03 G 3/20, 30.11.77 (прототип).

74880) Составитель Г.Челей

Техред М.Кузьма Корректор Н.Григорук

Редактор П.Макаревич

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Заказ 4383/21 1 ираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5