Цифровой фазовращатель

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ он748840

:l; (61) Дополнительное к ввт. свид-ву (22) ЗаявлеиоО 106.78 (21) 2625199/18-21 (51)М. Кл.

Н 03 К 5/153 с присоединением заявки Но (23) Приоритет

Государственный комитет

СССР но делам изобретений н открытий

Опубликовано 15.0 780. бюллетень Йо 26

Дата опубликовамия описания 150 7.80 (53) УДК 681. 325 (088. 8) (72) Авторы изобретения

В. A. Глаголев и С. Н. Малюков (71) Заявитель (54) ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ

Изобретение относится к радиотехнике, в частности используется в качестве исполнительного элемента систем автоматического сопровождения сигнала по фазе, частоте или временной задержке. . Известен цифровой фаэовращатель, содержащий счетчик, выходы которого соединены с первыми входами блока сравнения, вторые входы которогО подключены к выходам фазозадающего блока, и триггер, сигнал на выходе которого является выходным сигналом фаэовращателя (1).

„15

Недостаток известного устройства низкая точность установки фазы выходного сигнала из-за разброса и нестабильности сигнала в триггерах

: счетчика и логических схемах- блока

: сравнения. Кроме того, влияние упомянутых факторов, а также конечного времени срабатывания элементов устройства приводит к возникновению ложных срабатываний выходного триггера. з5

К недостаткам данного устройства следует отнести снижение выходной частоты вдвое по сравнению с частотой совпадения кодов на выходах счетчика и фэзозадающегс блока. Из-за этого для обеспечения заданной частоты на выходе фазовращателя частоту входного сигнала приходится повышать в два раза, что приводит к необходимости . использования в устройстве более высокочастотной элементной базы.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее счетчик, подключенный к выходу задающего генератора, блок сравнения, соединенный с выходами счетчика и фазоэадающего блока, счетный триггер, подключенный к выходу последнего разряда счетчика, элементы однозначности и элементы неоднозначности, одни входы которых соединены с выходами счетного триггера и входом фильтра, а другие — с выходом фаэоэадающего блока, элементы совпадения, первые входы которых подключены к выходу блока сравнения, а вторые входы - к выходам, соответственно, элемент однозначности и элемент неоднозначности, триггер с раздельным управлением, входы которого соединены с выходами элементов совпадения, а выход — с входом фильтра E2) .

748840, Недостаток этого устройства — низ" кая точность установки фазы и наличие ложных срабатываний.

Цель изобретения - повьыение точности установки фазы и исключение ложных срабатываний.

Цель: достигается тем, что в цифровой фаэовращатель, содержащий счетчик, выходы которого подключены к первым входам блока сравнения, вторые входы которого соединены с выходами фазозадающего блока, триггер с раздельным управлением, введены два тактируемых фильтра с памятью, сигнальный вход каждого из которых соединен с соответствующим выходом блока сравнения, а выходы каждого .тактируемого фильтра с памятью подключены к соответствующим входам триггера с раздельным управлением, причем тактовые входы упомянутых

Фильтров соединены со счетным входом счетчика.

В указанном устройстве тактируеьне фильтры с памятью могут быть выполнены в виде синхронных D-триггеров с двойной памятью.

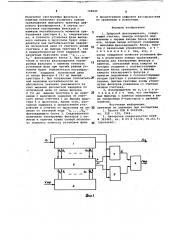

На фиг. 1 представлена функциональ-2 ная схема устройства; на фиг. 2 эпюры импульсов.

Цифровой фаэовращатель содержит счетчик 1, выходы которого подключены к первым входам блока 2 сравнения, вторые входы *оторого соединены с выходами фазозадающего блока 3, а выходы блока 2 сравнения подключены к информационным входам тактируемых фильтров 4 и 5 с памятью, например, выполненных в виде синхронных D-триггеров с двойной памятью, причем тактовые входы фильтров 4 и 5 соединены со счетным входом счетчика 1, а выходы упомянутых фильтров 4 и 5 подключе-. ны к выходам триггера с раздельным уп-40 равлением б.

Устройство работает следующим образом. °

На счетный вход счетчика 1 прстуцдвт входные импульсы с частотой fp 45 и периодом „ (эпюра Х на фиг. 2).

При этом пройсходит периодическое изменение кода, записанного в счетчике 1 с периодом Т „= 1/ оп = 2 / где и — число разрядов счетчика 1.

Изменяющийся код Cl О„ с вы1) ходов разрядов счетчика 1 поступает на первые входы блока 2 сравнения,на вторые входы которого поступает код ,..., Ь„ с выходов Фазозадающего блока 3. На выхбдаж P т Р> блока

2 сравнения синхронно с моментами совпадения кодов,формируются:импульсы с частотой повторения Х =1 /2"

1/Т и длительностью 1 б„, >jp/2 сдвинутые друг относительно друга íà 40 половину периода частоты 1,„ . Однако, кроме этих импульсоа на выходах

Р и Р" будут присутствовать импульсы, наличие которых обусловлено влиянием конечных задержек и времени срабаты- 5 вания реальных элементов цифрового фаэовращателя (эпюра P-II,III фиг. 2).

Параэитные импульсы на выходах блока 2 сравнения могут быть представлены в виде сумьн последовательностей

5 импульсов имеющих ту же частоту повторения, что и полезные (эпюра

P-I фиг. 2) но имеющих случайную длительность Ф „ и случайную задержку

Ф п относительно полезных. В диапазо не рабочих частот цифрового фазовращателя суммарная максимальная задержка по самой длинной логической цепи фазовращателя с учетом максимального времени срабатывания эле5 ментов остается меньшей половины периода Го входных импульсов на величину, обеспечиваемую устойчивое срабатывание элементов фазовращателя: Т„ "p/2 . В то же время дли-. тельность Толезных импульсов остает2О ся большей длительности половины периода входных: Ф Þ /2 . В этом случае длительность паразитных импульсов существенно меньше длительности полезйых. Смесь полезных и паразит5 ных импульсов с выходов Р и Р> блока

2 сравнения поступает на сигнальные входы тактируемях фильтров 4 и 5 с памятью, на тактовые входы которых подаются входные импульсы частоты Р„. Изменение информации на выходах фйльтров 4 и 5 будет происходить только в том случае, если импульс, на сигнальном входе фильтра не только совладает с тактовым, но и целиком перекрывает его.

С учетом различий в длительности iroлезных и паразитных импульсов становится очевидным, что информация на выходах тактируемых фильтров 4 и 5 с памятью будет изменяться только при поступлении на их сигнальные входы полезных импульсов, что наглядно иллюстрируется эпюрами 1, Р и д на фиг. 2. В качестве тактируемого фильтра с памятью может быть использован синхронный D-триггер с двойной памятью, серийно выпускаемый промышленностью. При этом наличие в D-триггере двойной памяти будет обеспечивать неизменность его выходного состояния при попадении на его информационный D вход паразитного импульса и одновременном поступлении на его тактовый С вход входных импульсов.

Таким образом, íà входы триггера с раздельным управлением б будут поступать последовательности только полезных импульсов, сдвинутые друг относительно друга на половину периода частоты У ы и начальной фазой, определяемой моментом совпадения кодов на выходах счетчика 1 и фазозадающего блока.З. Изменение кода

b„ на выходе фазозадающего блока

3 будет вызывать изменение начальной фазы меандра на выходе триггера б с минимальным дискретом b. Р„;и — — ЗбО/2"

748840

Включение -.актируеыях фильтров с . памятью позволяет исключить ложные срабатывания выходного триггера цифрового фаэовращателя. В случае отсутствия тактируемых фильтров с памятью нестабильность моментов срабатывания триггера 6, а, следовательно, и точность установки фазы выходного сигнала в прототипе будут определяться как нестабильностью задержки логической цепи от счетного входа счетчика 1 до выхода триггера 6, так и неидентичностью этой задержки при различных значениях кода Ь,,..., Ь„ фаэозадающего блока 3. При включзнии в состав фазовращателя тактируемых фильтров с памятью точность установки фазы при прочих равных условиях будет опРеделяться нестабильностью задержки логической цепи от входа фйльтра 4 (5) до выхода ., триггера 6. При сохранении относитель-_#_ ной величины нестабильности ее абсолютное значение уменьшается за счет меньшей абсолютной задержки по логической цепи от входа фильтра

4 (5) до выхода триггера 6 по срав- 25 нению с величиной задержки от счетного входа счетчика 1 до выхода триггера 6 в прототипе, Кроме того, указанная задержка в предлагаемом устройстве в отличие от прототипа не за- 30 висит от значений кода . .., Ьп фазозадающего блока 3. Следовательно включение тактируемых фильтров с памятью и наличие новых связей позволяет повысить точность установки фазы 35 в предлагаемом цифровом фазовращателе по сравнению с известным.

Формула изобретения

1. цифровой фаэовращатель, содержащий счетчик, выходы которого подключены к первым входам блока сравнения, вторые входы которого соединены с выходами фазоэадающего блока, триг" гер с раздельным управлением, ...o тличающийс я тем, что, с целью повышения точности установки фа" зы и исключения ложных срабатываний, введены два тактируемях фильтра с памятью, сигнальный вход каждого иэ которых соединен с соответствующим выходом блока сравнения, а выходы каждого тактируемого фильтра с памятью подключены к соответствующим входам триггера с раздельным управлением, причем. тактовые входы упомянутых фильтров соединены со счетным входом счетчика.

2 ° Фаэовращатель по п.l,î т л ич а ю шийся тем, что тактируеьые фильтры с памятью выполнены в виде синхронных D-триггеров с двойной памятью.

Источники информации, принятые во внимание при экспертизе

1. Патент CIJA 9 2910586, кл. 328 — 155, 1964.

2. Авторское свидетельство СССР

9 362465, кл. Н 03 К 13/20, 01.03.71 (прототип).

748840

Составитель И.Радько

Техред М.Келемеш Корректор H.Григорук

Редактор М.Келемеш

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Закаэ 4363/21 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР. по делам иэобретений H открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5