Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сокээ Советских

Социалистических

Республик

< 748863 (6I ) Дополнительное к ввт. свид-ву (22) Заявлено 10.05.78(21) 2612335/18-21 (5! )М. Кл.

Н 03 К 13/17 с присоединением заявки №

Гвеудврстввииый квмитет (23)Приоритет (53) УД К 681.325 (088.8) пп делам иэабретений и открытий

Опубликовано 15.07.80. Бюллетень ¹ 26

Дата опубликования описания 18.07.80 (72) Авторы изобретения

IG. В. Полубабкин, Ю. П. Прозоров, В. П. Сафронов и В. М. Шляндин

Пензенский политехнический институт (7I) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к измерительной и вычислительной технике и может быть использовано для преобразования аналоговых сигналов в цифровой код, Известен преобразователь напряже. ния в код, содержащий схему сравнения с выходным каскадом, распределитель импульсов, шфроаналоговый преобразователь, генератор импульсов запуска, вентили, дискриминаторы положительного и отрицательного уровней и схему ИЛИ, то причем входы дискриминаторов соединены с соответствующими выходами схемы сравнения, а выходы дискриминаторов через схему ИЛИ подключены к венти15 лю, другой вход которого соединен с выходом источника импульсов запуска (1).

Данный преобразователь обладает малым быстродействием, вследствие применения точного преобразователя коднапряжение и точного блока сравнения, требующих большего времени установления, Известен также преобразователь напряжения в цифровой код, содержащий два

2 пороговых элемента, преобразователь код-напряжение, регистр, логический блок, распределитель импульсов, блок запрета, генератор импульсов f2) .

Недостаток устройства состоит а малом быстродействии, так как оно имеет два канала преобразования: грубый и точный, т.е. грубые операции уравновешивания корректируются точными тактами. Поэтому цикл преобразования такого преобразователя разбивается на грубые операции уравновешивания и несколько точных корректирующих операций уравновешивания, которые по длительности значительно больше, чем грубые такты.

Дель изобретения — повышение быст-. родействия преобразователя.

Поставленная цель достигается тем, что в аналого-пирровой преобразователь, содержащий генератор импульсов, выход которого соединен с первым входом блока запрета, выход которого соединен со входом распределителя импульсов, первые

48863 ф

15

3 7 выходы которого соединены с первыми входаь и логического блока и первыми входами регистра, а выходы логического блоха соединены со вторыми входами регистра, причем выходы регистра соединены со входами преобразователя коднапряженне, выход которого соединен с первыми входами первого и второго пороговых элементов, введены усилитель разности, переключающий блок, триггер, дополнительный преобразователь кодйатфяжение, регистр-счетчих и дополнительный логический блок, причем шина входного сигнала соединена. с вторым входом первого порогового элемента и первым входом усилителя, выход которого соединен со вторым входом второго порогового элемента, а его второй вход соединен с выходом дополнительного преобразователя код-напряжение, входы которого соединены с единичными выходами регистра-счетчика, в котором нулевой выход предыдущего .разряда соединен со счетным входом последующего разряда, причем счетный вход первого разряда соединен с первым выходом логического блока, входы регистра-счетчика соединены с выходами дополнительного логического блока, первые входы которого соединены с выходами регистра, вторые входы соединены с выходами расйределителя импульсов, а третьи входы со вторым входом блока запрета, с единичным выходом триггера и с первым входом переключающего блока, при этом второй выход распределителя импульсов соединен со входом триггера, нулевой выход которого соединен со вторым входом переключающего блока, третий вход которого соединен с выходом первого порогового элемента, а четвертый вход с выходом второго порогового элемента, при этом выход соединен со вторыми входами логического блоха.

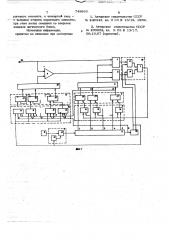

На фиг. 1 представлена структурная схема аналого-цифрового преобразователя, на фиг. 2 — диаграмма работы . устройства;

Оно содержит пороговые элементы 1, 2, преобразователь код-напряжение 3, реристр 4, состоящий из триггеров 17 памяти, логический блох 5, состоящий из элементов совпадения на каждый разряд, распределитель 6 импульсов, блок 7 запрета, состоящий из элемента совпадения и одновибратора 16, генератор 8 импульсов, усилитель 9 разности, переключакцц и блок 10, состоящий иэ двух элементов совпадения и элемента

ИЛИ, триггер ll, дополнительный преобразователь код-напряжения 12, регистр-счетчик 13 и дополнительный логический блок 14 состоящий из элементов совпадения на три входа.

Устройство работает следующим образом. В начальный момент времени триггер 11 находится в таком состоянии, что открыт элемент совпадения в переключающем блоке 10, который пропускает информацию с порогового элемента 1, этим же сигналом открыты все элементы совпадения в дополнительном логическом блоке 14 и элемент совпадения в блоке 7 запрета. Импульсы с генератора 8 импульсов поступают на распределитель 6 импульсов. Начинается поразрядная отработка компенсирующим напряжением (Ок ) преобразователем код-напряжение 3 входного сигнала.

Причем уравновешивание происходит на первом пороговом элементе, тах как только q него информация о процессе уравновешивания поступает на логический блок Б, информация со второго порогового элемента не снимается, так хак закрыт er î элемент совпадения триггера 1 1.

Одновременно информация с регистра

4 при помощи дополнительного логического блока 14 и тактовых импульсов распределителя импульсов записывается в регистр-счетчик 13., Таким образом, с началом процесса уравновешивания входного сигнал а 0„компенсирующим напряжением Ц< грубого преобразователя код-напряжение 3 начинает выделяться и усиливаться разность усилителем 9 разности между входным сигналом U и точным дополнительным преобразователем код-напряжение 12. Это сделано для уменьшения времени, отводимого на такт коррекции, так как усилитель 9 разности успеет выйти из насыщения эа время уравновешивания входного сигнала на первом пороговом устройстве и будет находиться в активной зоне, за 4р счет чего значительно уменьшится переходной процесс после окончания процесса уравновешивания на первом пороговом элементе. После окончания npo åññà уравновешивания входного сигнала О компенсирующим напряжением

U на пороговом элементе 1 последним тактовым импульсом (его задним фронтом) распределителя 6 импульсов перебросится триггер 1 1,который запустит одновибратор в блоке 7 запрета и им8863 в результате чего уменьшается время .такта уравновешивания, Особенно большой выигрыш в оборудовании и быстродей ствии достигается при построении прецизионных быстродействующих преобра зователей напряжение-код () 11 разрядов).

74 пульсы с генератора rrymbcoa не будут поступать на распределитель импульсов,, в то же время в дополнительном логическом блоке 14 будут закрыты все элементы совпадения нулевым уровнем триггера 11, кроме одной, которая тактируется последним импульсом распределителя импульсов. В переключающем блоке 10 в это время триггер 11 закроет элемент совпаденияпервого rroporo- iо Ф о р м у л а и з о 6 р е т e H H я вого элемента и откроет элемент совпадения второго порогового элемента. В Аналого-цифровой преобразователь, результате чего во втором такте цикла содержащий генератор импульсов, выход преобразования будет уравновешиваться которого соедийен с первым входом у енная разность усилителя 9 5 блока запрета выход которого соединен разности между входным сигналом и со входом РаспределителЯ импУльсов, компенсирующим напряжением 0>< пре- первые выходы которого соединены с образователя код-напряжение 12 (см. первыми входами логического блока и фиг.2). Как только переходной процесс rreprrbrìè входами регистра, а выходы в усилителе разности закончится окон- о логического блока соединены со вторыми чательно (а длительность запрещающего входами Регистра, причем выходы реимпульса одновибратора выбирается гистра соединены со входами преобраисходя из динамических свойств усилите- зователя код-напряжение, выход которого ля разности), единичный уровень с одно- соединен с первыми входами первого вибратора 16 откроет элемент совпаде- j5 H второго пороговых элементов, о т— .ния в блоке запрета и импульсы с гене- л и ч а ю шийся тем, что, с целью ратора импульсов начнут поступать на повышения быстродействия, в него ввераспределитель импульсов. Начнется по- лены усилитель разности йереключающий

) разрядная отработка на пороговом эле- блок, триггер, дополнительный Irpeoápaменте 2 усиленной разности напряжений Зф зователь Kog-напряжение, регистр-счет входного сигнала и компенсирующего. чик и дополнительный логический блок, После того как процесс уравновешивайия причем шина входного сигнала соедйнезакончится, производится коррекция ре- Ha c BTOPbrM вХОдОМ первоГо пбрбгОвоГ р зультата преобразования, произведен- . элемента и первым входом усилителя, ного на первом пороговом элементе, ко- выход которого соединен со вторым торый хранится в счетчике-регистре 13. входом второго порогового" элемента, а

Коррекция производится в конце всего его второй вход соединен с выходом доцикла преобразования импульсов с шины "полнительного преобразователя код-на6 распределителя импульсов, В течение пряжение, входы которого соединены с этого времени производится съем 40 единичными выходами регистра-счетчика, информации с шин регистра-счетчика 13 в котором нулевой выход предыдущего (старшие разряды) и шин, кроме 1-ой, Разряда соединен со счетным входом регистра 4 (младшие разряды). Таким последующего разряда причем счетнь и б

ы о разом, весь цикл преобразования (фиг.2) вход первого разряда соединен с первым состоит из двух тактов уравновешивания, 4 выходом дополнительного логического

45 а они в свою очередь состоят из элемен- блока, входы регистра счетчика соедитарных тактов уравновешивания, причем: иены с выходами дополнительного логи1-ый элементарный такт уравновешива- ческого блока, первые входы которого ния второго такта в цикле преобразования соединены с выходами регистра, вторые предназначен для коррекции инструмен- о входы соединены с выходами распреде тальной погрешности старших разрядов, лителя импульсов, а третьи входы — со определяемых на первом такте, вторым входом блока запрета, с единичВнедрение аналого-цифрового преоб- ным выходом триггера и с первым входом разователя обеспечивает по сравнению переключающего блока, при этом второй с известными устройствами более вы- выход распределителя импульсов соедисокое быстродействие при малых аппа- нен со входом триггера, нулевой выход ратурных затратах, так как простой по- которого соединен со вторым входом разрядный преобразователь строится на переключающего блока, третий вход комалоточных быстродействующих узлах, торого соединен с выходом первого по748863

7 рогового элемента, а четвертый вход— с "выходом второго порогового элемента, при этом выход соединен со вторыми входами логического блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 240343, кл. Н СЗ К 13/18, 1969..

- 2. Авторское свидетельство СССР

% 200882, кл. Н 03 К 13/17, 09.10;67 (прототип) .

Г

I !

Г

748863

Ул

Состою

6конн иикла

n eobw

+-4ц у-с

Составитель Л. Беляев

Редактор О. Колесникова Техред М. Петко Корректор М. Коста

Заказ 4384/22 Тираж 99 5 " Подписное

Ш1ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патейт, r, Ужгород, ул . Проектная, 4