Устройство для асинхронного сопряжения каналов связи

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистичвскии

Республик (61) Дополнительное к авт. саид-ау(22) Заявлено 15. 12. 77 (21) 2555198/18-09 с присоединением заявки М(23) Приоритет—

Опубликовано 15,07.80 Бюллетень g9 26

Дата опубликования описания 170780 (53)м. кл

Н 04 1 25/36 //

Н 04 L 7/04 //

H 04 Г 3/08

Государственный комнтет

СССР

II0 делам нзобретеннй н отнрытвй (. Ç) УДИ6 2 1 . 3 9 4 . 6 (088. 8) A. Н. Варфоломеев, Н. Ф. Андрияш, В. Н. Туманович и В. С. Коган (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АСИНХРОННОГО СОПРЯЖЕНИЯ

КАНАЛОВ СВЯЗИ

Изобретение относится к электросвязи и может быть использовано в многоканальных системах с временным разделением каналов.

Известно устройство для асинхронного сопряжения каналов связи в сис- . темах с временным разделением каналов, содержащее на передающей стороне последовательно соединенные блок фаэовой автоподстройки частоты, блок памяти, фазовый дискриминатор и блок управления, причем на вход блока фазовой автоподстройки частоты и на второй вход блока памяти подан абонентс-,15 кий сигнал,на третий вход блока памяти поданы считывающие,импульсы,а четВертый вход блока памяти соединен с первым выходом блока управления, второй выход блока памяти подключен к основ-20 ному каналу связи, а второй выход блока управления — к дополнительному каналу связи, и на приемкой стороне последовательно соединенные дешифратор команд, блок памяти и фазовый дио2 криминатор, при этом вход дешифратора команд соединен с дополнительным каналом связи, второй вход блока памяти соединен с основным каналом связи, на третий вход блока памяти поданы имЗО пульсы записи, к четвертому входу подключен выход блока формирования частоты считывания, а выход блока памяти является выходом устройства flj .

ОднакО в известном устройстве необходимо нали ие второго дополнительного канала связи, по которому передаются сигналы фазовой коррекции, что приводит к снижению пропускной способности устройства.

Цель изобретения — повышение пропускной способности без увеличения фазовых искажений сигналов.

Для этого в устройство для асинхронного сопряжения каналов связи в системах с временным разделением каналов, содержащее на передающей стороне последовательно соединенные блок фазовой автоподстройкн частоты, блок памяти, фазовый дискриминатор и блок управления, причем на вход блока фаэовой автоподстройки частоты и на второй вход блока памяти подан абонентский сигнал, на третий вход блока памяти поданы считывающие импульсы, а четвертый вход блока памяти соединен с первым выходом блока управления, второй выход блока памяти подключен к основному каналу связи, а второй выход блока управления — к дополнитель748896 ному каналу связи, на приемной стороне — последовательно соединенные дешифратор команд, блок памяти и фазо- . вый дискриминатор, прк.этом вход дешифратора команд соединен с дополнительным каналом связи, второй вход .блока памяти соединен с основным ка-, "налом связи„ на третий вход блока памяти поданы импульсы записи, к четвертому входу подключен выход блока формирования частоты считывания, а выход блока памяти является выходом устройства, на приемной стороне введены последовательно соединенные синтезатор сигналов низких частот и блок управления скоростью считывания, выход которого подключен к входу блока фор- 15 мирования частоты считывания, причем второй вход блока управления скоростью считывания соединен с первым выходом блока памяти, третий вход соединен с выходом фазового дискрими- Щ натора, выход блока формирования частоты считывания подключен к четвер-. тому входу блока памяти, а на вход синтезатора сигналов низких частот поданы управляющие импульсы.

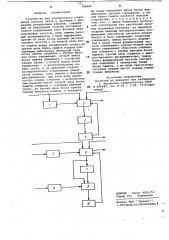

Ба чертеже представлена структурная схема устройства для асинхронного сопряжения каналов.

Устройство содержит на передающей стороне блок 1 фазовой автоподстройки частоты, блок 2 памяти, фазо- ®О вый дискриминатор 3 и блок 4 управления, а на. приемной стороне — дешифратор 5 команд, блок б памяти, фазовый дискриминатор 7, синтезатор 8 сигналов низких частот, блок 9 управления скоростью считывания и блок 10

/ формирования частоты считывания.

Устройство работает следующим образом. асинхронный абонентский сигнал 4О поступает на блок 1 фазовой автоподстройки частоты, который формирует импульсную последовательйость, синхронную с абонентским сигналом, преднаэначеннуюс для записи в блок 2 па- 45 мяти. Считывание информации из блока 2 памяти производится импульсами, синхронными с тактовой частотой канаь ла связи, при; этом информация передается по основному каналу связи. Фа- 5О зовый дискриминатор 3 контролирует сдвиг фазы между импульсами записи и считываний блока 2 памяти и при разности фаэ + Йс выделяет сигнал, по которому блок 4 управления вырабатыва -55 ет команду стаффинга "+" (добавить) или "-"{убавить) в зависимости от знака сдвига фаэ. Комайда стаффинга передается по дополнительному каналу в виде пятнадцатисимвольной кодовой комбинации, при этом команде "+" соответствует последовательность из пятнадцати- единиц, а- команде -" — из пятнадцати нулей. В фиксированный момент времени, определяемый сверхцйкловой синхронизацией группового обору- 65 дования передающей станции произво дится одна из двух операций:

1 Если по дополнительному каналу передавалась команда "+" то по этоC му каналу передается один информационный бит из эластичной памяти, прк этом запас информации в блоке эластич ной памяти уменьшается на один бит.

2. Если по дополнительному каналу передавалась команда "-", то по основному каналу передается балластная посылка, и запас информации в блоке памяти увеличивается на один бит. Та" ким образом, по дополнительному каналу передаются чередующиеся команды ."+" и "-" до тех пор, пока фазовый сдвиг между импульсами записи и считывания из блока памяти не превысит

2 . В этом случае дважды передается одна и та же команда. Следовательно, структура передаваемых по дополнительному каналу команд стаффинга имеет вид (+-+-+-++-+-),еслк частота записи абонента выше частоты считывания канала связи, и (+-+-+--+-+-) если частота записи абонента ниже частоты считывания канала связи. Таким образом, в последовательности команд дополнительного канала заложена .информация о частоте асинхронного або,нента.

На приемной стороне дешифратор 5 команд осуществляет прием команд стаффинга и выдает сигнал управления "добавить" или "убавить" в блок б памяти.

Информационный сигнал, принятый по основному каналу, записывается в блок 6 памяти. В фиксированный момент времени, определяемый сверхцикловой синхронизацией группового оборудования приемной станции, осуществляется либо вставка информационной посылки, принятой. по дополнительному каналу (при наличии сигнала "добавить", поступающего из дешифратора 5 команд), либо исключение балластной посылки, принятой по основному каналу (при наличии сигнала "убавить" ). Считывание информации из блока 6 памяти производится импульсной последовательностью, сформированной блоком 10 формирования частоты считывания, который представляет собой управляеьый дели-. тель, подстраивающий дискретным способом выходную последовательность импульсов в зависимости от того, в каком разряде блока б памяти происходит считывание информации.

Фазовый дискриминатор 7 сравнивает сдвиг фаз между импульсами записи и считывания блока б памяти и при расхож-. дении фаз на + 2 вырабатывает сигнал о знаке расхождения частот абонента

I и канала связи, который поступает на блок 9 управления скоростью.

748896

Формула изобретения

Устройство для асинхронного сопряжения каналов связи в системах с временным разделением каналов, содержащее на передающей стороне последовательно соединенные блок фазовой авто. подстройки частоты, блок памяти Жазосвый дискриминатор и блок управления, причем на вход блока фазовой автоподстройки частоты и на второй вход бло- о ка памяти подан абонентский сигнал,на третий вход блока памяти поданы считывающие импульсы,а четвертый вход блока памяти соедйнен с первым выходом блока управления, второй выход блока памяти подключен к основному каналу связи, а второй выход блока управления — к дополнительному каналу связи, и на приемной стороне— последовательно соединенные дешифратор команд, блок памяти и фазовый 20 дискриминатор, при этом вход дешифратора команд соединен с дополнительным каналом связи, второй вход блока памяти соединен с основным каналом связи, на третий вход блока памяти 2$ поданы импульсы записи, к четвертому входу подключен выход блока фор-, мирования частоты считывания, а выход блока памяти является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения пропускной способности без увеличения фазовых искажений сигналов, на приемной стороне введены последовательно соединенные синтезатор сигналов низких частот .и .блок управления скоростью считывания, выход которого подклв« чен к входу блока формирования частоты считывания, причем второй вход блока управления скоростью считывания соединен с первым выходом блока памяти, третий вход соединен с выходом фазового дискриминатора, выход блока формирования частоты считывания подключен к четвертому входу блока памяти, а на вход синтезатора сигналов низких частот поданы управ- ллющие импульсы.

Источники информации, принятые во внимание при экспертизе

Авторское свидетельство СССР

В 496687, кл. Н 04 L 7/04, 1974(прототип).

ЦНИИПИ Заказ 4265/51

Тираж 729 Подписное

Филиал ППП Патент, г.Ужгород,ул.Проектная,4