Избирательное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советсиии

Социалистических

Республик

„„748912 (61) Дополнительное к авт, сеид-ву— (22) Заявлеио07.04 78 (21) 2601822/18-09 (51)М. Кл.

Н,04 0 3/06 с присоединением заявки Йо(23) Приоритет—. Государственный комитет

СССР по.делам изобретений и открытий

Опубликовано150780 Бюллетень М26

Дата опубликования описания 17р 78р (53) УДК 621. 395. .344(088.8) (72) Авторы изобретения

Т. 3. Козловска и С. Я. Озолиня (7! ) Заявитель

Рижский ордена Ленина государственный электротехнический завод ВЭФ им. В. И. Ленина (54) ИЗБИРАТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к телеграфии. Устройство может использоваться в блоках концентрации коммутаторов электронно-телеграфной станции.

Известно избирательное устройство, содержащее логические блоки, входы которых соединены с выходами соответствукФдих блоков коммутации, каждый из которых содержит селекторы сигналов, входы и выходы которых являются соответственно входами и выходами блоков коммутации, причем входы соответствующих селекторов сигналов подключены к линиям связи 11 .

Однако известное устройство имеет 15 низкое быстродействие.

Цель изобретения. — повышение быстродействия.

Для этого в избирательное устройство, содержащее логические блоки, 20 входы которых соединены с выходами соответствующих блоков коммутации, каждый из которых содержит селекторы сигналов, входы и выходы которых являются соответственно входами и выходами блоков коммутации, причем входы соответствующих селекторов сигналов подключены к линиям связи, введейы блок управления и сумматор, причем выходы сумматора соединены с вхо- 30 дами одного из блоков коммутации и блока управления, выходы которого под ключены к дополнительным входам соответствующих логических блоков, а входы сумматора соединены с линиями связи.

Селектор сигналов содержит инвертор, формирователь сигналов, регистр сдвига и генератор, выходом подключенный к входу регистра сдвига, выходы которого соединены с одними входами формирователя сигналов, другие входы которого соединены соответственно с входами и выходами инвертора, при этом входы инвертора и выходы формирователя сигналов являются соответственно входами и выходами селектора сигналов. Логический блок содержит элементы И, соответствующие входы которых объединены, а входы и выходы элементов И являются соответственно входами и выходами логического блока.

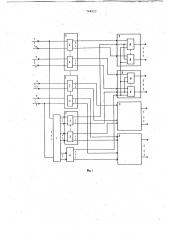

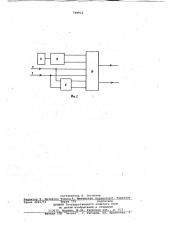

На фиг. 1 изображена структурная электрическая блок-схема предложенного устройства, на фиг. 2 показан вариант выполнения селектора сигналов.

Устройство содержит сумматор 1 блоки 2 коммутации, каждый из которых

748912 содержит селекторы 3 сигналов, блок

4 управления, логические блоки 5, каждый из которых содержит элементы

И 6, и линии связи 7.

Селектор сигналов iфиг. 2) содер,жит регистр 8 сдвига, инвертор 9, фор мирователь 10 сигналов и генератор 11. устройство работает следующим образом.

При поступлении на линии связи 7 сигналов, последовательность поступления которых случайная, селекторы 3 (0 сигналов выбирают на обслуживание од.:ну из обслуживаемых линий связи 7, включенных в каждый селектор 3 обслуживания требований. Одновременно сигналы требований поступают на входы сумматора 1. В результате сложения возбуждаются информационные выходы сумматора причем каждый иэ них соответствует сумме входов одного селектора 3 сигналов. Информационные входы включены в блок 2 коммутации, который выполняет функцию блока подготовки выбора. Каждый выход этого блока соединен с вторыми входами элементов И 6 соответствующего селектора сигналов. Выходы блока 2, выполняющего функции блока подготовки выбора, подготавливают срабатывание определенных элементов И. Одйовременно с появлением сигналов на информационных выходах сумматора 1 в ре- 30 зультате сложения входов каждого блока 2 сигналы возникают и на выходах посылки регистрации требований сумматора. Выходы посылки регистрации требований соединены с блоком 4 уп- 35 равления. Блок 4 формирует управляющий сигнал, который поступает на один из управляемых входов логического блока 5. Управляющий сигнал по управляемому входу логического блока 40 поступает на входы тех элементов И6 которые включены в выходы соответствующего блока 2 коммутации. Совпадение сигналов по всем трем входам в элементе И 6 вызывает появление сигнала на том выходе логического бло-< ка 5, который соответствует выбранной обслуживаемой линйи связи 7.

Селектор сигналов запускается при появлении на одном или нескольких обслуживаемых линиях связи сигнала 50 требования. Сигналы требования поступают на вторую группу входов формирователя 10 сигналов ббслуживания.

Сигналы требования поступают также на входы инвертора 9 и после прохожде- у ния через него поступают на третью группу входов формирователя 10 сигналов обслуживания. На первую группу входов формирователя 10 сигналов обслуживания поступают сигналы от генератора 11, преобразованные регистром 8 сдвига в параллельный код.

Формирователь 10 сигнала обслуживания формирует сигнал обслуживания на том выходе селектора 3 сигналов, на вход которого поступили сигнал требования и управляющий сигнал с выходов регистра 8 сдвига. !

Предложенное устройство по срав,нению с известным имеет более высокое быстродействие за счет уменьшения количества ступеней, состоящих из блоков коммутации;

Формула изобретения

1. Избирательное устройство, содержащее логические блоки, входы которых соединены с выходами соответствующих блоков коммутации, каждый из которых содержит селекторы сигналов, входы и выходы которых являются соответственно входами и выходами блоков коммутации, причем входы соответствующих селекторов сигналов подключены к линиям связи, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства,в него введены блок управления и сумматор, выходы которого сое динены с входами одного из блоков ком мутации и блока управления, выходы которого подключены к дополнительным входам соответствующих логических блоков, а входы сумматора соединены с линиями связи.

2. Устройство по и. 1, о т л и ч а. ю щ е е с я тем, что селектор сигналов содержит инвертор, формирователь сигналов, регистр сдвига и генератор, выход которого подключен к входу регистра сдвига, выходы которого соединены с одними входами формирователя сигналов, другие входы которого соединены соответственно с входами и выходами инвертора, при этом входы инвертора и выходы формирователя сигналов являются соответственно входами и выходами селектора сигналов.

3, Устройство по п. 1, о т л и ч а ю щ е е с я тем, что логический блок содержит элементы И, соответствукиаие входы которых объединены, а входы и выходы элементов И являются соответственно входами и выходами логического блока.

Источники информации, принятые во внимание при экспертизе

1. Патент ФРГ Р 1277935, кл. 21 а 30/01, 1969 (прототип).

748912

Тираж 729 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва, Ж-35 Раушская наб., д. 4/5. Заказ 4265/51

Филиал ППП "Патент", r. Ужгород, ул. Проектная, Составитель Е. Погиблов

Редакто Т. Юрчикова Техред A. Щепанская КорректорГ. Решетник