Устройство для контроля полупроводниковой памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социал нсткческих

Республик

»» 749887 (6I ) Дополнительное к авт. свил-ву— (22) Заявлено 27.06.78 (2! ) 2633894/18-24 (5I)M. Кл.

С 11 С 29/00 с присоединением заявки №вЂ”

Государственный комитет (23) Приоритет

Опубликовано 23.07.80. Бюллетень № 27

Дата опубликования описания 25.07.80 ло делам изобретений и открытий (53) УДК

681,327 (088.8) (72) Авторы изобретения

А. А. Гаврилов и В. А. Гаврилов

Институт электроники и вычислительной техники,, AH Латвийской CCP (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЛУПРОВОДНИКОВОЙ

ПАМЯТИ

Изобретение относится к области запоминающих устройств.

Известно устройство, содержащее генератор тактовых импульсов, соединенный с генератором тестовой последовательности и блок анализа

5 реакции испытуемой памяти на формируемые генератором тестовые воздействия (1) .

Недостаток устройства заключается в том, что оно не обеспечивает локализацию неисправностей.

Наиболее близким техническим решением к данному является устройство для контроля полупроводниковой памяти, содержащее генера. тор тактовых импульсов, генератор тестовой последовательности, блок управления, блок формирования временной диаграммы, блок согласования уровней, компаратор, причем выход генератора тактовых импульсов подключен ко входу генератора тестовой последовательности и входу блока формирования временной диаграммы, выходы которого соединены с первыми входами блока согласования уровней, управляющие входы генератора тактовых импульсов, генератора тестовой последовательности и блока формирования временной диаграммы подключены к одним из выходов блока управления, одни из входов которого соединены с выходами генератора тактовых импульсов и генератора тестовой последовательности и выходом компаратора,вход которого подключен ко входу устройс;гва (2(.

Недостатки этого устройства состоят в том, что оно обеспечивает тЬлько выявление дефектных ячеек запоминающего устройства, но не определяет причины их неправильной работы, а также не обеспечивает точной локализации неисправностей, что ограничивает область применения этого устройства.

Цель изобретения — расширение области применения устройств для контроля полупроводниковой памяти за счет обеспечения возможности проведения диагностических испытаний.

Поставленная цель достигается тем, что устройство содержит преобразователь кодов, адресный мультиплексор, счетчик, первый и второй накопители, причем выходы генератора тестовой последовательности подключены соответственно ко входу преобразователя кодов и первому »»ййвй;-:» -:.!.Ф! "

» =1»»НМА»й»4 "»Ы ».1.-»

3 " -" 74988 7 входу адресного мультиплексора, второй вход Устройство работает с которого подключен к выходу счетчика, выходы В начале испытания с преобразователя кодов соединены со вторыми поступает сигнал установ входами блока согласования уровней и управ- ние генератора 2 тестово ляющими входами компаратора и второго на- и счетчика 10 а первый

» копителя, выходы адресного мультиплексора полняется нулями, Зате подключены к адресным входам накопителей тор 1 тактовых импульс и третьим входам блока согласования уровней вой последовательности

) выходы которого соединены с выходами устрой- товых импульсов от ген ства, выход компаратора подключен к одному 10 батывать последовательно из входов первого накопителя, выход которо- ствий из исходной тесто го соединен с одним из входов блока управ- которые состоят из сиги ления, управляющие входы преобразователя налов адресации. Сигналь кодов, адресного мультиплексора, счетчика . образования передаются и накопителей подключены к другим выходам 15 кодов на входы блока блока управления.. Сигналы адресации перед

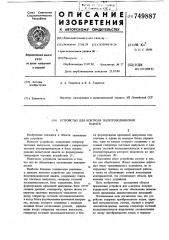

На чертеже изображена блок-схема предла- адресный мультиплексор гаемого устройства. ствии с сигналами време

Устройство содержит генератор 1 тактовых мируемыми блоком 4 п импульсов, генератор 2 тестовой последоЪатель- zp импульсов от генератора ности, блок 3 управления, блок 4 формирования управления и сигналы адр временной диаграммы, блок 5 согласования уров- туемого блока полупров ней, компаратор 6, вход 7 которого является Если действующее тест входом устройства, преобразователь 8 кодов, адрес- ся операцией считывания, ный мультиплексор 9, счетчик 10, первый 11 Z5 нивает значение реакции и второй 12 накопители. памяти с требуемой реак

Устройство подключается к блоку 13 полупро- жения несоответствия на водниковой памяти. Выход генератора 1 такто- 6 появляется сигнал "1" вых импульсов подключен ко входу генератора на информационный вход

2 тестовой последовательности и входу блока блок 3 управления кото зо

Э

4 формирования временной диаграммы, вы- генератора 1, фиксирует ходами соединенного с первыми входами блока ствия и вырабатывает им

5 согласования уровней. Управляющие входы копитель I I по адресу с генератора 1, генератора 2 и блока 4 подклю- фиксируя ее адрес. Одно чены к одним из выходов блока 3 управления, мирует цикл. восстановле

35 входы которого соединены с выходами генера- ячейки памяти, При этом торов 1 и 2, с выходами компаратора 6 и вы- кодов под действием сиг ходом накопителя 11. Выходы генератора 2 образует сигналы управле тестовой последовательности подключены соот- момент представляют one ветстветпю ко входу преобразователя 8 кодов сигналы, соответствующие

40 и первому входу адресного мультиплексора 9. или "1", в зависимости

Выходы преобразователя 8 кодов соединены со буемую реакцию формир вторыми входами блока 5 согласования уровней преобразователь 8 кодов. с управляющими входами компаратора 6 и - импульса от блока 3 упр накопителя 12, а выходы мультиплексора 9

45 очередной цикл временно подключены к адресным входам накопителей ветствии с которой блок

11 и и 12 и к третьим входам блока 5, выходы испытуемого блока полуп которого соединены с выходами устройства. новое значение п ав

Вход 7 компаратора 6 является входом

50 устроиства и соединен с выходом контролиру1 емого блока 13 памяти, а выход компаратора

6 подключен к одному из входов накопителя

11. У1правляющие входы преобразователя 8

" кодов, адресного мультиплексора 9, счетчика

10, накопителей 11 и 12 подключены к другим выходам блока 3 управления. Выход счетчика 10 соединен со вторым входом адресного мультиплексора. 9. ледующим образом, блока 3 управления ки в исходное состояй последовательности накопитель 11 зам запускается генераов. Генератор 2 тестопод действием так-, ератора 1 начинает вырасть тестовых воздейвой последовательности, алов управления и сиг управления без пречерез преобразователь 8

5 согласования уровней. аются на блок 5 через

9. Блок 5 в соответнной развертки, фор- од действием тактовых

1, передает сигналы есации на входы испыодниковой памяти. овое воздействие являет. компаратор 6 сравконтролируемого блока цией. В случае обнарувыходе компаратора, который поступает накопителя 11 и в рый запрещает работу появление несоответпульс записи "1" в набойной ячейки памяти, временно блок 3 форния состояния сбойной преобразователь 8 налов с блока 3 прения, которые в этот рацию считывания, в операции записи "0" от того, какую треует в данный момент

Блок 4 под действием авления формирует и развертки, в соот5 передает на входы роводниковой памяти у р ляющих сигналов. Сигналы адресации не изменяются. После этого блок 3, управления разрешает работу генератора 1, который запускает генератор 2, вырабатывающий очередные тестовые воздействия, и процесс повторяется до окончания исходной тестовой последовательности, при окончании которой генератор 2 вырабатывает соответствующий сигнал, который поступает в блок 3 управления, Блок 3 в этом случае запрещает работу генератора 1 и проверяет условие: ,был ли хотя бы один сбой при испытании

5 749887 на жюднУю тестовУю последоватЕль«ность. генератор 2 вырабатывает первое тестовое

Если сбоев зафиксировано не было, делается воздействие, Адресный мультиплексор 9 под заключение о годности испытуемого блока . действием сигнала управления с блока 3 передает на свой выход сигналы адресации один сбой имел место, что зафиксировано 5 с выхода генератора 2. Блок 4 под действием в блоке 3 управления, осуществляется пере-" тактового импульса от генератора 1 формиход на -диагностический этап, который начн- рует цикл временной развертки, под действием нается с опроса накопителя 11 для выявле- которой блок 5 передает тестовое воздействие ния адреса первой "сбойной" ячейки. Для этого на входы испытуемого блока памяти. Затем блок 3 управления последовательно изменяет . 1р под действием второго тактового импульса с состояние счетчика 10, с выхода которого генератора 1 блок 3 управления переключает сигналы передаются адресным мультиплексором адресный мультиплексор 9 на передачу сигналов

9 на адресные входы накопителя 11, При каж- с выхода сгетчика 10. Одновременно под дейдом изменении состояния счетчика под действием ствием сигналов с блока 3 управления преобрасигнала с блока 3 управления производится счи15 зователь 8 кодов преобразует управляющую . тывание информации из ячейки памяти нако- часть тестового воздействия, поступающую с пителя 11 с адресом, соответствующим состоя- выходов генератора 2, в новое тестовое воздейнию счетчика 10. Блок 3 каждый раз анали- ствие, соответствующее операции считывания, зирует состояние на выходе накопителя 11 и, а блок 4 под действием тактового импульса если считываемая информация "0", опрос его эр с генератора 1 формирует очередной цикл продолжается, а и считывании "1" ол временнои развертки, под действием которой прекращается. Счетчик 10 фиксирует значение блок 5 передает тестовое воздействие с выхо *сбойной" ячейки памяти. Затем блок 3 управ- дов преобразователя кодов 8 и адресного ления для определения работоспособности этой мультиплексора 9 на испытуемый блок памяти. ячейки памяти вырабатывает последовательность д5 Генератор 2 при этом продолжает выдавать преиз пяти импульсов, которые поступают" на дыдущее тестовое- воздействие. вход блока 4 формирования временной диаграм- Компаратор сравнивает значение реакции мы и вход преобразователя 8, который в сост- контролируемого блока памяти с требуемой

t ветствии с этими импульсами последовательно которая формируется преобразователем кодов вырабатывает сигналы, соответствующие опера-" Зр 8 под действием сигналов с блока 3 управлециям: зались "0", запись "1", считывание "1", ния. При обнаружении несоответствия блок 3 запись "0" и считывание "0". Адресный мульти- запрещает работу генератора 1, формирует имплексор 9 продолжает передавать значение адре- пульс записи и записывает в накоййтель 12 са с выходов счетчика 10. В случае обнаружения значение тестового воздействия, которое в несоответствия компаратором 6, блок 3 фор35 данный момент подавалось на испытуемый мирует импульсы записи во второй накопитель блок памяти. Затем преобразователь 8 и адрес12 значения анализирующего тестового воз- ный мультиплексор 9 под действием сигнала с деиствия, на котором было обнаружено несоот- блока 3 начинают передавать на свои выходы ветствие, и значения предшествующего аналйзу значение тестового воздействия, формируемого тестового воздействия. Затем блок 3 возобнов- 4р генератором 2. ляет опрос первого накопителя 11. Если несоот-, Значение этого тестового воздействия под ветствия требуемой реакции обнаружено не действием импульса записи от блока 3 запибыло, блок 3 управления вырабатывает сигнал сывается накопителем 12. После этого блок 3 плат «1 записи 0 в первыи накопитель 11 по адресу формирует цикл восстановления состояния соответствующему состоянию счетчика 10. 45 сбойной ячейки памяти, после чего разрешаетПосле этого начинается испытание на рас- работу генератора 1. Если тестовая последоширенную тестовую последовательность "сбой- вательность, генерируемая генератором 2, не ной" ячейки памяти, адрес которой зафик- закончена, он начинает вырабатывать очередное сирован счетчиком 10. тестовое воздеиствие, и изложенный выше проРежим и

50 ежим испытания на расширенную тестовую цесс испытания на расширенную тестовую попоследовательность отличается от режима- испы- следовательность повторяется до ее окончания. тания на исходную тем, что блок 3 управления После окончания тестовой последовательности устанавливает генератор 2 тестовой последователь- блок 3 возобновляет опрос накопителя 11, ности на режим работы, при котором он фор- и при считывании "1" начинаетсяпроверкарамирует очередное тестовое воздействие па каждо- ботоспособнасти очередной сбойной ячейки aa55 му нечетному тактовому импульсу, поступаю- мяти, а затем при Положительном исходе

Шему с генератора 1. Испытание начинается такой проверки начинается испытание íà расс запуска генератора 1 тактовых импульсов. ширенную тестовую последовательность для

Под действием первого тактового имп лъса " данной ячейки памяти. т

Такой процесс повторяется до завершения опроса накопителя 11. После испытания в накопителе 11 зафиксированы адреса }}еработоспс}собнь}х ячеек памяти, а в накопителе

12 зафиксированы тестовые воздействия, по

5 которым можно идентифицировать неисправнос }iN.

Технико-экономические преимущества описываемого устройства заключаются в том, что оно обеспечивает высокую точность и достоверность локализации неисправностей в блоках полупроводниковой памяти, в том числе локализацию многократных ошибок, получение диагностической информации в виде, не требу}ощем сложных вычислений, а также позволяет применять для диагностики неисправностей памяти простые тестовые последовательности и существенно сократить время локализации неисправностей без вмешательства оператора . в процесс контроля, Применение описываемого устройства позволяет полностью автоматизировать контроль блоков полупроводниковой памяти и использовать диагностическую информацию для корректировки технологического процесса изготовления полу- проводниковой памяти с целью повышения ее надежности, что существенно расширяет область применения устройств.

Устройство для контроля полупроводниковой памяти, содержащее генератор тактовых импульсов, генератор тестовой последовательности, блок

35 управления, блок формирования временной диаграммы, блок согласования уровней, компаратор, причем выход генератора тактовых импульсов подключен ко входу генератора тестовой последовательности и входу блока формирова40 ния временной диаграммы, выходы которого

Формула изобрeòåíèÿ

749887 соединены с первыми входами блока согласо,вания уровней, управляюшие входы генератора тактовых импульсов, генератора тестовой последовательности и блока формирования временной диаграммы подключены к одним из выходов блока управления, одни из входов которого соединены с выходами генератора тактовых импульсов и генератора тестовой последовательности и выходом компаратора, вход которого подключен ко входу устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства за счет обеспечения возможности проведения диагностических испытаний, оно содержит преобразователь кодов, адресный мультиплексор, счетчик, первый и второй накопители, причем выходы генератора тестовой последовательности подключены соответственно ко входу преобразователя кодов и первому входу адресного мультиплексора, второй вход которого подключен к выходу счетчика, выходы преобразователя кодов соединены со вторыми входами блока согласования уровней и управляющими входами компаратора и второго накопителя, выходы адресного мультиплексора подключены к адресным входам накопителей и третьим входам блока согласования уровней, выходы которого соединены с выходами устройств, выход компаратора подключен к одному из входов первого накопителя, выход которого соединен с одним из входов блока управления, управляющие входы преобразователя кодов, адресного мультиплексора, счетчика и накопителей подключены к другим выходам блока упраления.

Источники информации, принятые во внимание при экспертизе

1. Патент США N 3719929, кл. 340 — 146, 1, 1974.

2. Патент США N 3806243, кл, 340 — 146,1, 1974 (прототип).

7498S7

Редактор М. Ликович

Заказ 4427/8 - Филиал ПЙП "Патент", г. -Ужгород, ул. Проектная, 4

Составитель Т. Зайцева

Техред М. Кузьма Корректор B. Сщпщка i

ФФ Щ1 Р

Тираж 662 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5