Устройство для испытания транзисторных матриц

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (и1750401 (61) Дополнительное:к авт. свид-ву Р 402835 (я)м. к .з (22) Заявлено 26.06.78 (21) 2634252/18-25

Q 01 R 31/26 с присоединением заявки №

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 2 30 780. бюллетень ¹ 2 7 (>>) УДК 621. 382. .. 3 (088. 8) Дата опубликования описания 250780 (72) Автор изобретения

О. В. ПетухОв (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ ИСПЫТАНИЯ ТРАНЗИСТОРНЫХ

МАТРИЦ

Изобретение относится к области контроля полупроводниковых приборов и может быть испольэовано для электротермотренировки и испытаний на надежность при производстве полупроводниковых приборов.

Известно устройство для испытания транзисторных матриц, содержащее блоки задания режима, управления, питания, коммутации, пульт управления, измеритель параметров матриц, генератор импульсов, блок формирования тактов, распределитель импульсов, счетчик, соединенные между собой определенным 15 образом (11 .

Однако возможны сбои устройства тица записи ложных "1" в распределитель импульсов, в результате чего повышается рассеиваемая мощность на матрицах, что может привести к выходу их из строя. кроме того, возможны сбои устройства типа потери "1". что приводит к простою оборудования.

В связи с одновременностью работы контрольно-испытательного оборудования, мощных испытательных камер при производстве полупроводниковых приборов, вероятность укаэанных сбоев высока °

Целью изобретения является повышение эффективности устройства. указанная цель достигается тем, что в устройство для испытания транзисторных матриц введены многовходовая схема совпадения, интегрирующая цепь и генератор одиночных импульсов, причем входы схемы совпадения соединены с выходам распределителя импульсов, а выход — через интегрирующую цепь с одним из входов генератора одиночных импульсов, второй вход которого соединен с блоком формирования тактов, а выход — со счетчиком.

Такая схема устройства позволяет повысить его эффективность за счет ° восстановления правильной работы устройства в случае его сбоев. При этом, если в распределитель импульсов вписались ложные "1", многовходовая схема совпадения выдает разрешение на вход генератора одиночных импульсов и далее на пуск счетчика, а затем распределителя только после установки распределителя в состояние "0".

Аналогично при сбое, выражающемся в потере "1",осуществляется пуск счетчика, а затем распределителя импуль750401 сов, и начинается новый, исправленный цикл работы устройства.

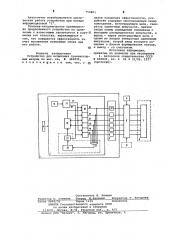

Блок-схема устройства для испытания транзисторных матриц представлена на чертеже.

Устройство содержит стойку испы,тательного режима 1, блок управления 2, блок задания режима 3, блок питания 4, блок коммутации 5, пульт управления 6, панель с транзисторными матрицами 7, измеритель параметров матриц 8, испытательную камеру 9, выходы 10-15 блока. управления, генератор Импульсов 16, блок формирования тактов 17, распределитель импульсов 18, счетчик 19, усилитель 20, многовходовую схему совпадения 21, интегрирующую цепь 22 и генератор оди ночных импульсов 23.

Устройство работает следующим образом.

Прямоугольные импульсы с генерато- 20 ра импульсов 16 поступают на вход блока формирования тактов 17, на выходах которого формируется двухтактная последовательность импульсов "1Т" и

"2Т" с периодами 2Т„ н (Т„ н- пеРиод 5 следования импульсов генератора 16).

Одновременно по сигналу "пуск" на выходе счетчика 19 в момент времени

"2Т" появляется одиночный импульс, который переключает в состояние "1" триггер первого разряда распределителя импульсов 18. На выходе 10 этого разряда формируется передний фронт испытательного импульса. Тактовый импульс "1T" устанавливает триггер первого разряда распределителя импульсов в состояние "0", а триггер второго разряда — в состояние "1".

В результате на выходе 10 формируется задний фронт испытательного импульса, а на выходе 11 — передний 40 фронт следующего испытательного импульса.

Длительность сформированного на выходе 10 импульса равна Т„„ Аналогично формируются дах 11-15, с которых эти импульсы по отдельным каналам поступают на соответствующие этим выходам матрицые

По окончании Формирования на вы- О ходах 10-15 распределителя импульсов ,длительностью Т„ „ все разряды устанавливаются в состояние "0", срабатывает многовходовая схема совпадения 21, и сигнал через интегрирующую цепь 22 поступает на вход генератора одиночных импульсов 23. Этот генератор формирует одиночный сигнал в момент времени "2Т", по которому запускается и начинает заполняться импульсами "1Т" счетчик 19. Импульс QQ переполнения в момент времени "2Т" запирает вход этого счетчика и поступает на вход первого разряда распределителя импульсов. Начинается новый цикл работы блока управления 2.

Интегрирующая цепь 22 служит для устранения ложного срабатывания ге— нератора одиночных импульсов в моменты переключения разрядов распределителя импульсов.

Счетчик 19 выполняет функцию линии задержки, которая необходима для задания требуемой частоты следования испытательных импульсов.на каждом из выходов 10-15 распределителя импульсов, а также для обеспечения постоянства скважности испытательных импульсов при изменении их длительности.

Период следования импульсов на каждом из выходов 10-15 определяется выражением

Тген(m+ 2)+ .у а, где Т вЂ” йериод следования испытательных импульсов;

Т„р„- период следования импульсов генератора 16; время задержки, равное времени заполнения счетчика 19 импульсами "1Т" до переполнения;

m — количество выходов блока управления 2, равное количеству испытательных матриц.

Из блока управления сформированные по длительности и частоте импульсы поступают на входы усилителей 20 блока задания режима 3, где,формируются по амплитуде и производится коррекция их. Фронтов. Проходя далее через блок коммутации, импульсы поступают на панель с транзисторными матрицами.

Пульт управления и блок коммутации служат для поочередного подключения выводов транзисторных структур матриц к измерителю для измерения их параметров в процессе испытания.

При работе устройства могут возникать сбои устройства, например, во время переключения мощных потребителей (испытательных камер и другого контрольно-испытательного оборудования).

Эти сбои выражаются либо в записи ложных "1" (дополнительно к информационной "1") в распределитель импульсов, что приводит к повышению рассеиваемой мощности на матрицах и к выходу их из строя, либо в потере информационной "1". В этом случае оборудование простаивает, испытание (тренировка) матриц не производится.

Устранение указанных сбоев в устройстве с помощью многовходовой схемы совпадения 21, интегрирующей цепи 22 и генератора одиночных импульсов 23 осуществляется следующим образом.

В случае записи ложных "1" схема совпадения сработает только после

"очистки" распределителя импульсов и установки его в состояние "0". Далее сигнал "пуск" распределителя формируется по цепи — интегрирующая цепь, генератор одиночных импульсов, счетчик аналогично описанному.

750401

Составитель В. Немцев

Редактор 0. Стенина Техред М.Келемеш Кор ектор Г. Назарова

Заказ 4644/Зб Тираж 1019 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра ская наб. д. 4 5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Аналогично возобновляется циклическая работа устройства при потере информационной "1".

Технике-экоцомическое преимущество предложенного устройства по сравнению с известными заключается в улуч 5 шенин его качества, выражающееся в том, что повышается эффективность за, счет исключения возможных сбоев при

его работе.

Формула изобретения

Устройство для испытания транзисторных матриц по авт. св. 9 402835, о т л и ч. а ю щ е е с я тем, что, с д целью повышения эффективности, устройство содержит многовходовую схему совпадения, интегрирующую цепь, генератор одиночных импульсов, причем входы схемы совпадения соединены с выходами распределителя импульсов, а выход - череэ интегрирующую цепь с одним из входов генератора одиночных импульсов, второй вход которого соединен с блоком формирования тактов, а выход - со счетчиком.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 402835, кл. G 01 R 31/26, 1977 (протртип).