Преобразователь двоичного кода в троичный код 1,0,1

Иллюстрации

Показать всеРеферат

Союз Советскин

Социалистических

Республик

О П И C А Н И Е 750477

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свнд-ву (22) Заявлено 09.02.78 (21) 2578020/18 — 24 с присоединением заявки .% (23) Приоритет (51)М. Кл.

5.

G 06 F 5/02

Государственный комитет

СССР.Ilo делам изобретений и открытий

Опубликовано 23.07.80. Бюллетень М 27 (53) УДК

<681325 (088.8) Дата опубликования описания 2З 07 80 (72) Авторы изобретения

Ф. Ф. Мннгалеев и Н. Т. Пластун (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ТРОИЧНЫЙ

КОД 1,0,1

Изобретение относится к вычислительной технике, предназначено для уплотнения информации за счет троичного кодирования чисел и может быть использовано для зкономии количества связей между цифровыми блоками вычислительной системы.

Известен преобразователь двоичного кода в троичный код 1, О, 1, содержащий двоичный регистр сдвига с дополнительным разрядом, элемент дифференцирования и диоды (1) .

l0

Недостаток этого преобразователя — низкое быстродействие, вызванное последовательным принципом преобразования.

Наиболее близким по технической сущности и схемному решению является преобразователь двоичного кода в троичный код 1, О, 1, содержащий троичные элементы, причем первая входная шина преобразователя соединена с входом отрицательного сигнала первого троичного элемента и первым входом положительного сигнала второго троичного элемента, вторая входная шина преобразователя соединена с входом положительного сигнала первого троичного элемента, третья входная шина

2 соединена со входом положительного сигнала третьего трончного элемента, выход первого троичного элемента соединен с входами отрицательного сигнала четвертого и пятого троичных элементов, выход пятого троичного элемента соединен с первым и вторым входами отрицательного сигнала шестого троичного элемента. Кроме того, данный преобразователь содержит еще три троичных элемента (21.

Недостаток известного преобразователя— относительно большой объем аппаратуры.

Цель изобретения — упрощение преобразователя.

Это достигается за счет того, что в нем третья входная шина соединена со вторым входом положительного сигнала и первым входом отрицательного сигнала второго троичного элемента, вторая входная шина соединена со входом отрицательного сигнала третьего троичного элемента и вторым входом отрицательного сигнала второго троичного элемента, выход которого соединен со входами положительного сигнала четвертого и

750477

Т аблица 1

4 Выход

О 0. +1

0 0 +1

О

+1 0 -1

0 +1 -1

О О +1

+1 0 О

+i +1

+1 О О

О +1 О

О "1 0

О

+1 О +1

О +1 - 1

3 пятого троичных элементов, выходы которых соответственно соединены с первыми входами положительного сигнала шестого и седьмого троичных элементов, выход третьего троичного элемента соединен со вторым входом положительного и первым входом отрицательного сигнала седьмого троичного элемента, выход четвертого троичного элемента соединен со вторым входом положительного сигнала шестого троичного элемента и вторым входом отрицательного сигнала седьмого .троичного элемента.

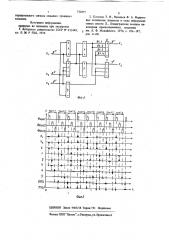

На фиг. 1 представлена блок-схема трехступенчатого преобразователя двоичного кода в троичный код 1, О, 1; на фиг. 2 приведена временная диаграмма работы преобразователя.

Первую ступень преобразователя составляют первый, второй и третий троичные элементы

1 — 3, вторую ступень — четвертый и пятый троичные элементы 4, 5. Третья ступень преобразователя состоит из шестого и седьмого троичных элементов 6, 7.

Троичные элементы реализуют троичные операции, описываемые табл. 1.

25 зо

4

Указанные операции образуют функционально полную систему логических функций и могут быть реализованы, например, при помощи ферритовых логических элементов.

Первая входная шина Х < соединена с входом отрицательного сигнала первого троичного элемента 1 и с первым входом положительного сигнала второго элемента 2. Вторая входная шина Х соединена с входом положительного сигнала первого троичного элемента 1 и с входами отрицательных сигналов второго 2 и третьего 3 троичных элементов.

Третья входная шина Х соединена с входами положительного и отрицательного сигналов второго 2 и с входом положительного сигнала третьего 3 троичных, элементов. Выход первого 1 троичного элемента соединен с входами отрицательных сигналов четвертого 4 и пятого 5 троичных элементов. Выход второго 2 троичного элемента соединен с входами положительных сигналов четвертого 4 и пятого 5 троичных элементов. Выход четвертого 4 троичного элемента соединен с первым и вторым входами положительного сигнала шестого 6 и с входом отрицательных сигналов седьмого 7 троичных элементов.

Выход пятого 5 троичного элемента соединен с первым и вторым входами отрицательного сигнала шестого 6 и с входом положительного сигнала седьмого 7 троичных элементов, Выход третьего 3 троичного элемента соединен со входами положительного и отрицательного сигналов седьмого 7 троичного элемента.

На входные шины Х вЂ” Х преобразова1 теля подаются кодовые комбинации в двоичной форме (по шине Х1 с естественным весом 2, по шине Х вЂ” 2, по Шине Х вЂ” 2 ), о 1 2 при этом на выходйых шинах Г1 и FZ преобразователя (на выходах элементов 6 и 7) появляются кодовые комбинации в троичной форме (по шиле Р1 с естественным весом 3, по шине V — 3 ), однозначно соответствующие входной комбинации сигналов. При подаче двоичного кода на шину Xg преобразователя "1 * представляется сигналом положительной полярности, а "0 — отсутствием сигнала. При подаче двоичного кода на шины Х2 и Х преобразователя 1" представляется сигналом положительной полярности, а "О" — сигналом отрицательной полярности.

+1 Ы1

+1

+1 +1

+1 *1 О

Система тактового питания схемы преобразователя трехфазная, при этом входная кодовая комбинация сигналов на шины Х вЂ” Х элементов 1 — 3 поступает через три фазы (один такт) передачи информации по элементам схемы (фиг. 2).

750477!

О !

Таблица 2

1!о и/п

25

ЗО

50

Иа фиг. 2 используются следующие условные обозначения, импульсы трехфазного источника питания считывание "0" запись "+1" считывание "+1" — запись "— 1" считывание "— 1"

Тактовым импульсом первой фазы считывается информация с троичных элементов б и 7, второй фазы — троичных элементов

1 — 3, а третьей фазы — с троичных элементов 4 и 5. Импульсы поступают на шины

Х1 — Х элементов 1 — 3 во время тактового

% импульса первой фазы.

Информация из трех двоичных разрядов переводится в два троичных разряда согласно табл. 2.

Функционирование преобразователя в соответствии с входной комбинацией (000) осуществляется следующим образом (временная диаграмма на фиг, 2).

Тактовым импульсом первой фазы первого такта согласно логике работы троичного элемента, записанной в табл. 1, отрицательный -.сигнал со входной шины Х преобразователя передается на вход отрицательного сигнала элемента 3, а со входной шины Х..! — на первый вход отрицательного сигнала элемента 2 и на вход положительного сигнала элемента 3; импульсом второй фазы отрицательньй сигнал с элемента 2 передается на вход положительного ситнала элемента 4; импульсом третьей фазы положительный сигнал с элемента 4 передается на вход положительного сигнала элемента 6.

Импульсом !!ервой фазы второго YAKTA no. ложительный сигнал с элемента б поступает на выход преобразователя, образуя выходную комбинацию (01), соответствующую входной комбинации (000) .

Аналогично происходят преобразования последующих входных комбинаций, при этом на выходах Г и V> сигналу положительной полярности соответствует код "1", а сигналу отрицательной полярности — код "1".

Использование предлагаемого преобразователя двоичного кода в троичный код 1, О, 1, обеспечивает по сравнению с известными техническими решениями упрощение преобразователя (сокращение объема аппаратуры преобразователя на 3 трончных элемента) и повышение надежности преобразователя.

Формула изобретения

Преобразователь двоичного кода в троичный код 1, О, 1, содержащий троичные элементы, причем первая входная шина преобразователя соединена с входом отрицательного сигнала первого троичного элемента и первым входом положительного сигнала второго троичного элемента, вторая входная шина преобразователя соединена с входом положительного сигнала первого троичного элемента, третья входная шина соединена со входом положительного сигнала третьего троичного элемента, выход первого троичного элемента соединен с входами отрицательного сигнала четвертого и пятого троичных элементов, выход пятого троичного элемента соединен с первым и вторым входами отрицательного сигнала шестого троичногоэлемента, отличающийся тем, что, с целью упрощения преобразователя, в нем третья входная шина соединена со вторым входом положительного Сигнала и первым входом отрицательного сигнала второго троичного элемента, вторая входная шина соединена со входом отрицательного сигнала третьего троичного элемента и вторым входом отрицательного сигнала второго троичного элемента, выход которого соединен со входами положительного сигнала четвертого и пятого троичных элементов, выходы которых соответственно соединены с первыми входами положительного сигнала шестого и седьмого троичных элементов, выход третьего троичиого элемента соединен со вторым входом положительного и первым входом отрицательного сигнала седьмого троичного элемента, выход четвертого троичного элемента соединен со вторым входом положительного сигнала шестого троичиого элемента и вторым входом

750477 отрицательного сигнала седьМого троичного элемента.

Источники информации, принятые во внимание при экспертизе Г, Авторское свидетельство СССР Р 411449, кл. 6 Об F 5/02, 1974. х, Фаза х, х

ЦНИИПИ Заказ 4465/18 Тираж 751 Подписное

Филиал ППП "Патент", г.Ужгород, ул. Проектная,4

6(Б) 1(Я

2. Соколов Т. H., Васильев Ф. А. Ферритовые логические элементы и узлы информационных систем Л,, Ленинградская военная инженерная .краснознаменная, академия им. А. Ф. Можайского, 1970, с. 186 — 187, рис. 4 — 60,