Преобразователь целых двоичнодесятичных чисел в двоичные

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик 1Ц750478 (61) Дополнительное к авт. свид-ву— (22) Заявлено 04.05.78 (21) 2610715/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) м. к1.

G 06 F 5/02

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681.325 (088,8) Опубликовано 23.07.80. Бюллетень №27

Дата опубликования описания 27.07.80 (72) Автор изобретения

В. И. Омельченко

Таганрогский радиотехнический институт им. В. Д. Kà tìüïîâà (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ЦЕЛЪ|Х

ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ В ДВОИЧНЫЕ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении устройств, осуществляющих двоично-десятичное преобразование информации.

Известен двоично-десятичный преобразователь, содержащий два регистра сдвига, блоки коррекции и блок управления (1).

Недостатком этого преобразователя является большой объем аппаратуры.

Наиболее близким по технической сущности к предлагаемому является преобразователь двоично-десятичного кода в двоичный, содержащий первый и второй регистры сдвига, первый сумматор, блок управления, четыре элемента И и первый элемент ИЛИ, первый вход которого соединен с выходом первого элемента И, выход первого элемента

ИЛИ соединен с первым входом первого сумматора, второй вход которого соединен с выходом второго элемента И, первый выход первого регистра сдвига соединен с первыми входами третьего и четвертого элементов И, выходы которых соединены соответственно с первым входом второго регистра сдвига и вторым входом первого элемента ИЛИ, первый и второй выходы второго регистра сдвига соединены соответственно с первыми входами первого и второго элементов И, первый выход блока управления соединен со вторыми входами первого и третьего элементов И, второй выход блока управления соединен со вторым входом четвертого элемента И, вторые выходы первого регистра сдвига соединены с выходными шинами преобразователя (2).

Недостатком этого устройства является относительно низкое быстродействие, свя1о занное с тем, что в каждом цикле в преобразование вовлекается только одна новая двоично-десятичная тетрада.

Цель изобретения — увеличение скорости преобразования.

Это достигается за счет того, что предлагаемый преобразователь содержит второй сумматор, коммутатор, блок памяти, пятый элемент И и второй элемент ИЛИ, входы которого соединены с первым и вторым выходами блока управления, а выход соединен со вторым входом второго элемента И, первый выход блока управления соединен с первым входом пятого элемента И, второй вход которого соединен с третьим выходом второго регистра сдвига, а выход соединен

750478

S 0

20 с первым входом второго сумматора, второй вход которого соединен с выходом первого сумматора, выход второго сумматора соединен со входом первого регистра сдвига, входы коммутатора соединены с информационными шинами преобразователя, выход коммутатора соединен с первым входом блока памяти, второй вход которого соединен с третьим выходом блока управления, а выход блока памяти соединен со вторым входом второго регистра сдвига.

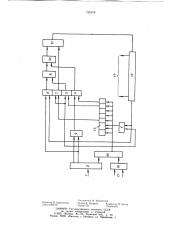

На чертеже представлена функциональная схема предлагаемого преобразователя.

Преобразователь содержит управляющую шину 1, блок 2 управления, первый, второй, третий, четвертый и пятый элементы 3 — 7 И, элементы 8 и 9 ИЛИ, сумматоры (двоичные) 10 и 11, регистры 12 и 13 сдвига, выходные шины 14, блок 15 памяти, коммутатор 16, информационные шины 17.

Управляющая шина 1 служит для поступления сигнала пуска на вход блока 2 управления, обеспечивающего работу всего устройства в целом. Первый выход блока 2 управляет передачей двоичного числа на этапе умножения и соединен с первыми входами первого 3, третьего 5 и пятого 7 элементов И. Выход первого элемента 3 И соединен с первым входом первого элемента 8 ИЛИ. Первый выход блока 2 управления соединен с первым входом второго элемента 9 ИЛИ. Второй выход блока 2 управления подключен к второму входу второго элемента 9 ИЛИ и к первому входу четвертого элемента 6 И и управляет суммированием на первом этапе преобразования в каждом цикле. Выход второго элемента 9

ИЛИ подключен к первому входу второго элемента 4 И, передающего информацию без сдвига на первом этапе и со сдвигом на шесть позиций в сторону старших разрядов на втором этапе каждого цикла. Выход первого элемента 8 ИЛИ соединен с первым входом первого двоичного сумматора 10 для суммирования с информацией, поступающей на его второй вход с выхода второго элемента 4 И. Информация с выхода первого двоичного сумматора 10 поступает на первый вход второго двоичного сумматора 11, суммируясь с информацией, поступающей на его второй вход с выхода пятого элемента 7 И. Выход второго двоичного сумматора 11 соединен с входом первого регистра 12 сдвига, обеспечивающего циркуляцию и хранение результатов суммирования. Первый и второй выходы первого регистра 12 сдвига соединены соответственно с выходными шинами 14 и вторыми входами третьего и четвертого элементов 5 и 6 И, обеспечивающих передачу входной информации без сдвига на первом этапе и со сдвигом на втором этапе. Выход третьего элемента 5 И соединен с первым входом второго регистра 13 сдвига, первый, второй и третий выходы которого выдают инфор35

4S

55 мацию, смещенную на шесть, пять и две позиции, и соответственно соединены с вторыми входами второго 4, первого 3 и пятого 7 элементов И. Третий выход блока 2 управления соединен с первым входом блока 15 памяти, второй вход которого соединен с выходом коммутатора 16, обеспечивающего чтение необходимого двоичного эквивалента.

Вход коммутатора 16 соединен с выходными шинами 17, обеспечивающими поступление очередной пары преобразующих тетрад.

Преобразование производится по схеме

Горнера в соответствии со следующим выражением:

А = ((Э1!100100 + Э )1100100 +

+....+ Э „,) 11OO1OO+ Э, где А — искомое двоичное число;

Э вЂ” двоичный эквивалент преобразуемой пары тетрад; — число пар тетрад, определяемое из соотноШения:

1. — число тетрад исходного числа.

Преобразование двоично-десятичного числа производится в следующей последовательности.

На коммутатор 16 по шинам 17 последовательно пара за парой (начиная со старшей пары) поступают тетрады преобразуемого двоично-десятичного числа. Одновременно на блок 2 управления по управляющей шине 1 поступает сигнал, запускающий все устройство в целом. Пусть преобразуется вторая пара тетрад, первый регистр 12 сдвига хранит результат преобразования первой пары в первом цикле. На коммутатор 16 параллельным кодом по шинам 17 поступает очередная пара преобразующих тетрад, код которой является адресом, по которому выбирается один из девяносто девяти двоичных эквивалентов (по числу комбинаций цифр двух десятичных разрядов от 01 до 99) из блока 15 памяти. Выбранный семиразрядный двоичный эквивалент поступает параллельным кодом во второй регистр 13 сдвига. Начинается первый этап второго цикла. Блок 2 управления выдает сигнал разрешения на второй и четвертый элемента 4 и 6 И. При этом содержимое первого и второго регистров 12 и 13 сдвига последовательным кодом поступает на первый и второй входы первого двоичного сумматора 10. Результат суммы поступает с выхода первого двоичного сумматора 10 на первый вход второго двоичного сумматора 11 и суммируется с нулем, поступающим на второй его вход, так как элемент 7 И закрыт.

С выхода второго сумматора 11 результат записывается на первый регистр 12 сдвига.

После этого начинается второй этап второго цикла, осуществляющий умножение на

1100100 (сто в двоичном коде). При этом четвертый элемент 6 И закрывается, а по750478 мимо второго элемента 4 И открываются первый 3, третий 5 и пятый 7 элементы И.

Содержимое первого регистра 12 сдвига поступает в шестой разряд второго двоичного регистра 13, который смещает информацию на две, пять и шесть позиций в сторону старших разрядов. Т. е. на втором этапе осуществляется умножение на сто косвенным путем. Результат умножения последовательным кодом поступает на первый регистр 12 сдвига, где хранится до следующего цикла.

Описанный процесс приема очередной преобразуемой пары тетрад, чтения соответствующего ей двоичного эквивалента, суммирования его с содержанием первого регистра 12 сдвига, умножения полученной суммы осуществляется еще j — 3 цикла. Последний цикл отличается от остальных циклов тем, что умножения на сто не производится. Съем двоичного числа производится с первого регистра 12 сдвига.

Предложенный преобразователь за счет умножения на сто вместо умножения на, десять и одновременной обработки двух тетрад позволяет в два раза IloBbIcHTb скорость преобразования.

Формула изобретения

Преобразователь целых двоично-десятичных чисел в двоичные, содержащий первый и второй регистры сдвига, первый сумматор, блок управления, четыре элемента И и первый элемент ИЛИ, первый вход которого соединен с выходом первого элемента И, выход первого элемента ИЛИ соединен с первым входом первого сумматора, второй вход которого соединен с выходом второго элемента И, первый выход первого регистра сдвига соединен с первыми входами третьего и четвертого элементов И, выходы которых соединены соответственно с первым входом второго регистра сдвига и вторым входом первого элемента ИЛИ, первый и второй выходы второго регистра сдвига соответственно соединены с первыми входами первого и второго элементов И, первый выход блока управления соединен со вторыми входами первого и третьего элементов И, второй выход блока управления соединен со вторым входом четвертого элемента И, вторые выходы первого регистра сдвига соединены с выходными шинами преобразователя, отличаюи1ийся тем, что, с целью увеличения скорости преобразования, он содержит второй сумматор, коммутатор, блок памяти, пятый элемент И и второй элемент ИЛИ, входы которого соединены с первым и вторым выходами блока управления, а выход соединен со вторым входом второго элемента И, первый выход блока управления соединен с первым входом пятого элемента И, 2Î второй вход которого соединен с третьим выходом второго регистра сдвига, а выход соединен с первым входом второго сумматора, второй вход которого соединен с выходом- первого Сумматора, выход второго

25 сумматора соединен со входом первого ре гистра сдвига, входы коммутатора соединены с информационными шинами преобразователя, выход коммутатора соединен с первым входом блока памяти, второй вход которого соединен с третьим выходом блока эо управления, а выход блока памяти соединен со вторым входом второго регистра сдвига.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 311474, кл. G 06 F 5/02, 1968.

2. Авторское свидетельство СССР № 329525, кл. G 06 F 5/02, 1969 (прототип).

750478

Составитель М. Аршавский

Редактор В. Зарванская Техред К. Шуфрич Корректор М. Коста

Заказ 4467/! 9 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

I 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент>, r. Ужгород, ул. Проектная, 4