Устройство для преобразования координат

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«»750491 (6! ) Дополнительное к авт. свид-ву(53)М. Кл.з

G 06 F 15/20 (22) Заявлено 04. 05. 78 (2t) 2610284/18-24 с присоединением заявки Йо— (23) Приоритет—

Государственный комитет

СССР но делам изобретениИ и открытий

Опубликовано 2 30780. Q j Aeтеиь Н 27 (53) УДК 681. 325 (088.8) Дата опубликования описания 250780

{72) Авторы изобретения

M. Ю. Кляшторный, Б. Х. Красницкий и В. Г. Петров (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ

Изобретение относится к области автоматики и вычислительной техники, а именно к цифровым преобразователям координат и может быть использовано в качестве вычислителя, входящего в состав астронавигационных систем.

Известно устройство, содержащее блок управления, сумматоры, сдвигающие регистры )1)

Недостатком известного устройства является низкое быстродействие.

Наиболее близким по сущности техническим решением задачи является устройство, содержащее блок управления, коммутатор, реверсивные счетчики, сумматоры (23

Недостатком известного устройства является недостаточное быстродействие.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что з устройство для преобразо- gg вания координат, содержащее первый, второй и третий сумматоры, выходы которых соединены с первыми входами одноименных реверсивных счетчиков, блок управления, первый коммутатор, память, введены дешифратор, формирователь, регистр аргумента, второй коммутатор, блок коммутаторов, три сумматора по модулю два, элемент

НЕ, причем выход блока управления соединен со входами формирователя и дешифратора, первый выход дешифратора соединен с первым входом регистра аргумента, первый выход которого соединен со входом элемента

НЕ и первым входом первого сумматора по модулю два, выход которого соединен с первыми входами второго и третьего сумматоров по модулю два, остальные выходы дешифратора и выходы формирователя соединены со входами второго коммутатора, первый, второй и третий выходы. которого соединены с управляющими входами первого, второго и третьего сумматоров, четвертый выход второго коммутатора соединен с управляющими входами памяти, блока коммутаторов и регистра аргумента, второй выход которого соединен со вторым входом первого сумматора по модулю два, группа выхо.дов второго коммутатора соединена с первыми группами входов памяти, пер вого коммутатора и блока коммутато750491

lI т

1У

0 0

0 1

1 0

1 1 ров, втора.я группа входов которого соединена с выходами элемента НЕ, первого, второго и третьего сумматоров по модулю два и первым выходам регистра аргумента, группа выходов блока коммутаторов соединена со второй группой входов памяти, выходы которой соединены с второй группой входов первого коммутатора, первый и второй выходы которого соединены со вторыми входами соответственно второго и третьего сумматоров по модулю 10 два и первый выход блока коммутаторов соединен с первым входом первого сумматора и вторым входом первого реверсивного счетчика, второй выход блока коммутаторов соеди-. нен с первым входом второго сумматора и вторым входом второго реверсивного счетчика, третий выход блока коммутаторов соединен с первым входом третьего сумматора и вторым входом третьего реверсивного счетчика, второй и третий входы первого сумматора соединены с первыми выходами соответственно второго и третьего реверсивных счетчиков, второй и третий входы второго сумматора соединены соответственно с первым выходом nepBQFo реверсивного счетчика и вторым выходом третьего реверсивного счетчика, второй и третий входы третьего сумматора соединены со вторыми выхо- 30 дами соответственно первого и второго реверсивных счетчиков.

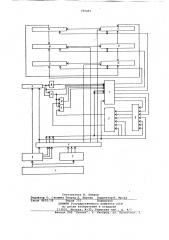

Блок-схема. устройства приведена на чертеже.

Устройство содержит бпок 1 управ- 35 ления, формирователь 2, дешифратор 3, регистр 4 аргумента, коммутаторы

5 и 6, блок 7 коммутаторов, память

8 сумматоры 9-11 по модулю два, реверсивные счетчики 12-14 сумматоры

15-17, элемент НЕ 18.

Устройство работает следующим образом

Предварительно в реверсивные счетчики 12- 14 устанавливаются значения проекций единичного радиуса-вектора в исходной системе координат. Затем последовательно согласно программе работы, задаваемой блоком 1, формирователем 2 и дешифратором З,осуществляются заданные преобразования ка- 50 ординат.

Пусть, например, первый поворот системы координат необходимо осуществить вокруг оси на заданный угол, превышающий по величине, Р

55 два квадранта. Код квадранта в этом случае будет соответствовать следующим значениям разрядов: а=0,а=1...

Г что видно из таблицы:

Номер к та

Первым тактом значение аргумента передается с дешифратора 3 в регистр

4. Бо втором такте определяются значения логических функций

«=0 « pp, 1 у,=О (a „= <,а„, -о ;1„„=о,„= для чего код квадранта передается из памяти 8 через коммутатор 5 в сумматоры 9-11 и с помощью сигнала, поступившего с коммутатора 6, согласно полученным результатам корректируются знаки начальных значений проекций на оси и ;

При этом изменяются знаки в реверсивных счетчиках 12, 14 и в сумматоре 17, поскольку возбуждается соответствующий выход блока 7, Таким образом, заканчиваются все подготовительные операции, в результате которых получены значения проекций во вспомогательной системе координат, повернутой относительно исходной на 180о, и начинается непосредственно выполнение "преобразование координат".

В последующие моменты времени синхранизирующие импульсы из коммутатора б поступают на регистр 4 для преобразования величины, записанной в нем в параллельном коде, в унитарный код путем списывания ее значения до нуля, и на управляющие входы сумматоров 15, 17.

Схема, состоящая из реверсивных счетчиков 12, 14 и сумматоров 15, 17, которые связаны между собой указанным образом, причем знак переполнения одного йз сумматоров инвертируется, описывается следующим соотношением:

«т м кп > у

«р

«т

«т, где В,, R — значения проекций радиуса-вектора на

m такте, R R > „, - значения проекций

Х н4 У и радиуса-вектора на я+1 такте после поворота исходной системы координат на элементарный угол поворота, определяемый единицей младшего разряда цифровых интеграторов 2

Приведенное соотношение описывает преобразование координат на плоскости — поворот исходной системы координат на угол 2 рад.

Следовательно, после поступления в регистр 4 числа импульсов, соответствующего заданному углу поворота о, в реверсивных счетчиках 12, 14 образуются новые числа, пропорцио750491 нальные величинам проекций радиусавектора в новой системе координат (Х, У ), а в реверсивном счетчике 13 число не изменяется.

Сигнал, поступивший из регистра 4, прекратит выдачу импульсов с выхода 5 блока 7. Это преобразование соответствует повороту пространственной системы координат вокруг оси q на заданный угол. Следующий поворот может быть произведен вокруг оси

Получаемое в устройстве сокращение длительности операции "преобра. зование координат" позволяет в четыре раза уменьшить потребляемую мощность за счет соответствующего снижения рабочей частоты.

Например, для цифрового преобразователя координат на 500 корпусах интегральных микросхем 133 серии требуется дополнительно затратить 70 корпусов, но снижение тактовой частоты в четыре раза благодаря вве— дению регистра аргумента и комбинационного блока уменьшает потребляемую мощность с 25 Вт до 7,1 Вт (средняя потребляемая динамическая мощност М на один корпус составляет 50 мВт).

При этом количество унифицированных стабилизаторов на 5 Вт снижается с

5 штук до 2, а при весе каждого стабилизатора 300 г экономия в массе 30 составляет 1,1 кг.

За время эксплуатации самолета (10-15 лет) 1 кг веса в стоимостном выражении составляет около 2 млн.руб.

Следовательно, экономический эф- 35 фект от снижения веса вычислителя за время его эксплуатации составляет около 2,2 млн. руб.

Формула изобретения

Устройство для преобразования координат, содержащее первый, второй и третий сумматоры, выходы которых соединены с первыми входами одноимен-. ных реверсивных счетчиков, блок управления, первый коммутатор, память, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия в него введены дешифратор, формирователь, регистр аргумента, второй коммутатор, блок коммутаторов, три сумматора по модулю два, элемента НЕ, причем, выход блока управления соединен со входами формирователя и дешифратора, первый выход дешифратора соединен с первым входом регистра аргумента, первый выход которого соединен со входом элемента НЕ и первым входом первого сумматора по модулю два, выход которого соедияен с первыми входами второго и третьего сумматоров по модулю два, остальные выходы дешифратора и выходы формирователя соединены со входами второго коммутатора, первый, второй и третий выходы которого соединены с управляющими входами первого, второго и третьего сумматоров, четвертый выход второго коммутатора соединен с управляющими входами памяти, блока Коммутаторов и регистра аргумента, второй выход которого соединен со вторым входом первого сумматора по модулю два, группа выходов второго коммутатора соединена с первыми группами входов памяти, первого коммутатора и блока коммутаторов, вторая группа входов которо. го соединена с выходами элемента НЕ, первого, второго и третьего сумматоров по модулю два и первым выходом регистра аргумента, группа выходов блока коммутаторов, соединена со второй группой входов памяти, выходы которой соединены со второй группой входов первого коммутатора, первый и второй выходы которого соединены со вторыми входами соответственно второго и третьего сумматоров по модулю два, первый выход блока коммутаторов соединен с первым входом первого сум матора и вторым входом первого ревер сивного счетчика, второй выход блока коммутаторов соединен с первым входом второго сумматора и вторым входом второго реверсивного счетчика третий выход блока коммутаторов соединен с первым входом третьего сумматора и вторым входом третьего реверсивного счетчика, второй и третий входы первого сумматора соединены с первыми выходами соответственно второго и третьего реверсивных счетчиков, второй и третий входы второго сумматора соединены соответственно с первым выходом первого реверсивного счетчика и вторым выходом третьего реверсивного счетчика, второй и третий входы третьего сумматора соединены со вторыми выходами соответственно первого и второго реверсивных счетчиков.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 591860, кл. G 06 F 15/20, 1976.

2. Авторское свидетельство СССР

9568947, кл G 06 F 15/20, 1974 (прототип).

750491

Заказ 4650/38

Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Раушская наб., д. 4 /5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Составитель В. Петров

Редактор О. Стенина Техред Я. Би чак КорректорИ. Муска