Устройство для сложения сигналов в системе остаточных классов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

«»750504 (61) Дополнительное к авт. свид-ву— (22) Заявлено13. 02. 78 (21) 257961б/18-24 с присоединением заявки Нов (23) Приоритет—

Опубликовано23.0780. Бюллетень 14о27

Дата опубликования описани я25.07.80 (51)М К 3

06 q 7/14

Государственный комитет

СССР по делам изобретений и отнрыти и (53) УДК Ь81. 338 (088. 8) (72) Авторы изобретения

М. В. Синьков, А. И. Закидальский, Н. Б. Нифонтов и М. Н. Рогов (71) Заявитель (5 4 ) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ СИГНАЛОВ

В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ

Изобретение относится к вычислительной технике и дискретной авто матике и может быть использовано в устройствах математического моделиро- вания для сложения сигналов.

Известные устройства для сложения сигналов, выполненные на операционных усилителях не могут быть использованы для сложения в системе остаточных классов 11) Наиболее близким по технической сущности к предложенному является устройство для сложения сигналов в системе остаточных классов, содержащее дифференциальный усилитель, неинвертирующий вход которого через первый и второй масштабные резисторы соединен с источниками входных сигналов а инвертирующий вход диффе- 2{ ренциального усилителя через третий масштабный резистор подключен к era выходу, четвертый масштабный резистор, один вывод которого подключен к инвертирующему входу дифференциаль- 25 ного усилителя, и источники напряжения (2)

Недостатком данного устройства

=ложения в системе остаточных классов является то, что входные сиг- Зп.,налы могут принимать максимальные

I з начения, не превышающие полови ну динамического диапазона выходного напряжения в узле и недостаточное быстродействие из-за задержки выполнения операций на время переходного процесса.

Цель изобретения — повышение быстродействия и расширение динамического диапазона входных сигналов.

Это достигается тем, что в устройство введены компаратор и ключи, выходы которых соединены со вторым выводом четвертого масштабного резистора, вход первого ключа подключен к первому источнику напряжения, вход второго ключа соединен с шиной нулевого потенциала, управляющие входы ключей связаны с выходом компаратора, первый вход которого соединен со вторым источником напряжения, а второй вход подключен к неинвертирующему входу дифференциального усилителя.

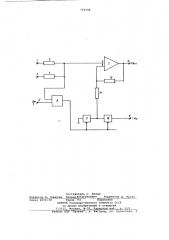

На чертеже представлена блок-схема устройства.

Устройство для сложения сигналов в системе остаточных классов содержит источник 1 и 2 входных сигналов И„и

750504

Ил соответственно, первый масштабный резистор 3, второй масштабный резистор

4„ неинвертирующий 5 и инвертирующий

6 входы дифференциального усилителя

7, компаратор 8, ключи 9 и 10, источники напряжения 11 и 12„ третий .масштабный резистор 13, четвертый масштабный резистор 14, выход 15 дифференциального усилителя. Входные сигналы от источников 1 и 2 суммируются на масштабных резисторах 3 и 4 и 1О поступают на неинвертирующий вход 5 дифференциального усилителя 7 и один иэ входов компаратора 8, ко нторому входу компаратора 8 подключен источник напряжения 12. Выход компаратора

8 соединен с управляющими входами ключей 9 и 10, подключающих инвертирующий вход 6 дифференциального усилителя 7 через резистор 14 или к шине нулевого потенциала, или к источнику напряжения 11. Результат суммирования снимается с выхода 15 дифференциального усилителя 7 и через масштабный резистор 13 подается на инвертирующий вход 6 дифференциального усилителя 7. 25

Устройство работает следующим образом. Входные сигналы Ц л и О от источников нходных сигналов 1 и 2 суммируются на резисторах 3 и 4. Результат суммирования подается на неинвертирующий вход 6 дифференциального уси лителя 7 и на один из входов компаратора 8. На второй вход компаратора подается сигнал u /2 от источника напряженияя 12, где Ц„„-напряже ние, пропорциональное модулю п. При равенстве резисторов 3 и 4 напряжение на входе усилителя 7 будет равно (0<+V>) /2, Таким образом, если (02 Н ) /2 меньше, чем U, /2, т.е.

0„0 Π— (— Х 2 то выходной сигнал компаратора 8 будет таким, что ключ 9 подключает резистор 14 к шине нулевого потенциала.

При этом ключ 10 разомкнут. На выходе

15 дифференциального усилителя 7 должно устанавливаться такое напряжение которое обеспечивает величину входных напряжений дифференциального усилителя 7,при котором удовлетворяется равенство

u„u„u„„„„„ л 4 л ),(л 55

%„Ag Й, R> где К, Р2, R, и й, - соответственно резисторов 3,4, 14 и 13

При В В й5 К4 К Оьь 0л ФО2

Если же сигнал на входе 5 усилителя 7 и компаратора 8 превышает Urn/2, то выходной сигнал компаратора 8 становится таким, что ключ 9 размыкается.

К резистору 14 подключается напряже- 65 ние U, . В этом случае выходное напряжение усилителя 7 станет таким, что, как и в предыдущем случае, будет обес— печено равенство входных сигналов усилителя 7.

В этом случае будет справедливо следующее соотношение из которого при равенстве сопротивлений R = R = Й, = к = к получаем л и,„=u„° о -U„

Устройство нашло применение в аналоговых и гибридных вычислительных блоках, использующих для представления информации непозиционную систему счисления в остаточных классах.

По данному техническому предложению на предприятии был изготовлен макет, который показал работоспособность данного устройства. Выполнение суммирования и сравнения на входе усилителя обеспечило повышение быстродействия и расширение динамического диапазона изменения входного напряжения. формула изобретения

Устройство для сложения сигналов в системе остаточных классов, содержащее дифференциальный усилитель, неинвертирующий вход которого через первый и второй масштабные резисторы соединен с источниками входных сигналов, а инвертирующий вход дифференциального усилителя через третий масштабный резистор подключен к его выходу, четвертый масштабный резистор, первы вый вывод которого подключен к инвертирующему входу дифференциального усилителя, и источники напряжения, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия и расширения динамического диапазона нходных сигналон, в него введены компаратор и ключи, выходы которых соединены со вторым выводом четвертого масштабного резистора, выход первого ключа подключен к первому источнику напряжения, вход второго ключа соединен с шиной нулевого потенциала, управляющие входы ключей связаны с выходом компаратора. первый вход которого соединен со вторым источником напряжения, а нторой вход подключен к неинвертирующему входу дифференциального усилителя.

Источники информации, принятые во внимание при экспертизе

1. Коган Б.Я.Электронные моделирующие устройства.Л.,физматлит,1959 с. 58-61.

2. Авторское свидетельство СССР

М 362312, кл. Сл 06 (л 7/12, 1973 (прототип).

750504

+и„

Составитель С. Белан

Редактор Л. Лашкова Техред Ж.Кастелевич Корректор И.

Закаэ 4650/38

Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035 Москва Ж-35 Раушская наб. д. 4 5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4