Делительное устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социвлистнческих

Республик

ОЛИСЛНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

С 06 G 7/16 с присоединением заявки ¹

Гасударственный кокнтет (23 ) П рноритет— по делам нзаоретеннй н открытий

Опубликовано 23.07.80. Бюллетень № 27 (53} УД1(681. .335(088.8}

Дата опубликования описания 23.07.80 (72) Автор изобретения

Т. Л. Метс

Тартуский филиал Государственного всесоюзного ордена

Труцового Красного Знамени научно-исследовательского технологического института ремонта и эксплуатации машинно-тракторного парка (7I ) Заявитель (54} ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к аналогоцифровой вычислительной технике и технике аналого-цифрового преобразования.

Известно устройство аналого-цифрового преобразования двойным интегрированием t lj.

В этом устройстве преобразование напряжения в КоН осушествляется путем двухтактового интегрирования

Нецостатком устройства является низ10 кая точность целения, обусловленная тем, что выходной сигнал зависит от длительности интервала интегрирования.

Наиболее близким техническим решением является устройство цля деления

5$ сигналов, содержашее цва ключа, интегратор, генератор интервала Времениэ компаратор, элемент И, генератор импульсов станцартной частоты, цифровой индикаторный блок и генератор тактовых импульсов (2).

Недостатком этого устройства также является невысокая точность деления, так кELK зависпмocть выходного сигналa от длительности интервала интегрирования в данном устройстве устранжтся за счет введения в устройство генератора цлительности интервала Г =- CQ

Целью изобретения является повышение точности целеиия путем исключения зависимости выходного сигнала от интервала интегрирования.

Поставленная цель достигается тем, что в целительное устройство, соцержашее первый ключ, первый вход которого является вхоцом делимого устройства, второй ключ, первый вход которого является вхоцом целителя устройства, первый интегратор, первый вход которого поцключен к выходу первого ключа, компаратор, один вхоц которого подключен к выходу интегратора, а другой вход к шине нулевого потенциала, триггер, вхоцкоторого подключен к выходу KQMTIBpoTopB, элемент И, первый ахоп которого подклют, Й!6 Г 2 () Й1 k (g z Ij 0 гце i (t) — ток заряда второго инUg(t)

Я к тегратора, 5 — среднее значение тока заряда второго интегра15 тора, R — входной масштабный ре!

Ь зистор второго интегратора.

В конце интервала интегрирования Т

20 на выходе второго интегратора будет напряжение

Э„° T„

„ унт 0 Jg ° Т

Д

Ф

< Ra с„ Р

50 з 7505 чен к выходу триггера, генератор импульсов стабильной частоты, выход которого подключен ко второму входу элемента И, вькод которого подключен ко входу цифрового индикаторного блока, генератор

5 тактовых импульсов, выхоцы которого поцключены к управляющим входам всех ключей, элемента И и цифрового индикаторного блока, дополнительно введены второй интегратор, в обратную связь которого включен ключ сброса, вход которого .подключен к выходу второго ключа, третий ключ, первый вход которого подключен к выходу второгоннтегратора, а выходко второму входу первого интегратора.

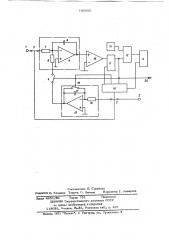

Блок-схема делительного устройства представлена на чертеже.

Устройство содержит вхоц 1 напряжения делимого, вход 2 напряжения делителя, ключи 3, 4 и 5, первый интегратор 6 с входными масштабными резисторами 7 и 8 и интегрирующим конденсатором 9,компаратор

10, триггер 1 1, элемент И 1 2, генератор 1 3 импульсов стабильной частоты, цифровой индикаторный блок 14, второй интегратор 15 с входным масштабным резистором 16, интегрирующим конденсатором

17 и ключом сброса 18, тактовый генератор 19, выхоц 20 интервала.

Устройство работает следующим образом.

В начальном состоянии выходные напряжения интеграторов 6 и 15 равны нулю/(иит «1 1=ттинт й(0) = 0/ К э

4 и 5 разомкнуты и ключ 18 замкнут, выход триггера 11 имеет запретный уровень 0 . В начале интервала интегрирования тактовый генератор 19 замыкает ключи 3 и 5 и размыкает ключ 18. Входные напряжения делимогоIJ (ь ) и дели- 40 теля )а (Ц поданы на входы 1 и 2 соответственно. Начинается интервал интегриро»вания Т .

В течение интервала Т первым ин45 тегратором 6 интегрируют напряжение делимого,(4) за время Т в соответствии с выражением:

Ч;

R I, L,(t.)ét=R,,З r, 05 4

Заряд первого интегратора в конце интервала интегрирования Т,,у

Минтz = "

В то же время Т, интегрируют напряжение целителя U (f. ) с помощью второго интегратора 15 в соответствии с выражением: где С,, — емкость интегрирующего конденсатора второго интегратора.

3а интервал Тт на BblKoaax интеграторов 6 и 15 будут напряжения инт-, (t ) и иит (-) °

В момент t= t,, т. е. в конце интегрирования, тактовый генератор 19 подает импульс сброса на вхоц индикатор ного блока 14, разомкнет ключи 3 и 5 и поцает на вход триггера 11 сигнал цикла компенсации. На выходе триггера

11 появляется разрешающий уровень 1 который замыкает ключ 4 На втором Вхо» де первого интегратора 6. Импульсы

Ут (4) генератора 13 стабильной частоты через элемент И поступают в индикаторный блок 14. Компенсацию заряда первого интегратора 6 производят выходным напряжениемЦ„„п„-(I) =UffHT L lвтсporo интегратора 15 до конца интервала компенсации Тк

Ток компенсации

U,t где <(t. ) = „- ток заряда первого инк1 тегра тора;

У . - среднее значение тока заряда первого интегратора;

R> - входной масштабный резистор первого интегратора.

Заряд компенсации

q=z г=-- —, .т, к

R 8

В конце интервала компенсации выходное напряжение первого интегратора унт i (tz ) О.Иэ равенства зарядов „ц,у*

Ц согласно выражениям(1) и(2) интервал компенсации з, „, ii il. sksi: 1 4

Rib, ° гце К= — L > R - коэффициент пропорК циональности

U, — среднее значение напряжения делимого;

V — срецнее значение напряжения-цели геля.

В конце интервала компенсации (при

U«, (tg) = 0) срабатывает компаратор

10, который переводит триггер 11 в начальное состояние. На выхоце триггера вырабатывается сигнал логического нуля, который поступает на вход элемента

И и закрывает его. Сигнал с выхода триггера ll поступает на вход ключа 4 и размыкает его, а также постугает на вход тактового генератора 19, Сигнал с выхода тактового генератора 19 замыкает ключ 18 и aoaapaulaer второй интегратор в начальное состояние.

В течение интервала компенсации измеряют время компенсации Т, заполняя его импульсами постоянной частоты

lJ - (t. ), Время компенсации Ч„„пропорциональное отношению напряжений —, U не зависит от длительности интервала интегрирования. Обеспечена возможность деления двух изменяющихся напряжений, усредняя их значения в течение интервала интегрирования.

С целью получения аналогового выхода на выход интервала 20 включают усредняющее измерительное устройство.

Формула изобретения

Делительиое устройство, содержащее первый ключ, первый вхоц которого яв50505 6 ляется входом делимого устройства, вт<ъ рой ключ, первый вход которого является вхоцом делителя устройства, первый интегратор, первый вхоц которого поцключен к выходу первого ключа, компаратор, один вход которого подключен к выходу интегратора, а другой вхоц — к шине нулевого потенциала, триггер, вхоц которого подключен к выходу компарато10 ра, элемент И, первый вход которого поцключен к выхоцу триггера, генератор импульсов станцартной частоты, выход которого подключен ко второму входу элемента И, выход которого подключен ко входу цифрового индикаторного блока, генератор тактовых импульсов, выходы которого подключены к управляющим вхоl1aM всех ключей, элемента И и цифрового индикаторного блока, о т л и ч а ющ е е с я тем, что, с целью повышения точности деления, путем исключения зависимости выходного сигнала от интервала интегрирования, оно содержит второй интегратор, в обратную связь которого

25 включен ключ сброса, вхоц которого под ключен к выходу третьего ключа, третий ключ, первый вход которого поцключен к выходу второго интегратора, а выход— ко второму входу первого интегратора.

30 Источники информации, принятые во внимание при экспертизе

1. Прянишников В. А. Интегрирующие цифровые вольтметры постоянного тока, Л.: Энергия, 1976, с, 46-49, 2. Жук Л. А., Лучук A. М., Скурицин В, П. Применение метоца поочередного интегрирования сигналов для построения множительнсь-целительных устройств комбинированного типа, Приборостроение, 40 т. Х1, . М 9, 1968, с. 53-54, рис. 1.

7 50505

Составитель О. Сапунова редактор Q, Стенина Техред О. Дегеза Корректор Г. Назарова

Заказ 4651/39 Тираж 751 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж35, Раушская наб., д. 4/5 филиал ППП Патент", г. Ужгород, ул, Проектная, 4