Устройство для моделирования статических характеристик логических элементов триггерного типа

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (61) Дополнительное к авт. свид-ву (22) Заявлено 050778 (21) 2638171/18-24 (51)М. КЛ.

3 с присоединением заявки Ио (23) Приоритет

С 7/25

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 230780.бюллетень М27

Дата опубликования описания 230780

РЗ) УДК 681. 333 (088. 8) (72) Авторы изобретения

Г.Я. Кердивара, В.П. Недельчук, С.В. Марин и В. Н. -Мурашев (71) Заявитель

Кишиневский политехнический институт им. С.Лазо (54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СТАТИЧЕСКИХ

ХАРАКТЕР ИСТИК ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

ТРИГГЕРНОГО ТИПА

Изобретение относитс я к вычислительной технике и машинному проекти. рованию и может быть использовано для анализа логических устройств.

Известно устройство для моделирования динамических характеристик логических элементов, содержащее задающие резисторы и управляемые источники (1) .

Недостаток этих устройств — слож- 1Î ность моделирования статических характеристик и невысокая точность.

Наиболее близким техническим решением является устройство для моделирования характеристик логических 15 элементов триггерного типа, содержащее источник опорного напряжения, задающие резисторы и два управляемых источника напряжений, например операционных усилителей с резисторами 20 в цепях обратной связи (2), Недостатки устройства — относительная низкая точность и необходимость больших затрат времени при обработке данных на цифровой вычис- 25 лительной машине (IQ3M).

Цель изобретения — повышение точности устройства.

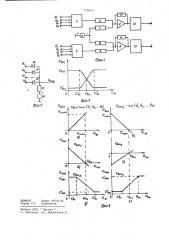

Укаэанная цель достигается тем, что в устройство для моделирования 30 статических характеристик логических элементов трнггерного типа, содержащее ис точняк опорного напряжения, задающие резисторы и операционные усилители, введены арктангенсные функциональные преобразователи и блоки выделения минимума, выходы которых соответственно через первый и второй задающие резисторы подключены ко входам первого и второго операционных усилителей соответственно,выходы которых соединены с входами соответствующих арктангенсных функциональных преобразователей, выходы которых являются выходами устройства, входы операционных усилителей подключены к одним выводам третьего и четвертого задающих резисторов, другие выводы которых соединены с выходом источника опорного напряжения, входы блоков выделения минимума являются соответственно прямыми и инверсными входами устройства, На фиг. 1 представлена структурная схема устройства; на фиг. 2 — схема блока выделения минимума; на фиг. 3 и фиг. 4 — зависимости напряжений в характерных узлах устройствa..

750513

Устройство содержит блоки выделения минимума 1, 2, на входы которых подаются прямые и инверсные входные сигналы, а выходы через два задающих резистора 3, 4 подсоединены ко входам операционных усилителей 5,6 и через два других задающих резистора 7 и 8 к источнику опорного напряжения 9.

Операционные усилители имеют в цепях обратной связи резисторы 10, 11, выходы операционных усилителей подсоединены ко входам арктангенсных функциональных преобразователей 12, 13, выходы которых являются выходами устройства °

Схема также содержит диоды 14, которые подсоединены ко входам (U«U2t Un) и к балластному резистору 15 и выхоДУ (U х 1) .Второй вывод балластного резистора 15 подсоединен к положительному полюсу источника опорного напряжения 16, отрицательный полюс которого эаземлен.

Аппроксимация исходной нелинейной статической характеристики (фиг. 3) на участке U x до U х осуществляется арктангенсной зависимостью по формуле

О ВЫ Х ВЬ1Х

u -u

-0 Р

Вых Вых 7

12,13

1- arch((hju „ ) (1)

3 где 10 i) IO

=u — — miп(u,u,...,u„) —, &мха Оя ц 1 2 " д

7 3 4, 1О

Р

= ООП вЂ” - и (() < uZ uП} - — °

Вых6 Оп

& К4

Зависимости изменения напряжений приведены на фиг. 4 а-е. Величийы напряо жений Uz, „и U 1„„(41èã. 3) соответствуют вычисленным значениям напряжений 1)вь1„1 1з функциональных преобразователей 12,13.

При достаточно небольшом N выражении в квадратных скобках приобретает значение либо нуль, либо два, в зависимости от знака Пвь1х q,ь i«> обеспечивается переход от уровня

1 О

U@ыхк Пвых и обРатно, Вариацией N можно добиться требуемой ширины зоны переключения ха1 о рактеристик от U>> до Uz„. Величина

N вычисляется по формуле (2)

Н = .4. tg (О 44-а}

ЗХ !Он

Входные источники напряжений задаются в соответствии с таблицей истинности работы данного логического элемента триггерного типа. Блоки 1, 2 (фиг. 1) являются эквивалентом многоэмиттерного транзистора. Значение электродвижущей силы (ЭДС) совместно с сопротивлениями R и R> резисторов 7 и 8 определяют значения U>„„ - напряжения переключения (фиг. 3 и фиг. 4).

В устройстве исключены перекрестные положительные обратные связи между базовыми логическими элементами в триггерах, а их значение учтено корректировкой законов изменения напряжений, U, усилителей 5,6 от протекающих через резисторы

10, 11 токов.

Потеря свойства запоминания устройством информации не сказывается,так как выходные напряжения на блоках

1, 2 (фиг. 1) задаются в соответствии с таблицей истинности работы данного логического элемента. Благодаря введенным блокам и связям между ними повышается точность.

Формула изобретения

Устройство для моделирования статических характеристик логических элементов триггерного типа, содержащее источник опорного напряжения, задающие резисторы и операционные усилители, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, в него введены арктангенсные функциональные преобразователи и блоки выделения минимума, выходы которых соответственно через первый и второй задающие резисторы подключены ко входам первого и второго операционных усилителей соответственно, выходы которых соединены с входами соответствующих арктангенсных функциональных преобразователей, выходы которых являются выходами устройства, входы операционных усилителей подключены к одним выводам третьего и четвертого задающих резисторов, другие выводы которых соединены с выходом источника опорного напряжения, входы блоков выделения минимума являются соответственно прямыми и инверсными входами устройства.

Источники информации, принятые во внимание при экспертизе

1. Кори Г., Корн Т. Электронные аналоговые и аналого-цифровые вычислительные машины, иэд.Мир, М., 1968, ч. 11, гл. 9.

2. Электроника, 1973, Р 26, с.63, рис. 2.

75051 3

Mg

Ф ц

Ив

Ф-—

ЦНИИПИ Заказ 4470/20

Тираж 751 Подписное

Филиал ППП Патент, r, Ужгород, ул, Проектная,4