Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ оп 750560 (61) Дополнительное к авт. санд-ву (5) ) М. Кл.

G 11 С 17100 (22) Заивлено03.1 1.77 (21) 2540117/18-24 с присоединением заявки М (23) Приоритет

Опубликовано 23.07.80. Бюллетень Л 27

Гооударстваииый комитет

Ila делам изобретений и открытий (53) УДК681.327.. 6 (088.8) Дата опубликования описания 25.07.80 (?2) Автор изобретения

М. М. Московкин (7l) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может использоваться в различных цифровых вычислительных системах.

Известны постоянные запоминаюшие устройства, содержашие регистр адреса, дешифратор адреса, блок формирователей адресного тока, накопитель чисел, блок усилителей считывания и регистр данных.

Накопитель чисел состоит иэ М сер10 дечников для хранения М-многоразрядных чисел. При прохождении тока по одной иэ адресных шин, наводятся сигналы в вьтходных шинах, праходяшКх через сердечники. Выходная шина служит для считыва;

15 ния кода единицы, если праходит через сердечник, и - кода нуля "0", если не проходит через него P)

Недостатком такого постоянного эапоминаюшего устройства (ПЗУ) является низкая помехозашишенность, вследствие трудностей, связанных с различием нулевого и единичного уровней сигналов, и пониженная надежность иэ-за неоптимальной упаковки чисел, что приводит к увеличению габаритно-весовых характеристик

ПЗУ.

Наиболее близким техническим решением к данному является постоянное эапоминаюшее устройство, содержащее рвгистр адреса, выходы которого через последовательно соединенные дешифратор адреса и блок формирователей адресных токов подключены ко входам накопителя, выходы которого соединены со входами блока усилителей считывания, и числовой регистр f2) Накопитель чисел состоит из М сердечников для формирования М-разрядных чисел, но при этом адресные проводники проходят через все сердечники, таким образом, что в выходных обмотках сердечников наводится отрицательный сигнал, что соответствует, например, считыванию кодовой единицы числа, или положительный сигнал, соответствуюший нулевой информации.

Недостатком такого постоянного запо= минающего устройства является понижен= ная надежность из-за неоптимальной упаковки чисел, что ведет к увеличению габаритноо-весовых характеристик устройства, снижению помехозащищенности.

Е елью изобретения является повышение надежности запоминающего устройства.

Это достигается тем, что в постоянном запоминающем устройстве, содержащем регистр адреса, выходы которого че- . рез последовательно соединенные дешифратор адреса и блок формирователей адресHblx токов подключены ко входам накопителя, выходы которого соединены со входами блока усилителей считывания, и числовой регистр, дополнительный блок усилителей считывания, буферный регистр и сумматор, входы которых через буферный регистр соединены с выходом блоков усилителей считывания, а выходы - со входами числового регистра.

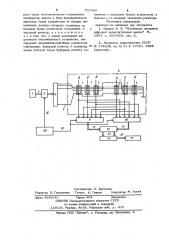

На чертеже представлена блок-схема постоянного запоминающего устройства.

Постоянное запом наюшее устройство состоит из регистра адреса 1, выходы 2 которого через дешифратор адреса 3 и блок формирователей адресных токов 4 присоединены к адресным шинам 5, поступающим на накопитель 6. Накопитель 6 содержит М сердечников 7 для хранения

М-многоразрядных чисел. Выходные обмотки 8 проходят через сердечники 7 и присоединяются поразрядно к входам первого и второго блоков усилителей считиванкя 9 и 10 соответственно, выходы 11 и 12 которых соединены с входами 13 сумматора 14 через буферный регистр 15, Выходы 16 сумматора 14 присоединены к выходам числового регистра 17, выходы 18 и 19 местного блока управл"-"íèÿ

20 присоединены соответственно к дешифратору адреса 3 и блоку усилителей счи-, тывания 9,10.

Постоянное запоминающее устройство работает следующим образом.

Число, которое хранится в регистре адреса 1, передается в дешифратор адреса 3, а затем поступает на блок формирователей адресных токов 4 по сигналу "., выхода 18 местного блока управления 20, По одной адресной шине 5 проходит импульсный сигнал с блока формирователей адресных токов 4. Каждая адресная шина кодирует одно М-разрядное число, опрвдепяемое числом сердечников 7 в накопителе 6. В зависимости от того, как про0 ф ходит провод адресной шины " через сер-. дечник 7, в выходной обмотке 8 наводится отрицательный или положительный сигнал. Б данном устройстве применена но= вая упаковка чисел, связанная с тем, что в накопителе чисел 6 помещаются двоичные числа с наименьшими арифметическими весами, то есть двоичное число с коэффициентами 0" и 1" представляется в виде: (М

К=.Y„a,2. "-,7 а. 2."

5=1

Например, двоичное число

К=О, 1 3 0 10 1 1 1 1 буд ет пр едставл ено с минимальным арифметическим весом как:

К=-+1,000 000 000 0,001 010 000

Число с минимальным арифметическим весом — это число с минимальным количеством не нулевых членов и имеет единственное представление для двоичных чисел. Сигнал с выходной обмотки 8 сердечника 7 поступает на усилители блоков усилителей считывания 9 и 10, а по командному сигналу с выхода 17 местного блока управления 18 поступает на установочные входы буферного регистра 15.

Причем, первая половина буферного регистра 1 5 устанавливается в положение, соответствующее первому числу, то есть

М а 2, ", а вторая половина

1. буферного регистра 15 устанавливается в положение, coQTBBTcTBóþøåå второму числу д 2. . Первое и второе числа 5 с буферного регистра 15 поступают на в.ходы 13 сумматора 14, где происходит их сложение, например, в дополнительном коде. При этом получается число с весовыми ксх ффициентами "0 и 1", то есть число "К", которое фиксируется в числовом регистре 17.

Предварительное, преобразование двоичных чисел с весовыми коэффициентами

"1 и «О" в числе с минимальными арифметическими весами, то есть двоичные числа с коэффициентами +1 и "-1", позволяет сократить число прошивочных проводов через .сердечники, а это приводит к уменьшению типоразмера сердечника и физического объема ПЗУ, а также увеличению помехозащищенности; повышению надежности.

Формула изобр ет ения

Постоянное запоминающее устройство, содержащее регистр адреса, выходы кото750560

Г н z в

g г l

Составитель Л. Амусьева

Редактор B. Голышкина Техред К. Гаврон Корректор М. Коста

Заказ 4658/40 Тираж 662 Подписное

UHHHHH Государственного комитета СССР по делам изобретений н открьггий

113035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 рого черю последовательно соединенные дешифратор адреса и блок формирователей адресных токов подключены ко входам накопнтвля, выходы которого соединены со входами блока усилителей считывания, и числовой регистр, о т л н ч а ю щ ее с я тем, что, с целью повышения надежности запоминающего устройства, оно содержит дополнительный блок усилителей считывания, буферный регистр н сумматор, 1О входы которых через буферный регистр соединены с выходами блоков уснлнтелей, а выходы — со входами чнслового, регистра.

Источники информацнн,, принятые во внимание прн экспертизе

l. Барднж B. B, Магнитные элементы цифровых вычислительных машин. М., 1967, с. 200-202, рис. 2.

2. Авторское свидетельство СССР № 174838, кл. G 11 С 17/00, 1965 (прототип) .