Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советск их

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<» 750561 (6l ) Дополнительное к авт. саид-ву— (22) Заявлено 14 03.78 (21) 2590420/18-24 с присоединением заявки.%(23) Приоритет

Опубликовано 23.07.80. Бюллетень № 27

3 (51) Ы. Кл.

G 11 С 17/00

Гасударственный комитет

СССР по делам иаабретеиий и открытий (53) УД К 628.327.. 6 (088.8) Дата опубликования описания 25.07.80

П. И. Платонов, B. И. Скорубцев, В. И. Конон и С. В. Кузнецов (72) Авторы изобретения (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Изобретение относится к вычислителт ной технике и может быть использовано для построения устройств хранения дискретной информации.

Известны постоянные запоминающие

5 устройства для хранения дискретной информации, состоящие из дешифратора адреса, выходы которого подключены ко входу накопителя и шифратора, входы которого подключены к выходу накопителя(Я.10

Такие постоянные запоминающие устройства имеют большое количество оборудования ввиду оГромного числа запоминающих элементов в накопителе и малую информационную емкость.

Наиболее блирким по технической сущности к предлагаемому является запоминающее устройство, имеющее дешифратор адреса, выходы которого через первую группу элементов ИЛИ соединены с соответствующими входами накопителя, вторую группу элементов ИЛИ, входы которых подключетсы к выходам накопителя, а выходы через усилители считывания - к соответствующим входам сумматора(аД

В сумматоре этого постоянного запоминающего устройства происходит формирование требуемых кодов чисел путем сложения нескольких кодов чисел, выбратеных из различных частей накопителя по заданному адресу.

Такое постоянное запоминающее устройство имеет большое количество оборудования, в особенности запоминающкх элементов в накопителе, и невысокое быстродействие из-за наличия в устройс1 ве сумматора.

Целью изобретения является повышение надежности и быстродействия постоянного запоминающего устройства.

Это достигается тем, что в постоянное запоминающее устройство, содержащее дешифрмор адреса, выходы которого соединены со входами соответствующи.х элементов ИЛИ первой группы, накопитель на триггерах и вторую группу элементов ИЛИ, введена группа двувходовых

3 75056 элементов И, нечетные входы которых соединены с выходами элементов ИЛИ пер-, вой группы, а четные входы соответственно с инверсными и прямыми выходами соответствующих триггеров накопи5 теля, а выходы элементов И попарно подключены ко входам элементов ИЛИ второй группы.

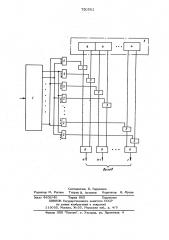

На чертеже дана структурная схема предлагаемого постоянного запоминающего устройства.

Устройство содержит дешифратор 1 адреса, первую группу элементов ИЛИ 2, группу двувходовых элементов И 3, трит геры 4 накопителя 5 и вторую группу эле-15 ментов ИЛИ 6. Выходы элементов ИЛИ 6 являются выходами постоянного запоминающего устройства.

Выходы дешифратора 1 адреса подключены ко входам первой группы соответсч вуюших элементов ИЛИ 2, количество которых равно удвоенному значению количеств& разрядов Выходного числа постоянно го запоминающего устройства, Выход каждого элемента ИЛИ 2 соеди- д нен с нечетным входом соответствующего элемента И 3. Четные входы элементов

И 3 соединены поочередно с инверсными и прямыми выходами соответствующих триггеров 4 накопителя 5. Количество зо элементов И 3 в группе равно 2 Г1, где

П -количество разрядов в коде выходного числа устройства. Выходы группы двувходовых элементов И 3 попарно подключены ко входам элементов ИЛИ 6 второй 3s группы, число которых равно

Устройство работает следующим образом.

При поступлении адреса числа на дешифратор 1 адреса на одном из его вы- 4g .ходов формируется сигнал, поступающий одновременно на несколько элементов

ИЛИ 2 первой группы. Триггеры 4, количество которых равно количеству разрядов 0 выходного числа устройства како- 4з пителя 5, всегда взведены после подачи питания. Сигналы с выходов элементов

ИЛИ 2 поступают на соответствующие элементы И 3, обеспечивая считывание с триггеров 4 накопителя 5 требуемого sp кода числа. С выходов элементов И 3 код числа через элементы ИЛИ 6 второй группы выдается из постоянного запоминающего устройства. Элементы ИЛИ 6

1 ф обеспечивают обьединение одновременных разрядов считываемых кодов чисел.

Время срабатывания t. сраб.пр. предллагаемого устройства определяется соот ношением

+21

cpaS,np А > иии и .

Предлагаемое устройство по сравнению с известным позволяет повысить быстродействие на величину t g t в предположении, что 1ус = „

Применение группы двувходовых элементов И выгодно отличает предлагаемое постоянное запоминающее устройство от прототипа, так как позволяет уменьшить количество оборудования, в особенности минающих элементов (триггеров) в накопителе (количество триггеров в накопителе равно количеству разрядов выходного числа), который позволяет выбрать

2% разных чисел, где rtl - количество разрядов в адресе числа, а также увеличить быстродействие устройства за счет того, что формирование кодов числа, в отличие от прототипа, осуществляется беэ применения сумматора, Формула изобр етения

Постоянное запоминающее устройство, содержащее дешифратор адреса, выходы которого соединены со входами соответствующих элементов ИЛИ первой группы, накопитель на триггерах и вторую группу элементов ИЛИ, о т л и ч а ю ш е е с я тем, что, с целью повышения надежности и быстродействия устройства, оно содержит группу двувходовых элементов И, нечетные входы которых соединены с выходами элементов ИЛИ первой группы, а четные входы — соответственно с инверсными и прямыми выходами соответствукьших триггеров накопителя, а выходы элементов И попарно подключены ко нходам элементов ИЛИ второй группы.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 371616, кл. Я 11 С 17/00, 1973, 2. Авторское свидеть ьство СССР № 490184, кл. Cj 11 С 17/00, 1975 (прототип) .

75056l

Bbixu>

Составитель В. Гордонова

Редактор М. Рогова Техред H. Асталош Корректор И. Муска

Заказ 4658/40 Тираж 662 Подписное

UHHHHH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4