Одноканальное устройство для асинхронного управления многофазным вентильным преобразователем

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик о П И < А Н И Е 750695

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву

Э (22) Заявлено 31.01.78 (21) 2576381/24-07 (5() M. (.п

Н 02 P 13/16 с присоединением заявки №Гооударстевииый комитет (23) Приоритет— ио делам изобретений и открытий

Опубл икова но 23.07.80. Бюллетень № 27

Дата опубликования описания 25.07.80 (53) УДК 621.316. .727 (088.8) Л. П. Деткин, A. Е. Рефес, Я. А. Тарс, 3, С. Иоспа, Б, Ф, Горошин, Т, Б, Кузьмина, В. B. Морозов и Е, И, Васин (72) Авторы изобретения (71) Заявитель (54) ОДНОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ АСИНХРОННОГО

УПРАВЛЕНИЯ МНОГОФАЗНЫМ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ

Изобретение относится к электротехнике в части статических вентильных преобразователей с асинхронными одноканальными системами управления.

Известно одноканальное устройство

5 для асинхронного управления многофазным вентильным преобразователем (1), содержащее интегратор, нуль-орган и распределитель импульсов, по упраляющим входам вентилей.

Однако устройство вносит статическую ошибку, зависящую от нагрузки и напряжения сети.

Известно также одноканальное устройство для асинхронного управления много-, фазным вентильным преобразователем (2), содержащее интегратор, ключ для сброса интегратора, нуль- орган, логический элемент "ИЛИ и распределитель импульсов по направляющим входа вентилей, Однако данное устройство не обе спечивает высокой точности регулирования и вносит статическую ошибку, зависящую от нагрузки и напряжения сети.

Наиболее близким техническим решением к рассматриваемому изобретению по техничесхой сущности и достигаемому результату является одноканальное устройство для асинхронного управления многофазным вентильным преобразователем (31, содержащее суммирующие резисторы, подключенные соответственно к источникам сигнала упраления, сигнала обратной связи и напряжения смещения, вторые концы резисторов объединены в общую точку, два интегратора с ключами сброса, выходы инте раторов включены через резисторы на вход нульоргана, на который также подключен резистор, другой конец которого соединен с источником напряжения смещения, распределитель импульсов, вход синхронизации которого подключен к источнику синхронизирующего напряжения, а выходы используются для подключения к управляющим электродам вентильного преобразователя и ко входам логическсьго элемента ИЛИ".

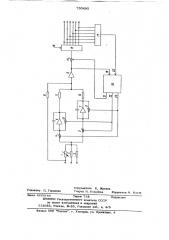

На чертеже изображена схема одноханального устройства для асинхронного управления многофазным вентильным пре50 образователем. Это устройство содержит суммирующие резисторы 1, 2, 3 интеграторов, входные ключи 4, 5, интеграторы 6, 7 с ключами 8, 9 сброса, суммирующие резисторы 10, 11 и «2 нул органа, нуль-орган 13, выходной ключ

14, распределитель 15, со входом 16 синхронизации логический элемент ИЛИ"

17, блок 18 логики, имеющий входы 19„

3 75069

Яедостатком данного устройства явля-. ется недостаточно высокая точность управц ения.

Целью данного изобретения является повьш(ение точности управления, 5

Поставленная цель достигается тем„ что одноканальное устройство для асинхронного управления многофааным вентильEEbnм преобразователем, содержащее суммирующие резисторы, подхдоченные соответственно к источникам сигнала уцравления,сигнала обратной связи и напряжения смещения, вторые концы резисторов объединены в общую точку, два HBтегратора с кпочами сброса, выходы интеграторов включены через резисторы на вход нуль-органа, на который также подключен резистор, другой конец которого соединен с источником напряжения смещения, распределитель импульсов, вход син-

20 хронизации которого подключен к источни-, ку синхронизирующего напряжения, а выхс ды используются для подключения к управляющим электродам вентильного преобразо25 вателя и ко входам логического элемента

" ИЛИ, снабжено блоком логики и тремя дополнительными ключами, два иа которых являются входными, а один выходным, причем общая точка суммирующих резисторов через входные ключи подключена ко входам ин-. теграторов, управляющий вход входного ключа первого интегратора соединен с управ1ыющим входом кгпоча сброса второго интегратора и с первым выходом блока логики, управляющий вход входного ключа второго интегратора соединен с управляющим входом первого интегратора и со вторым входом блока логики, выходной ключ одним концом соединен с выходом нуль-органа, а вторым концом со входом рас40 пределителя импульсов, управляющий вход выходного ключа соединен с третьим выхо. дом блока логики, выход нуль-органа соединен с первым входом блока логики, второй вход которого соединен с выходом логического элемента "ИЛИ", 5 ф

20 и выходы 21,22, 23, Устройство работает следующим образом, На вход 16 синхронизации распределителя подается напряжение синхронизации. На резистор 1 подается напряжение смещения, которое подается также через резистор 10 íà вход нуль-органа 13, Резистором 1 устанавливается требуемое начальное значение интервала между импульсами управления на выходах распределителя 15, На резистор 2 подается напряжение управления, на резистор 3 напряжения обратной связи.

Интегрирование сигнала ошибки и сигнала смещения на интервале между импульсами управления, необходимое для работы асинхронной системы управления, осуществляется за два полуинтервала.

На первом полуинтервале интегрирования блок 18 логики замыкает ключи 4, 9, а киочи 5, 8, 14 размыкает. При этом вход интегратора 6 подключен х суммирующим резисторам, а интегратор 7 сбрасывается HG нуль. По достижении выходным напряжением интегратора 6 порогового значения, определяемого соотношением резисторов 10 и 11, срабатывает нульорган 13 и подает сигнал на вход 19 блока 18 логики, Елок логики в этот момент изменяет состояние своих выходов 22 и 23 на противоположное, вследствие чего к почи 4, 9 размыкаются, а ключи 5, 8 замыкаются. Начинается второй полуинтервал интегрирования, Вход интегратора 6 отключается от суммирующих резисторов ключом 4, сигнал на выходе интегратора 8 сбрасывается ключом 8, сигнал на входе нуль-органа

13 пропада ет, на что блох 1 8 логики отвечает включением ключа 14, По достижеьпи выходным напряжением интегратора 7 порогового значения, определяемого соотношением резисторов 10 и 12, срабатывает нуль-орган 13 и вновь подает сигнал на блок 18 логики и через ключ 14 на распределитель 15. Распределитель в соответствии с очередностью включения фаз вентильного преобразователя и диапазоном угла управления соответствующей фазы, определяемым напряжением синхронизации, подает импульс в управляющую цепь одной из фаз вентильного преобразователя и одновременно на логический элемент 17, с выхода которого подается сигнал на блок

5 7

18 логики. В этот момент блок 18 лс гики размыкает ключи 5, 8„14, а ключи 4, 9 замыкает. Вновь начинается первый полуинтервал интегрирования, и далее процесс повторяется. Использование данного изобретения позволяет увеличить точность поддержания выходного параметра и снизить содержание субгармоник до значений 0,24. Улучшается распределение токов в параллельных мостах преобразователя, при этом упрошается настройка системы и снижаются затраты на настройку системы управления, так как не требуется устройство выравнивания токов, уменьшаются габариты уравнительного реактора. формула изобретения

Одноканальное устройство для асинхронного управления многофазным вентильным преобразователем, содержашее суммирующие резисторы, подключенные соответственно к источникам сигнала управления, сигнала обратной связи и напряжения смещения, вторые концы резисторов объединены в обшую точку, два интегратора с ключами сброса, выходы интеграторов включены через резисторы на вход нуль-органа, на который также подключен резистор, другой конец которого соединен с источником напряженич смешения, распределитель импульсов, вход синхронизации которого подктпочен к источнику синхронизируюшего напряжения, а выход используется для подключе50695 б ния к управшцошим электродам вентильного преобразователя и ко входам логического элемента ИЛИ", о т л и ч а ющ е е с я тем, что, с целью повышения точности управления, оно снабжено блоком логики и тремя дополнительными два На которых asmrw s axogными, а один выходным, причем общая точка суммнруюших резисторов через о входные ключи подключена ко входам интеграторов, управляющий вход входного ключа первого интегратора соединен с управляющим входом ключа сброса второго инте ратора и с первым выходом блока логики, управляюший вход входного ключа второго инте.ратора соединен с управляюшим входом первого интегратора и со вторым входом блошка логики, выходной ключ одним концом соединен с к выходом нуль-органа, а вторым концом со входом распределителя импульсов, управляющий вход выходного ключа соединен с третьим выходом блока логики, выход нуль-органа соединен с первым вхо25 д ом блока логики, второй вход которого соединен с выходом логического элемента

"ИЛИ", Источники информации, принятые во внимание при экспертизе зс 1. Писарев А.Л., Деткин Л.П. Управление тиристорными преобразователями, 14., "Энергия, 1975, с. 94-111, 2. Авторское свидетельство СССР

% 425297, кл. Н 02 P 13/16, 1970, 3s 3, Авторское свидетельство СССР !

4 440758, кл, Н 02 Р 13/16, 1971 (прототип).

Редактор П. Горькова

Составитель Е. Жданов

Техред Н. Ковалева Корректор М. Коста

Заказ 4668/44 Тираж 783 П од пнс ное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

13.3035, Москве, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент . v У ж го р о д, ул, Проектная, 4