Формирователь импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

< > 750710 (61) Дополнительное к авт. свид-ву (51)М. Кл. (22) Заявлено 210377 (21) 2463528/18-21 с присоединением заявки ¹

Н 03 К 5/01

Государственный комитет

СССР по делам изобретений и открытий

{23) Приоритет

Опубликовано 230780. Бюллетень № 27 (53) УДК 621. 373

{088.8) Дата опубликования описания 230780 (72) Авторы изобретения

В. A. Милошевский и A. A. Яковлев (71) Заявитель (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к радиоэлектронике и может применяться в устройствах для формирования импульсов с амплитудой, превышающей на- 5 пряжение источника питания.

Известны формирователи импульсов, содержащие и накопительных конденсаторов, диоды, ключевые транзисторы (1J . 10

Указанные формирователи недостаточно экономичны.

Известны формирователи, содержа- . щие входной транзистор и цепь умножения, сОстОящую из и пОследОвательнО соединенных ячеек, каждая из которых содержит транзистор, база которого через резистор соединена с шиной источника питания резистором, эмиттер через диод соединен с шиной источника питания, а через конденсатор — с коллектором транзистора предыдущей ячейки и с анодом диода, катод которого соединен с коллекторами входного и последнего транзисторов, 25 а через нагрузку — с эмиттером входного транзистора и общей шиной источника питания, обкладка конденсатора и анод диода первой ячейки соединены через резистор к шине источника пита- 0 ния, которая соединена с базовым резистором первой ячейки (2) .

Это устройство имеет значительные потери мощности.

Цель изобретения — уменьшение потерь мощности.

Для достижения указанной цели в устройстве, содержащем входной транзистор и цепь умножения, состоящую из и ячеек последовательно соединенных, каждая из которых содержит транзистор, база которого соединена с резистором, эмиттер через диод соединен с шиной источника питания, а через конденсатор — с коллектором транзистора предыдущей ячейки и с анодом диода, катод которого соединен с коллекторами входного и последнего транзисторов, а через нагрузку — с эмиттером входного транзистора и общей шиной источника питания, обкладка конденсатора и анод диода первой ячейки подсоединены через резистор к шине источника питания, которая соединена.с базовым резистором первой ячейки, базовый резистор каждой, кроме первой ячейки соединен с эмиттером транзистора предыдущей ячейки.

750710 цНИИПИ Эаказ 4670/45 .Рираж 995 Подписное

Филиал ППП Патент, г, Ужгород, ул ° Проектная,4

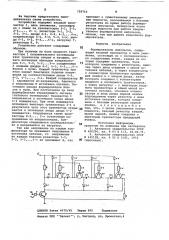

На чертеже представлена принципиальная схема устройства.

Устройство содержит входной транзистор 1, цепь умножения, состоящую из и ячеек на транзисторах 2-1, 2-2, 2-3,..., 2- и, резисторы 3-1, 3-2, 3-3, 3-и диоды 4-1, 4-2, 4-3,...4-п конденсаторы 5-1, 5-2, 5-3, 5=п, диоды.6-1, 6-2, 6-3,...6-п, нагрузку 7, резисторы 8, 9.

Устройство работает следующим образом.

При наличии на базе входного транзистора 1 положительного потенциала этот транзистор открыт и насыщен, отчего потенциал обкладок конденсаторов 5-1, 5-2, 5-3,...5-п соединенных с анодами диодов 6-1, 6-2, 6-3,...б-в близок к нулю. Каждый транзистор при этом закрыт благодаря падению напряжения на соответствующем диоде 4-1, 4-2, 4-3...i, 4-и. Каждый конденсатор

1 заряжается до напряжения, близкого к напряжению Е источника питания. IIoтенциал выхода формирователя близок к нулю. При поступлении на вход формирбвателя управляющего сигнала (нулевого потенциала} транзистор 1 закрывается и потенциал анода диода

6-1 повышается. При этом повышается потенциал эмиттера транзистора 2-1 в результате чего этот транзистор открывается и потенциал анода диода 6-2 повышается. Открываются также транзисторы 2-2,... 2-п остаточным напряжением на конденсаторах. Конденсаторы соединяются последовательно и разряжаются на нагрузку.

Так как напряжение на каждом кон денааторе не превышает напряжение Е источника питания, то напряжение на каждом базовом резисторе 5-1, 5-2, 5-3,...5-п не превышает Е, что приводит к существенному уменьшению мощности, рассеиваемой в базовых резисторах во время работы формирователя импульсов. Вследствие этого потери мощности при работе предлагаемого Формирователя импульсов, меньше, чем при работе известного формирователя.

Формула изобретения

t0

Формирователь импульсов,.содержащий входной транзистор и цепь умножения, состоящую из и последовательно соединенных ячеек, каждая из которых содержит транзистор, база которого соединена с резистором, эмиттер через диод соединен с шиной источника питания, а через конденсатор с коллектором транзистора предыдущей ячейки и с.анодом диода, катод

2О которого соединен с коллекторами входного и последнего транзисторов, а через нагрузку — с эмиттером входного транзистора и общей шиной источника питания, обкладка конденсатора и анод диода первой ячейки . подсоединены через резистор к шине источника питания, которая соединена с базовым резистором первой ячейки, отличающийся тем, что, с целью уменьшения потерь мощности, базовый резистор каждой, кроме первой, ячейки соединен с эмиттером транзистора предыдущей ячейки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 406296, кл. Н 03 К 1/2, 28.06.71.

2. Авторское свидетельство СССР

Р 445138, кл. Н 03 К 5/01, 1972

40 (прототип) .